# E-Infrastructures H2020- INFRAEDI-2018-2020

# INFRAEDI-01-2018: Pan-European High Performance Computing infrastructure and services (PRACE)

## PRACE-6IP

# **PRACE Sixth Implementation Phase Project**

**Grant Agreement Number: INFRAEDI-823767**

### **D8.5**

# Final report: Including performance results on (pre)Exascale systems

#### **Final**

Version: 0.7

Author(s): Alex Upton, ETH Zürich

Joost VandeVondele, ETH Zürich

Fabio Affinito, CINECA

Date: 30.06.2022

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: INFRAEDI-823767                                                                                       |                               |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

|               | Project Title: PRACE Sixth Implementation Phase Project                                                               |                               |  |

|               | Project Web Site: <a href="https://www.prace-ri.eu/about/ip-projects/">https://www.prace-ri.eu/about/ip-projects/</a> |                               |  |

|               | Deliverable ID: D8.5                                                                                                  |                               |  |

|               | Deliverable Nature: Report                                                                                            |                               |  |

|               | <b>Dissemination Level:</b>                                                                                           | Contractual Date of Delivery: |  |

|               | PU*                                                                                                                   | 30/06/2022                    |  |

|               |                                                                                                                       | Actual Date of Delivery:      |  |

|               |                                                                                                                       | 30/06/2022                    |  |

|               | EC Project Officer: Leo                                                                                               | onardo Flores Añover          |  |

<sup>\* -</sup> The dissemination level are indicated as follows: PU - Public, CO - Confidential, only for members of the consortium (including the Commission Services) CL - Classified, as referred to in Commission Decision 2005/444/EC.

### **Document Control Sheet**

| Document   | Title: Final report: Including performance results on (pre)Exascale systems   |  |  |

|------------|-------------------------------------------------------------------------------|--|--|

|            | ID: D8.5                                                                      |  |  |

|            | Version: 0.7 Status: Final                                                    |  |  |

|            | Available at: https://www.prace-ri.eu/about/ip-projects/                      |  |  |

|            | Software Tool: Microsoft Word 2016                                            |  |  |

|            | File(s): D8.5_v0.7_final.docx                                                 |  |  |

| Authorship | Written by:  Alex Upton, ETHZ Joost VandeVondele, ETHZ Fabio Affinito, CINECA |  |  |

|            |                                                                               |  |  |

| 1             |                                |

|---------------|--------------------------------|

| Contributors: | Fabio Affinito, CINECA         |

|               | Momme Allalen, LRZ             |

|               | Simone Bacchio, CaSToRC        |

|               | Vicenç Beltran, BSC            |

|               | Marco Bettiol, ETH Zürich      |

|               | Mauro Bianco, ETH Zürich       |

|               | John Biddiscombe, ETH Zürich   |

|               | Ricard Borrell, BSC            |

|               | Fabian Bösch, ETH Zürich       |

|               | David Brayford, LRZ            |

|               | John Brennan, ICHEC            |

|               | Dirk Brömmel, JUELICH          |

|               | Tomáš Brzobohatý, IT4I         |

|               | Mark Bull, EPCC                |

|               | Zahra Chitgar, JUELICH         |

|               | Laurent Chôné, CSC             |

|               | Olivier Coulaud, CENAERO       |

|               | Tilman Dannert, MPCDF          |

|               | Edoardo Di Napoli, JUELICH     |

|               | Myles Doyle, ICHEC             |

|               | Jacob Finkenrath, CaSToRC      |

|               | Christophe Geuzaine, ULIEGE    |

|               | Paul Gibbon, JUELICH           |

|               | Luc Giraud, INRIA              |

|               | Aleksander Grm, UL             |

|               | Kenneth Hanley, ICHEC          |

|               | Berk Hess, KTH                 |

|               | Koen Hillewaert, ULIEGE        |

|               | Victor Holanda, ETH Zürich     |

|               | Guillaume Houzeaux, BSC        |

|               | Luigi Iapichino, LRZ           |

|               | Alberto Invernizzi, ETH Zürich |

|               | Niclas Jansson, KTH            |

|               | Joe Jordan, KTH                |

|               | Prashanth Kanduri, ETH Zürich  |

|               | Sebastian Keller, ETH Zürich   |

|               | Leon Kos, UL                   |

|               | Marcin Krotkiewski, UiO        |

|               | Chiara Latini, CINECA          |

|               | Carlos Lopez, MPCDF            |

|               | Martti Louhivuori, CSC         |

|               | Georgi-os Markomanolis, CSC    |

|               | Michele Martone, LRZ           |

|               | Michal Merta, IT4I             |

|               | Teodor Nikolov, ETH Zürich     |

|               | Henrik Nortamo, CSC            |

|               | Lee O'Riordan, ICHEC           |

|               | Adam Peplinski, KTH            |

|               | Transi i Opinioni, ixiii       |

|              | Janes Povh, UL                 |

|--------------|--------------------------------|

|              | Lara Querciagrossa, CINECA     |

|              | Michel Rasquin, CENAERO        |

|              | Cristóbal Samaniego, BSC       |

|              | Mikael Simberg, ETH Zürich     |

|              | Matthieu Si-monin, INRIA       |

|              | Ujjwal Sinha, JUELICH          |

|              | Raffaele Solcà, ETH Zürich     |

|              | Thomas Toulorge, CENAERO       |

|              | Alex Upton, ETH Zürich         |

|              | Joost VandeVondele, ETH Zürich |

|              | Ivona Vasileska, UL            |

|              | Radim Vavřík, IT4I             |

|              | Jonathan Vincent, KTH          |

|              | Xinzhe Wu, JUELICH             |

|              | Shuhei Yamamoto, CaSToRC       |

|              | Artem Zhmurov, KTH             |

| Reviewed by: | Thomas Eickermann, JUELICH     |

|              | Pedro Alberto, UCoimbra        |

| Approved by: | MT/TB                          |

# **Document Status Sheet**

| Version | Date       | Status                | Comments                                                                                           |

|---------|------------|-----------------------|----------------------------------------------------------------------------------------------------|

| 0.1     | 04.10.2021 | 1 <sup>st</sup> Draft | 1 <sup>st</sup> version with input from all projects                                               |

| 0.2     | 19.10.2021 | 2 <sup>nd</sup> Draft | 2 <sup>nd</sup> version following internal review                                                  |

| 0.3     | 25.10.2021 | 3 <sup>rd</sup> Draft | Final 'pre-submission' version following internal review, will be updated with annexes in May 2022 |

| 0.4     | 10.06.2022 | 4 <sup>th</sup> Draft | Updated version with<br>annex following WP8<br>extension                                           |

| 0.5     | 21.06.2022 | 5 <sup>th</sup> Draft | Updated version following internal review                                                          |

| 0.6     | 22.06.2022 | 6 <sup>th</sup> Draft | Updated version                                                                                    |

| 0.7     | 30.06.2022 | 7 <sup>th</sup> Draft | Final version for EC                                                                               |

#### **Document Keywords**

| Keywords: | PRACE, HPC, Research Infrastructure, Exascale, Forward-looking |

|-----------|----------------------------------------------------------------|

|           | software solutions                                             |

|           |                                                                |

|           |                                                                |

#### Disclaimer

This deliverable has been prepared by the responsible work package of the project in accordance with the Consortium Agreement and the Grant Agreement n° INFRAEDI-823767. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the project and to the extent foreseen in such agreements. Please note that even though all participants to the project are members of PRACE aisbl, this deliverable has not been approved by the Council of PRACE aisbl and therefore does not emanate from it nor should it be considered to reflect PRACE aisbl's individual opinion.

#### **Copyright notices**

© 2022 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract EINFRA-730913 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as owned by the respective holders.

# **Table of Contents**

| Projec  | t and Deliverable Information Sheet                                    | 1      |

|---------|------------------------------------------------------------------------|--------|

| Docum   | nent Control Sheet                                                     | i      |

| Docum   | nent Status Sheet                                                      | iii    |

| Docum   | nent Keywords                                                          | iv     |

| List of | Figures                                                                | vii    |

| List of | Tables                                                                 | xi     |

| Refere  | ences and Applicable Documents                                         | xii    |

| List of | Acronyms and Abbreviations                                             | XV     |

| List of | Project Partner Acronyms                                               | xvii   |

| Execut  | tive Summary                                                           | 1      |

| 1 In    | troduction                                                             | 2      |

| 2 Co    | ompatibility of PRACE-6IP WP8 projects on leading European HPC system  | ıs3    |

| 3 Pi    | CKeX: Particle Kinetic codes for Exascale plasma simulation            | 7      |

| 3.1     | Introduction and summary                                               | 7      |

| 3.2     | Benchmarking results on pre-exascale/petascale/Tier-0 systems          | 8      |

| 3.3     | Interactions with stakeholders, users, outreach and publications       | 12     |

| 3.4     | Overall assessment of achievements and future developments             | 13     |

|         | oPHA: Modernisation of Plasma Physics Simulation Codes for Heterogeneo |        |

| 4.1     | Introduction and summary                                               |        |

| 4.2     | Benchmarking results on pre-exascale/petascale/Tier-0 systems          |        |

| 4.3     | Interactions with stakeholders, users, outreach and publications       |        |

| 4.4     | Overall assessment of achievements and future developments             |        |

| 5 Lo    | oSync: Synchronisation reducing programming techniques and runtime sup | port27 |

| 5.1     | Introduction and summary                                               | 27     |

| 5.2     | Benchmarking results on pre-exascale/petascale/Tier-0 systems          |        |

| 5.3     | Interactions with stakeholders, users, outreach and publications       | 32     |

| 5.4     | Overall assessment of achievements and future developments             | 33     |

| 6 FE    | EM/BEM based domain decomposition solvers                              | 35     |

| 6.1     | Introduction and summary                                               |        |

| 6.2     | Benchmarking results on pre-exascale/petascale/Tier-0 systems          |        |

| 6.3     | Interactions with stakeholders, users, outreach and publications       | 39     |

| 6.4  | Overall assessment of achievements and future developments                                           | 40    |

|------|------------------------------------------------------------------------------------------------------|-------|

| 7 P  | erformance portable linear algebra                                                                   | 41    |

| 7.1  | Introduction and summary                                                                             | 41    |

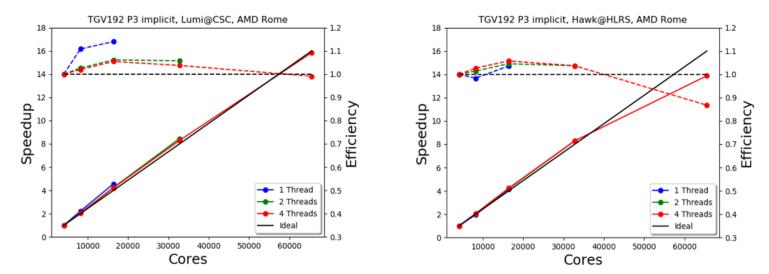

| 7.2  | Benchmarking results on pre-exascale/petascale/Tier-0 systems                                        | 42    |

| 7.3  | Interactions with stakeholders, users, outreach and publications                                     | 48    |

| 7.4  | Overall assessment of achievements and future developments                                           | 49    |

|      | yNcs: Linear Algebra, Krylov methods, and multi-grid API and library support secovery of new physics |       |

| 8.1  | Introduction and summary                                                                             | 51    |

| 8.2  | Benchmarking results on pre-exascale/petascale/Tier-0 systems                                        | 52    |

| 8.3  | Interactions with stakeholders, users, outreach and publications                                     | 58    |

| 8.4  | Overall assessment of achievements and future developments                                           | 60    |

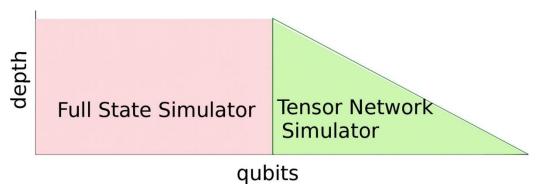

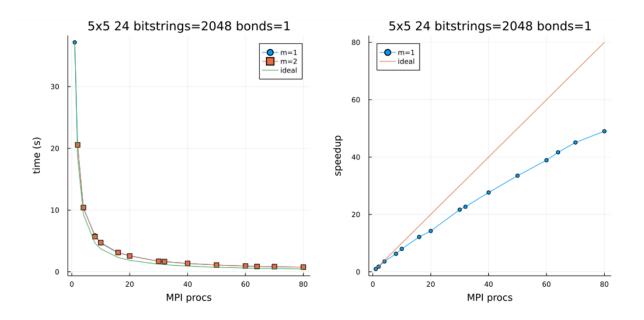

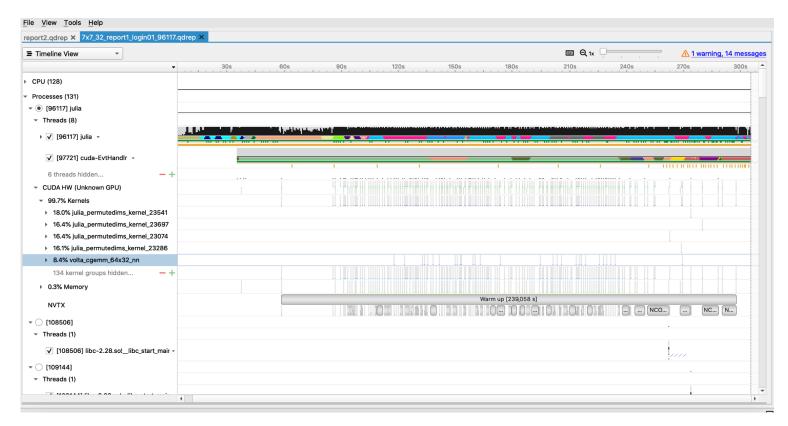

| 9 Q  | uantEx: Efficient Quantum Circuit Simulation on Exascale Systems                                     | 62    |

| 9.1  | Introduction and summary                                                                             | 62    |

| 9.2  | Benchmarking results on pre-exascale/petascale/Tier-0 systems                                        | 63    |

| 9.3  | Interactions with stakeholders, users, outreach and publications                                     | 67    |

| 9.4  | Overall assessment of achievements and future developments                                           | 68    |

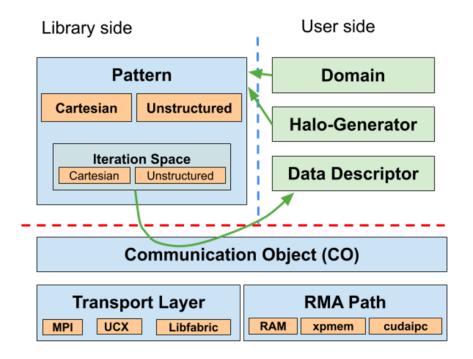

| 10   | GHEX: Generic Halo-Exchange for Exascale                                                             | 70    |

| 10.1 | Introduction and summary                                                                             | 70    |

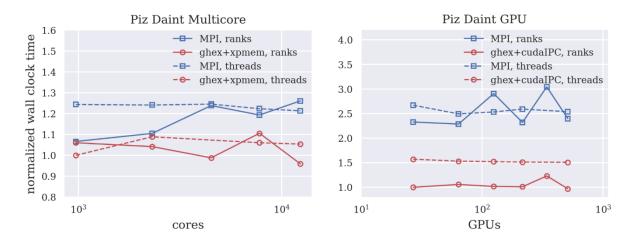

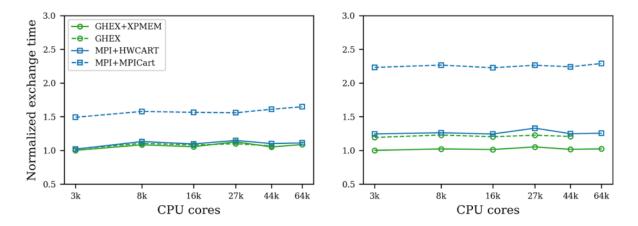

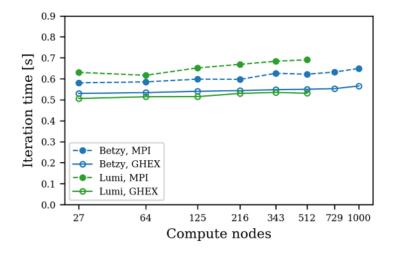

| 10.2 | Benchmarking results on pre-exascale/petascale/Tier-0 systems                                        | 72    |

| 10.3 | Interactions with stakeholders, users, outreach and publications                                     | 77    |

| 10.4 | Overall assessment of achievements and future developments                                           | 79    |

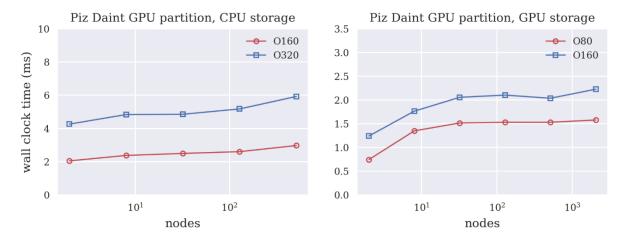

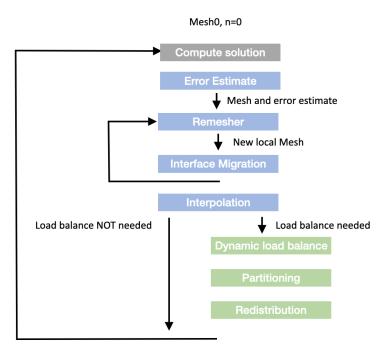

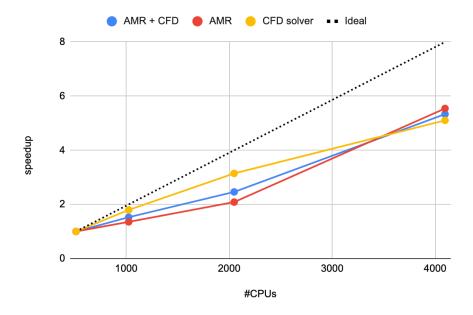

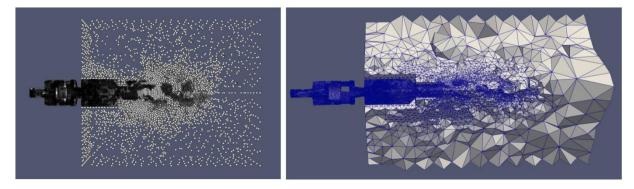

| 11   | ParSec: Parallel Adaptive Refinement for Simulations on Exascale Computers                           | 81    |

| 11.1 | Introduction and summary                                                                             | 81    |

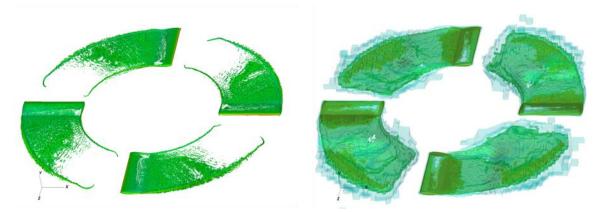

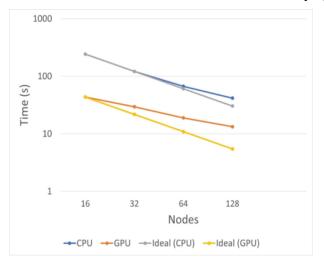

| 11.2 | Benchmarking results on pre-exascale/petascale/Tier-0 systems                                        | 82    |

| 11.3 | Interactions with stakeholders, users, outreach and publications                                     | 87    |

| 11.4 | Overall assessment of achievements and future developments                                           | 89    |

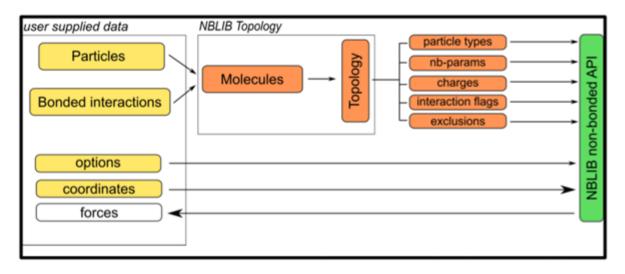

| 12   | NB-LIB: Performance portable library for N-body force calculations at the Exast 91                   | scale |

| 12.1 | Introduction and summary                                                                             | 91    |

| 12.2 | Benchmarking results on pre-exascale/petascale/Tier-0 systems                                        | 92    |

| 12.3 | Interactions with stakeholders, users, outreach and publications                                     | 95    |

| 12.4 | Overall assessment of achievements and future developments                                           | 97    |

| 13   | Conclusions                                                                                          | 99    |

| Annex A: Benchmarking and performance results obtained on leading HPC systems duri WP8 extension1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

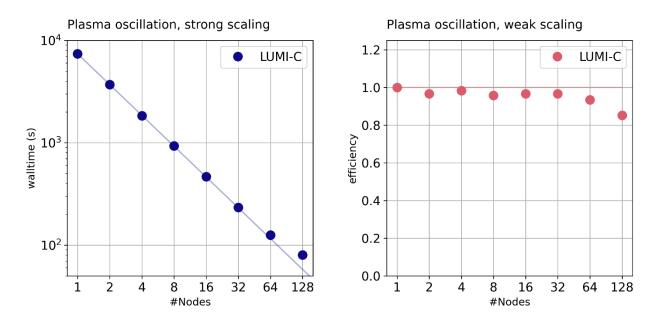

| A.1 PiCKeX: Particle Kinetic codes for Exascale plasma simulation1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101                   |

| A.2 MoPHA: Modernisation of Plasma Physics Simulation Codes for Heterogeneous Exascale Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103                   |

| A.3 Performance portable linear algebra1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105                   |

| A.4 LyNcs: Linear Algebra, Krylov methods, and multi-grid API and library support for the discovery of new physics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

| A.5 QuantEx: Efficient Quantum Circuit Simulation on Exascale Systems1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110                   |

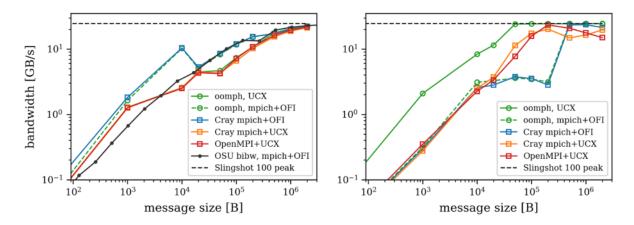

| A.6 GHEX: Generic Halo-Exchange for Exascale1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113                   |

| A.7 ParSec: Parallel Adaptive Refinement for Simulations on Exascale Computers1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |

| A.8 NB-LIB: Performance portable library for N-body force calculations at the Exascal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | le                    |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |

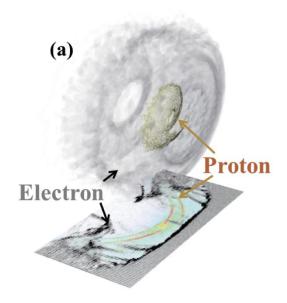

| Figure 1: Proton acceleration by circularly polarized, multi-petawatt laser pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | f<br>s                |

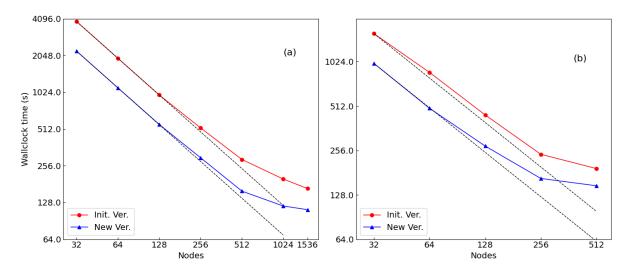

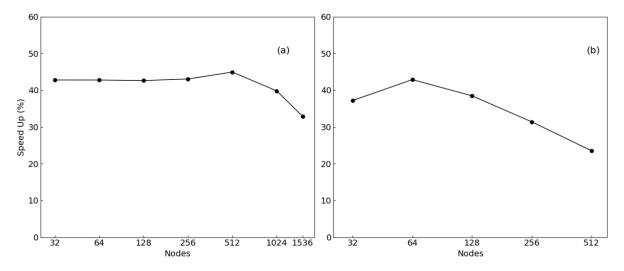

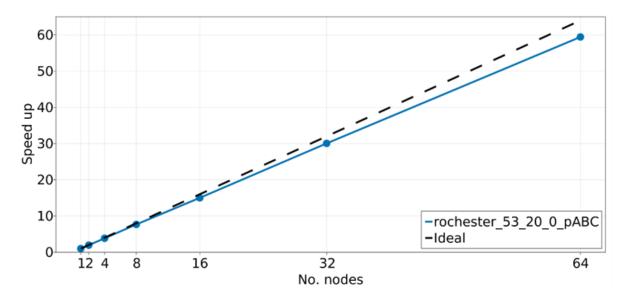

| Figure 3: (a) Speed-Up obtained by the new version of EPOCH over the initial version from 32 1536 nodes (1536 to 73728 CPU cores) on JUWELS. (b) Speed-Up obtained by the new version of EPOCH over the initial version from 32 to 512 nodes (4096 to 65536 CPU cores) on JURECA-DC.                                                                                                                                                                                                                                                                                                                                  | 2 to<br>on<br>.10     |

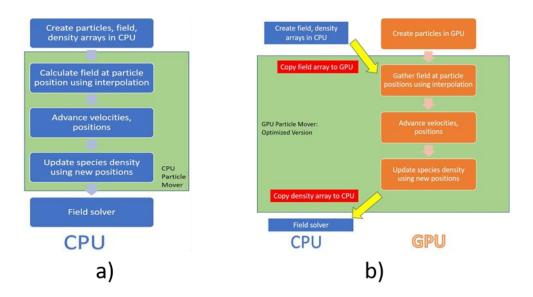

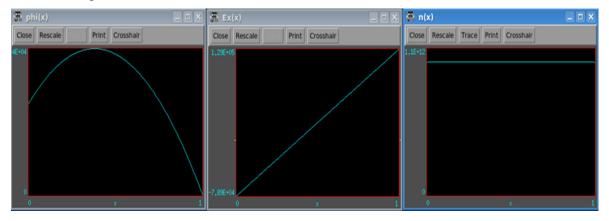

| Figure 4: a) CPU version b) GPU version of the particle mover algorithm in OOPD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |

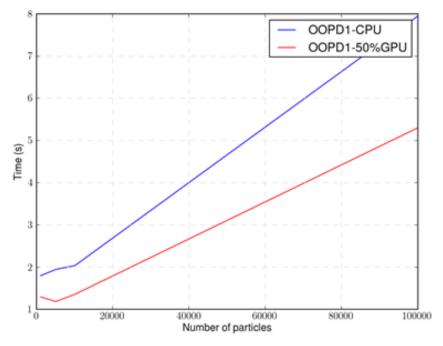

| Figure 6: Benchmark of the CPU and full particle mover GPU version of OOPD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .12                   |

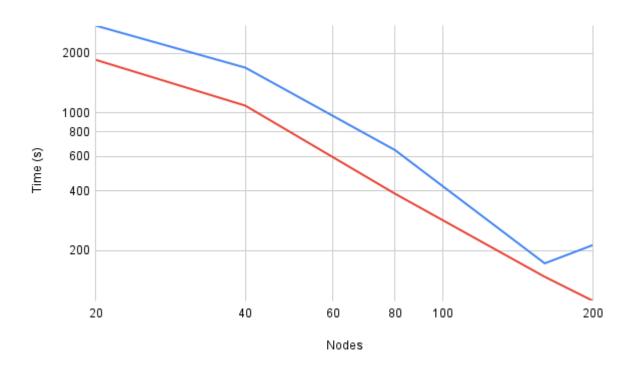

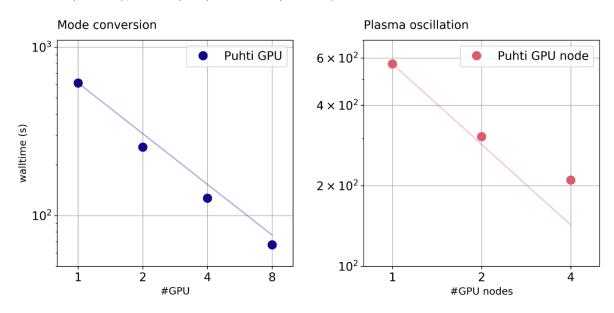

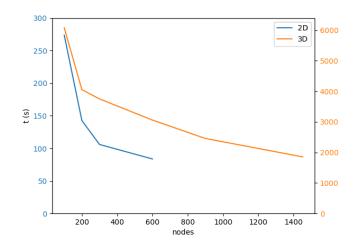

| Figure 8: Gantt diagram of the tasks performed during the computation of the right-hand side vector (rhs) required in the time-step and how they were distributed on the available hardware. Figure 9: Gantt diagram of the computation of the rhs. The new task-based parallelism allows to everlap the computation of entire terms (which is not possible in the MPI implementation) and now they can be computed concurrently in both the CPU (upper part) and GPU (lower part) Figure 10: Scalability study of Vlasiator on the Mahti supercomputer with total time (blue) and propagation time (red) in seconds. | .16<br>to<br>.17<br>l |

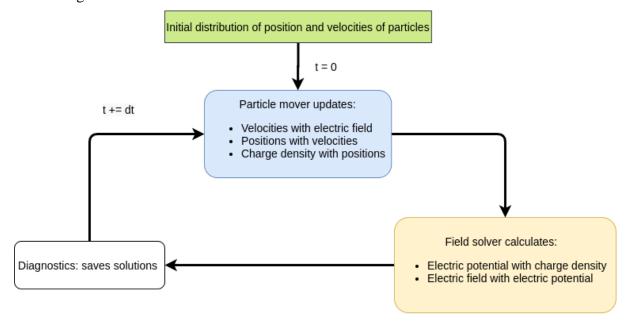

| Figure 12: SIMPIC workflow diagram. It shows the general algorithm flow of the PIC codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                    |

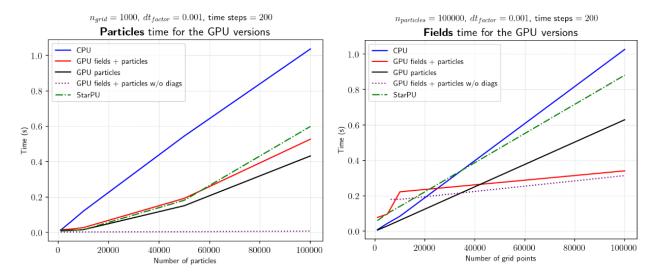

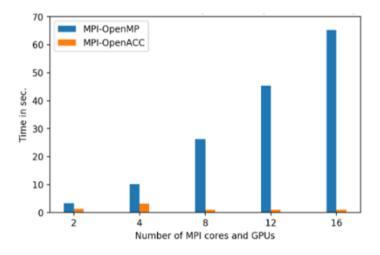

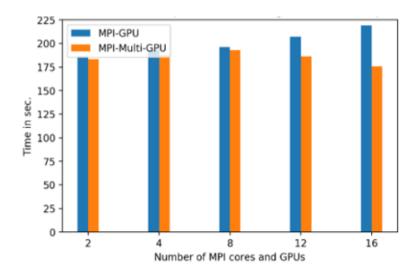

| Figure 13: Comparing performance of various accelerated versions of SIMPIC on the VIZ              |

|----------------------------------------------------------------------------------------------------|

| cluster. Left: Runtime Plot of the Particle Mover against number of particles. Right: Runtime plot |

| of field solver against number of cells                                                            |

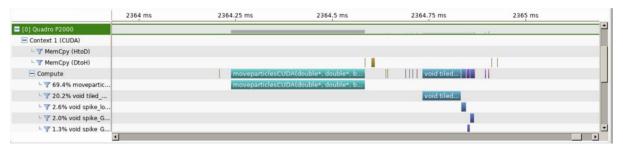

| Figure 14: Timeline of One Time Step of the full SIMPIC GPU version23                              |

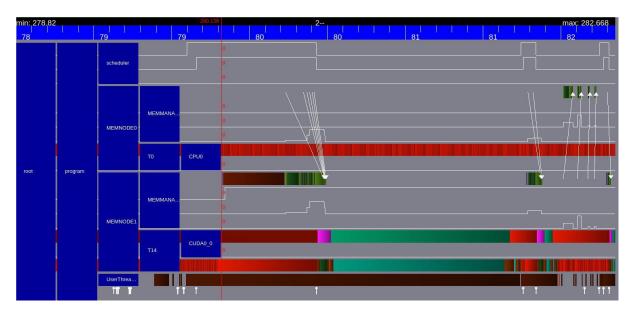

| Figure 15: Timeline for StarPU particle mover task24                                               |

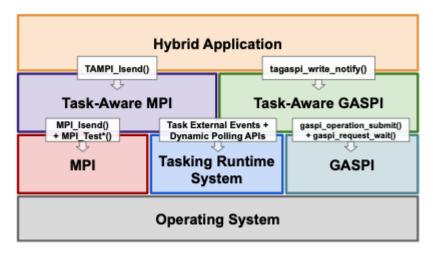

| Figure 16: Software architecture for hybrid applications using TAMPI and TAGASPI libraries .27     |

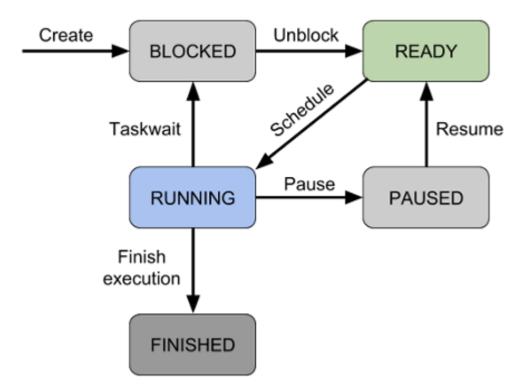

| Figure 17: State transition diagram for tasks (blocking mode)28                                    |

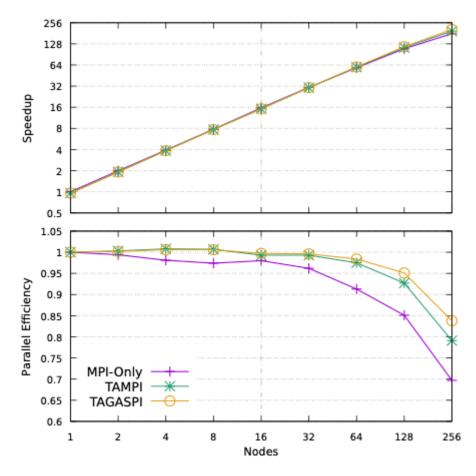

| Figure 18: Gauss-Seidel strong scaling with a 256Kx128K matrix and 1000 timesteps in MN4           |

| from 1 to 256 nodes. Due to the memory available in each node, we use a large input for the        |

| experiments from 16 to 256 nodes, and a 16x smaller input (64Kx32K matrix and 1000                 |

| timesteps) for the experiments from 1 to 8 nodes                                                   |

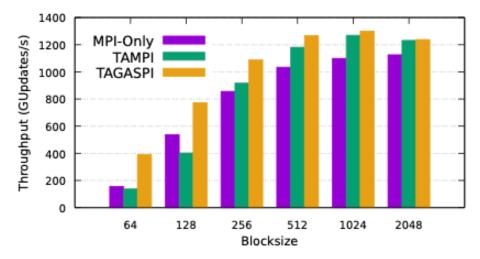

| Figure 19: Gauss-Seidel throughput varying the block size with a 128Kx128K matrix and 500          |

| timesteps in Marenostrum4 with 128 nodes                                                           |

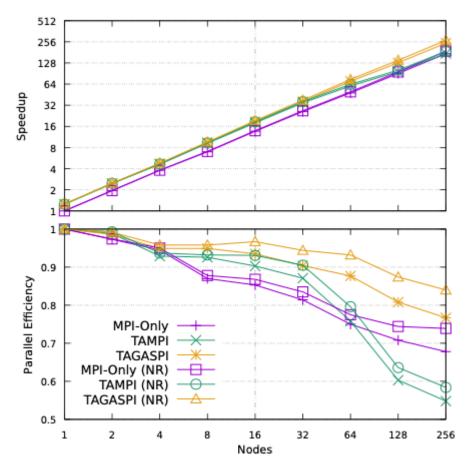

| Figure 20: miniAMR strong scaling in Marenostrum4 from 1 to 256 nodes. The lower shows the         |

| efficiency for both the total time and assuming a negligible refinement time (NR). Due to the      |

| memory available in each node, we use a large input for the experiments from 16 to 256 nodes,      |

| and a 16x smaller input for the experiments from 1 to 8 nodes                                      |

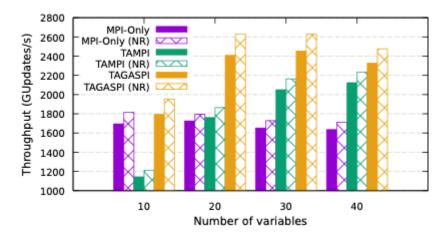

| Figure 21: miniAMR throughput varying the number of computed variables in Marenostrum4             |

| with 128 nodes. The figure shows the throughput for both the total time and assuming a             |

| negligible refinement time (NR). Notice that the vertical axis (throughput) starts at 1000         |

| GUpdates/s                                                                                         |

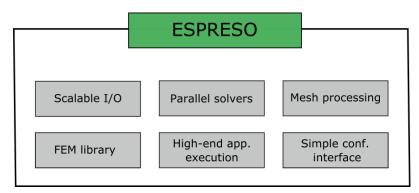

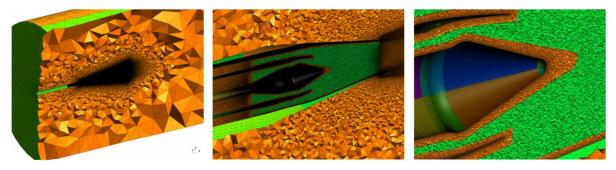

| Figure 22: Capabilities of the ESPRESO library                                                     |

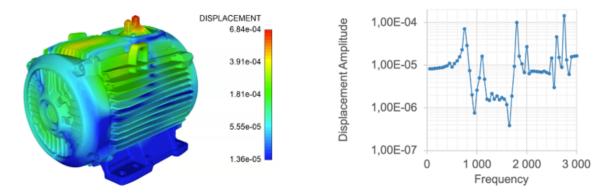

| Figure 23: Frequency response of the electric motor case computed using 450 nodes of the           |

| Salomon cluster at IT4Innovations in 714 s (15 million DOFs, 60 frequency samples)36               |

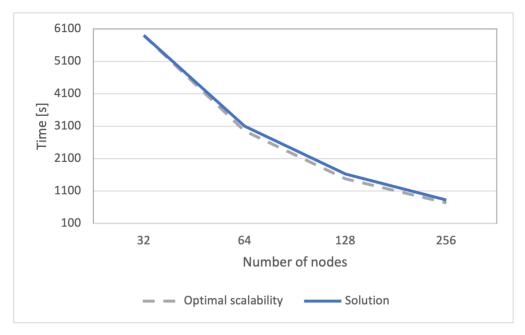

| Figure 24: Strong parallel scalability of the harmonic analysis solver on JUWELS Booster           |

| module                                                                                             |

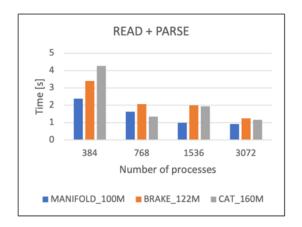

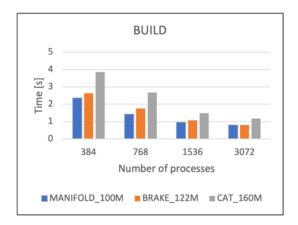

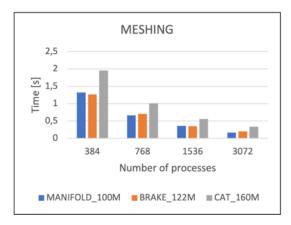

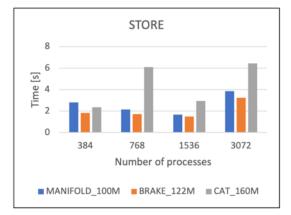

| Figure 25: Scalability of the individual phase of mesh manipulation on the JUWELS cluster          |

| module                                                                                             |

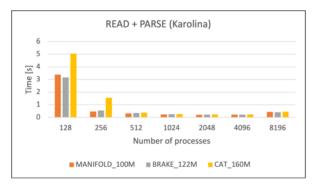

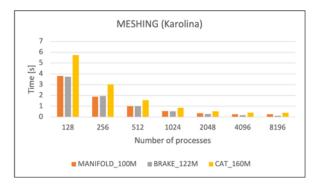

| Figure 26: Scalability of the READ + PARSE and MESHING phases on the Karolina system39             |

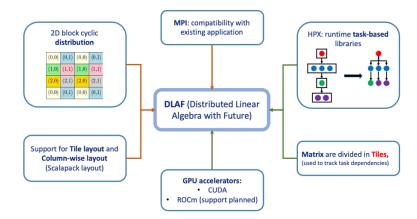

| Figure 27: Overview of DLA-Future41                                                                |

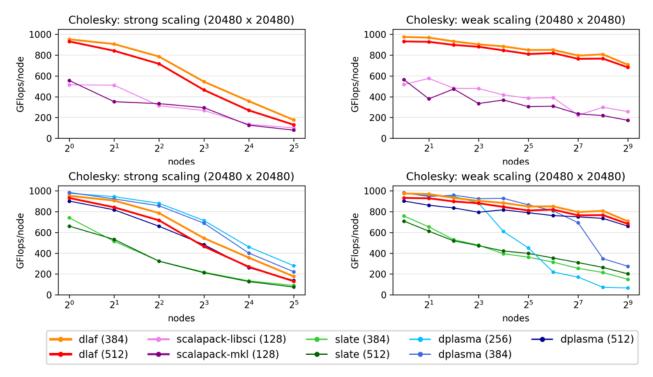

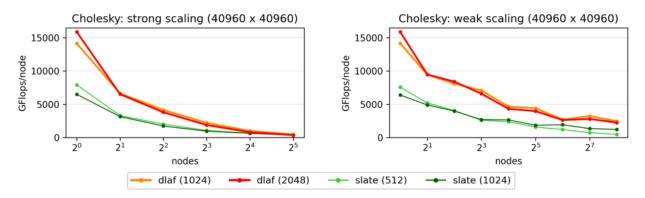

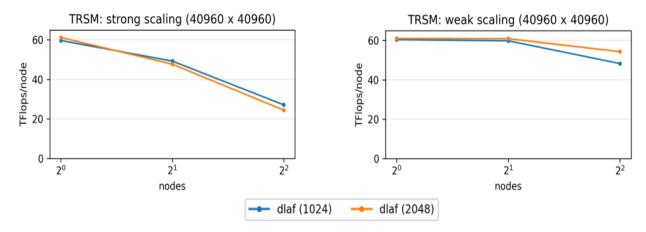

| Figure 28: Cholesky factorization on Daint MC. Left: we present the strong scaling for a matrix    |

| of size 20k. Right: we present the weak scaling for 400M elements per node (20k x 20k matrix       |

| for the run on a single node                                                                       |

| Figure 29: Cholesky factorization on Daint GPU. Left: we present the strong scaling for a matrix   |

| of size 20k. Right: we present the weak scaling for 400M elements per node (20k x 20k matrix       |

| for the run on a single node)                                                                      |

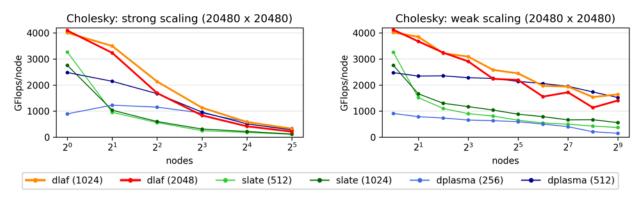

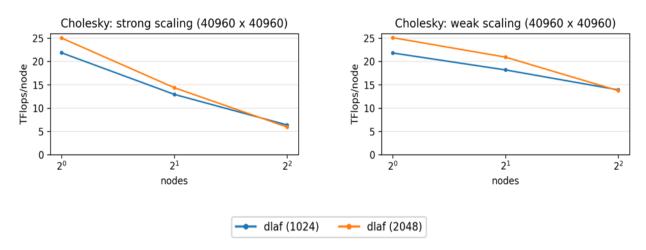

| Figure 30: Cholesky factorization on Marconi 100. Left: we present the strong scaling for a        |

| matrix of size 40k. Right: we present the weak scaling for 1.6G elements per node (40k x 40k       |

| matrix for the run on a single node)44                                                             |

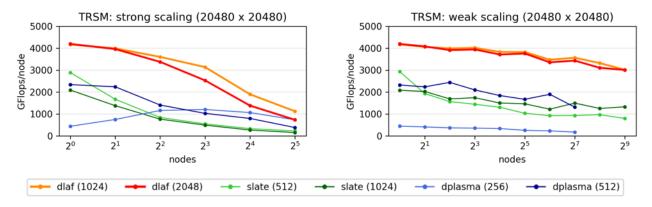

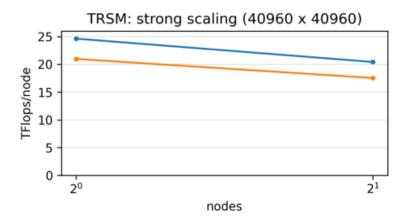

| Figure 31: Triangular solver on Daint GPU. Left: we present the strong scaling for a matrix of     |

| size 20k. Right: we present the weak scaling for 400M elements per node (20k x 20k matrix for      |

| the run on a single node)                                                                          |

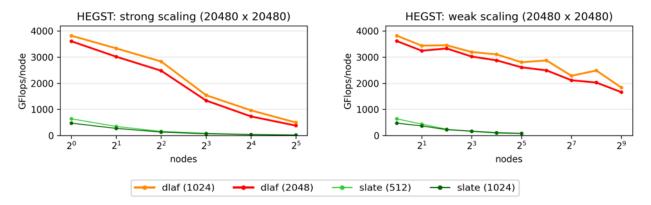

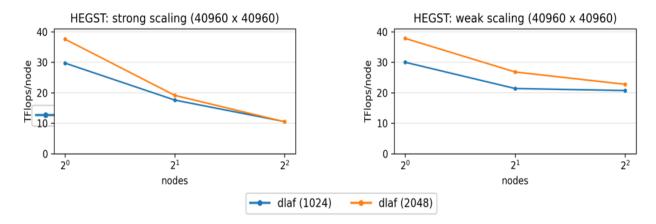

| Figure 32: Transformation from generalized to standard eigenproblem on Daint GPU. Left:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | we          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| present the strong scaling for a matrix of size 20k. Right: we present the weak scaling for 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00M         |

| elements per node (20k x 20k matrix for the run on a single node)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

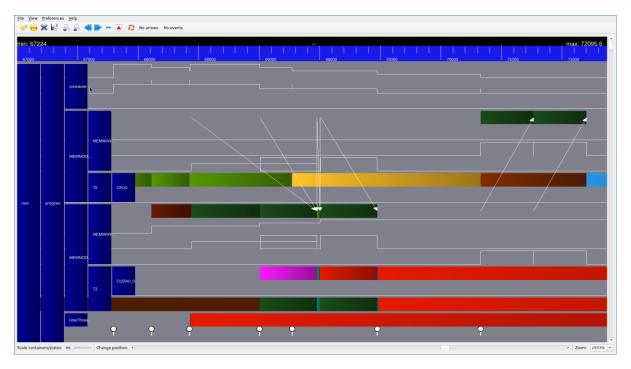

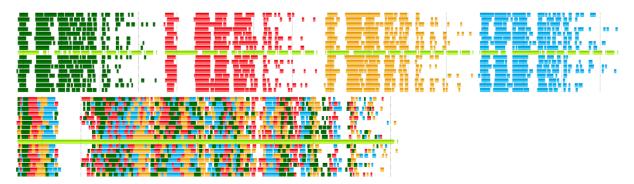

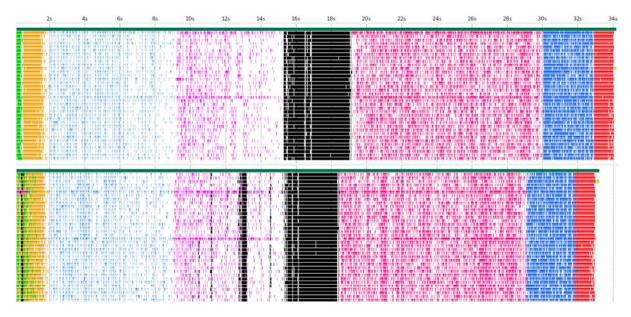

| Figure 33: Trace of 1 rank (over a total of 4) for the execution of 4 independent Cholesky                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| decompositions. The tasks of each factorization are depicted with a different color. (Due to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | a           |

| limitation of the trace utility, MPI communications cannot be identified, therefore they are a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| colored in light-green). The trace above shows the case in which after each factorization a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| synchronization point is added, the trace below shows the case in which the factorizations a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | re          |

| allowed to overlap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45          |

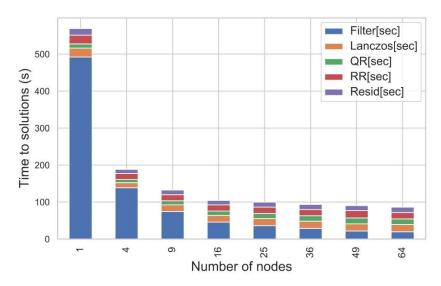

| Figure 34: Runtime of ChASE as a vertical stacked bar plot, including includes the fractions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| runtime of numerical modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

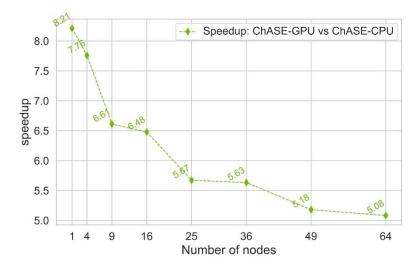

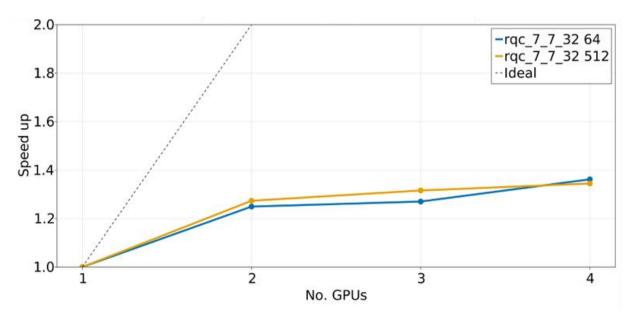

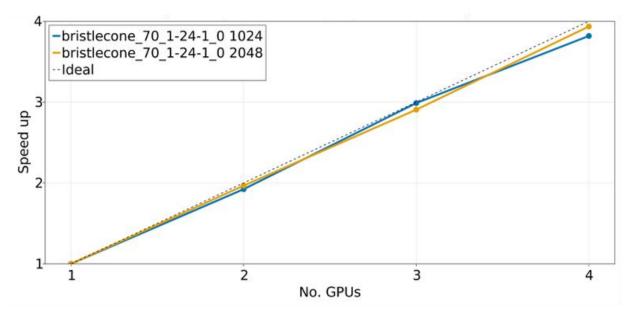

| Figure 35: Speedup of the ChASE GPU implementation compared with the ChASE CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 47          |

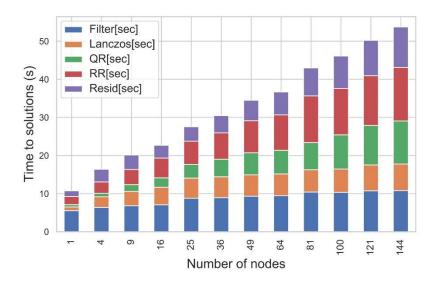

| Figure 36: ChASE weak scaling results across increasing number of nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

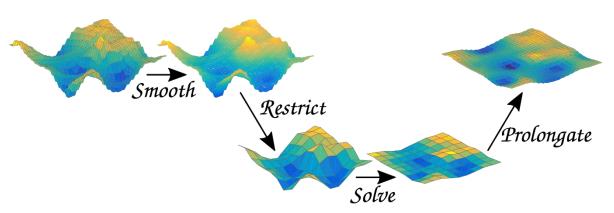

| Figure 37: Important algorithmic steps in the Krylov accelerated multigrid solver developed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| the LyNcs project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

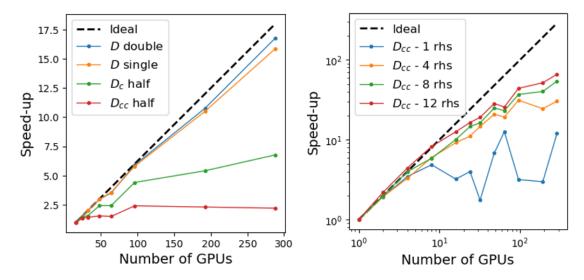

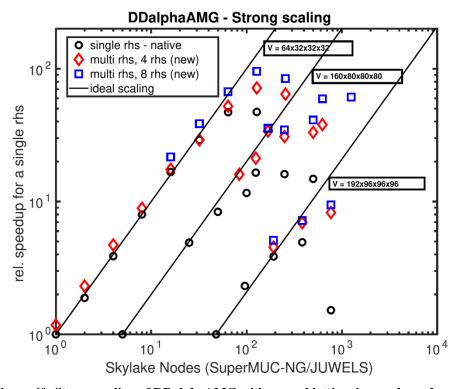

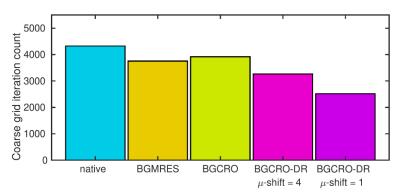

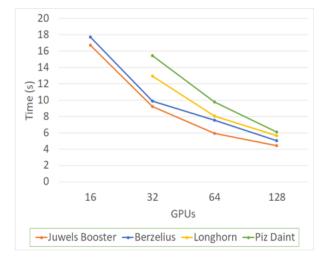

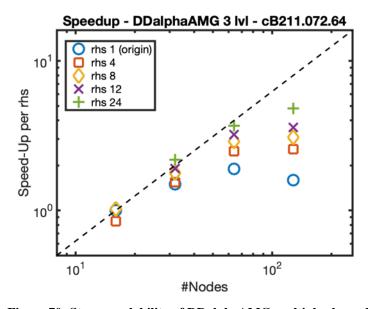

| Figure 38: (Left) Strong scaling study of the QUDA Dirac operators on the fine (D), intermediate the project of |             |

| (Dc) and coarsest (Dcc) grids for a lattice of size 963 x 128. (Right) Strong scaling of the co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| operator Dcc varying the number of right-hand sides (rhs) inverted at the same time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

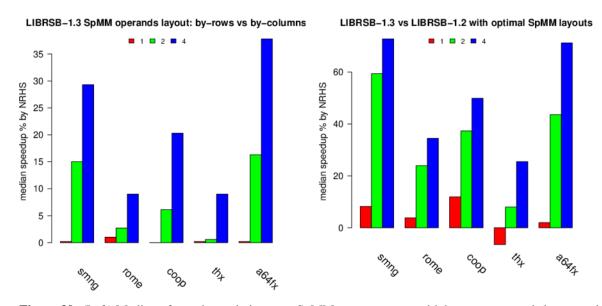

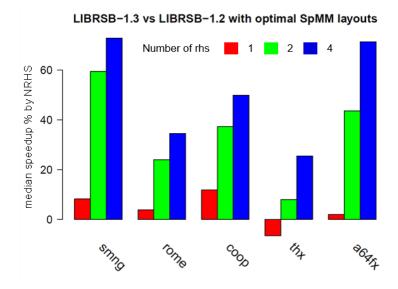

| Figure 39: (Left) Median of speedup ratio between SpMM measurements with by-rows ope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| layout and by-columns, on different machines and for different right hand sides count. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

| rows layout is recommended in LIBRSB-1.3 because of its better locality in the lower level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •           |