# E-Infrastructures H2020- INFRAEDI-2018-2020

# INFRAEDI-01-2018: Pan-European High Performance Computing infrastructure and services (PRACE)

## PRACE-6IP

# **PRACE Sixth Implementation Phase Project**

**Grant Agreement Number: INFRAEDI-823767**

### **D5.2**

# Worldwide HPC technology and market landscape

### **Final**

Version: 1.1

Author(s): Evangelia Athanasaki, GRNET; Norbert Meyer, PSNC; Andreas Johansson,

SNIC; Christelle Piechurski, GENCI; Dirk Pleiter, KTH; Ezhilmathi

Krishnasamy, U Luxembourg; Mikael Johansson, CSC

Date: 30.11.2021

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: INFRAEDI-823767                            |                     |  |

|---------------|------------------------------------------------------------|---------------------|--|

|               | Project Title: PRACE Sixth Implementation Phase Project    |                     |  |

|               | Project Web Site: http://www.prace-ri.eu/about/ip-projects |                     |  |

|               | Deliverable ID: D5.2                                       |                     |  |

|               | Deliverable Nature: Report                                 |                     |  |

|               | Dissemination Level: Contractual Date of Delivery:         |                     |  |

|               | PU* 30 / November / 2021                                   |                     |  |

|               | Actual Date of Delivery:                                   |                     |  |

|               | 30 / November / 2021                                       |                     |  |

|               | <b>EC Project Officer: Leo</b>                             | nardo Flores Añover |  |

$<sup>\</sup>ast$  - The dissemination level is indicated as follows: PU – Public, CO – Confidential, only for members of the consortium (including the Commission Services) CL – Classified, as referred to in Commission Decision 2005/444/EC.

# **Document Control Sheet**

|            | Title: Worldwide HPC technology and market landscape |                                       |  |  |

|------------|------------------------------------------------------|---------------------------------------|--|--|

| Document   | ID: D5.2                                             |                                       |  |  |

|            | Version: 1.1 Status: Final                           |                                       |  |  |

|            | Available at: http://                                | /www.prace-ri.eu/about/ip-projects    |  |  |

|            | Software Tool: Mic                                   | crosoft Word 2016                     |  |  |

|            | <b>File(s):</b> D5.2-v1.1.d                          | <b>File(s):</b> D5.2-v1.1.docx        |  |  |

|            | Written by:                                          | Andreas Johansson, SNIC;              |  |  |

| Authorship |                                                      | Christelle Piechurski, GENCI;         |  |  |

|            |                                                      | Dirk Pleiter, KTH;                    |  |  |

|            |                                                      | Ezhilmathi Krishnasamy, U Luxembourg; |  |  |

|            |                                                      | Evangelia Athanasaki, GRNET;          |  |  |

|            |                                                      | Mikael Johansson, CSC;                |  |  |

|            |                                                      | Norbert Meyer, PSNC                   |  |  |

|            | Contributors: Adem Tekin, UHEM;                      |                                       |  |  |

|            |                                                      | Ahmet Tuncer Durak, UHEM;             |  |  |

|            |                                                      | Damian Kaliszan, PSNC;                |  |  |

|            |                                                      | Dirk Pleiter, JSC-GCS;                |  |  |

|            |                                                      | Enver Özdemir, UHEM;                  |  |  |

|            |                                                      | Fethiye Aylin Sungur, U Luxembourg;   |  |  |

|            |                                                      | Filip Blicharczyk, PSNC;              |  |  |

|            |                                                      | Fredrik Robertsén, CSC;               |  |  |

|            |                                                      | Krzysztof Wadówka, PSNC;              |  |  |

|            |                                                      | Michael Mucciardi, BSC;               |  |  |

|            |                                                      | Michal Pilc, PSNC;                    |  |  |

|            |                                                      | Mirco Cestari, CINECA;                |  |  |

|            |                                                      | Philipp Gschwandtner, UIBK;           |  |  |

|            |                                                      | Sebastien Varrette, U Luxembourg      |  |  |

|            | Reviewed by:                                         | Walter Lioen, SURF;                   |  |  |

|            |                                                      | Veronica Teodor, JUELICH              |  |  |

|            | Approved by:                                         | MB/TB                                 |  |  |

# **Document Status Sheet**

| Version | Date             | Status                | Comments                                          |

|---------|------------------|-----------------------|---------------------------------------------------|

| 0.1     | 6/October/2021   | 1 <sup>st</sup> draft | Initial draft and setup of the document structure |

| 0.2     | 2/October/2021   | 2 <sup>nd</sup> draft | 2 <sup>nd</sup> compiled version                  |

|         |                  |                       | with additions to section 2                       |

| 0.3     | 27/October/2021  | 3 <sup>rd</sup> draft | Executive Summary and                             |

|         |                  |                       | additional updates                                |

| 0.4     | 3/November/2021  | 4 <sup>th</sup> draft | Ready for WP5 internal                            |

|         |                  |                       | review                                            |

| 0.5     | 8/November/2021  | 5 <sup>th</sup> draft | Draft with WP5 and PMO                            |

|         |                  |                       | internal review comments                          |

| 0.6     | 15/November/2021 | 6 <sup>th</sup> draft | Integration of reviewers'                         |

|         |                  |                       | comments                                          |

| 0.7     | 22/November/2021 | 7 <sup>th</sup> draft | Draft with 2nd review                             |

|         |                  |                       | comments                                          |

| 1.0     | 23/November/2021 | Final                 | Integration of reviewers'                         |

|         |                  |                       | comments. Addition of                             |

|         |                  |                       | technical reports as an                           |

|         |                  |                       | annex in pdf version                              |

| 1.1     | 30/November/2021 | Final                 | Final adjustments                                 |

ii

# **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure, Technology landscape, |  |

|------------------|------------------------------------------------------------|--|

|                  | Market landscape                                           |  |

#### **Disclaimer**

This deliverable has been prepared by the responsible work package of the project in accordance with the Consortium Agreement and the Grant Agreement n° INFRAEDI-823767. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the project and to the extent foreseen in such agreements. Please note that even though all participants to the project are members of PRACE aisbl, this deliverable has not been approved by the Council of PRACE aisbl and therefore does not emanate from it nor should it be considered to reflect PRACE aisbl's individual opinion.

#### **Copyright notices**

© 2021 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract INFRAEDI-823767 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as owned by the respective holders.

# **Table of Contents**

| P | roject        | and Deliverable Information Sheet                                                     | i   |

|---|---------------|---------------------------------------------------------------------------------------|-----|

| D | ocume         | ent Control Sheet                                                                     | i   |

| D | ocume         | ent Status Sheet                                                                      | ii  |

| D | ocume         | ent Keywords                                                                          | iii |

| L | ist of I      | Gigures                                                                               | v   |

| R | eferen        | ces and Applicable Documents                                                          | v   |

| L | ist of A      | Acronyms and Abbreviations                                                            | v   |

| L | ist of I      | Project Partner Acronyms                                                              | vi  |

| E | xecuti        | ve Summary                                                                            | 1   |

| 1 | Inti          | oduction                                                                              | 2   |

| 2 | Apj           | proach of technical reports                                                           | 4   |

|   | 2.1           | Selection of topics                                                                   | 4   |

|   | 2.2           | Organisation                                                                          | 4   |

|   | 2.3           | Review and Publication                                                                | 5   |

| 3 | Sun           | nmaries of Technical Reports                                                          | 6   |

|   | 3.1           | Edge Computing: An Overview of Framework and Applications                             | 6   |

|   | 3.2           | Data Management Services and Storage                                                  | 7   |

|   | 3.3<br>Soluti | State-of-the-Art and Trends for Computing and Interconnect Network ons for HPC and AI | 8   |

|   | 3.4           | Quantum Computing – A European Perspective                                            | 9   |

|   | 3.5           | Security in an Evolving European HPC Ecosystem                                        | 10  |

| 4 | Cor           | nclusion                                                                              | 12  |

| 5 | Anı           | nex 1: Technical reports                                                              | 13  |

## **List of Figures**

# References and Applicable Documents

- [1] https://prace-ri.eu/infrastructure-support/market-and-technology-watch/

- [2] <a href="https://prace-ri.eu/wp-content/uploads/Edge-Computing-An-Overview-of-Framework-and-Applications-1.pdf">https://prace-ri.eu/wp-content/uploads/Edge-Computing-An-Overview-of-Framework-and-Applications-1.pdf</a>

- [3] https://doi.org/10.5281/zenodo.5534072

- [4] <a href="https://prace-ri.eu/wp-content/uploads/Data-Management-Services-and-Storage-1.pdf">https://prace-ri.eu/wp-content/uploads/Data-Management-Services-and-Storage-1.pdf</a>

- [5] https://doi.org/10.5281/zenodo.5534064

- [6] <a href="https://prace-ri.eu/wp-content/uploads/State-of-the-Art-and-Trends-for-Computing-and-Interconnect-Network-Solutions-for-HPC-and-AI-1.pdf">https://prace-ri.eu/wp-content/uploads/State-of-the-Art-and-Trends-for-Computing-and-Interconnect-Network-Solutions-for-HPC-and-AI-1.pdf</a>

- [7] https://doi.org/10.5281/zenodo.5534080

- [8] <a href="https://prace-ri.eu/wp-content/uploads/TR-Quantum-Computing-A-European-Perspective.pdf">https://prace-ri.eu/wp-content/uploads/TR-Quantum-Computing-A-European-Perspective.pdf</a>

- [9] https://doi.org/10.5281/zenodo.5547408

- [10] <a href="https://prace-ri.eu/wp-content/uploads/Security-in-an-Evolving-European-HPC-Ecosystem.pdf">https://prace-ri.eu/wp-content/uploads/Security-in-an-Evolving-European-HPC-Ecosystem.pdf</a>

- [11] https://doi.org/10.5281/zenodo.5638456

# **List of Acronyms and Abbreviations**

ACID Atomicity, Consistency, Isolation, Durability

AI Artificial Intelligence

API Application Programming Interface

APU Accelerated Processing Unit CPU Central Processing Unit

DDR Double Data Rate

DL Deep Learning

DNS Domain Name System

DOI Digital Object Identifier

EC European Commission

EPI European Processor Initiative

EuroHPC JU The European High Performance Computing Joint Undertaking

EXDCI-2 European Extreme Data & Computing Initiative

FPGA Field Programmable Array

GPPs General Purpose Processors

GPU Graphics Processing Unit

HBM High Bandwidth Memory

HPC High Performance Computing

IDS Intrusion Detection Systems

INFRAG Infrastructure Advisory Group

I/O Input/Output IoT Internet of Things

MCM Multi-Chip Module ML Machine Learning

NVMe Non-Volatile Memory express POSIX Portable Operating System Interface

PRACE Partnership for Advanced Computing in Europe; Project Acronym

QC Quantum computing

RIAG Research & Innovation Advisory Group (RIAG)

SSH Secure Socket Shell SVE Scalable Vector Extension

WP Work Package

# **List of Project Partner Acronyms**

BADW-LRZ Leibniz-Rechenzentrum der Bayerischen Akademie der

Wissenschaften, Germany (3<sup>rd</sup> Party to GCS)

BILKENT Bilkent University, Turkey (3<sup>rd</sup> Party to UHEM)

BSC Barcelona Supercomputing Center - Centro Nacional de

Supercomputacion, Spain

CaSToRC The Computation-based Science and Technology Research Center

(CaSToRC), The Cyprus Institute, Cyprus

CCSAS Computing Centre of the Slovak Academy of Sciences, Slovakia CEA Commissariat à l'Energie Atomique et aux Energies Alternatives,

France (3<sup>rd</sup> Party to GENCI)

CENAERO Centre de Recherche en Aéronautique ASBL, Belgium (3<sup>rd</sup> Party to

UANTWERPEN)

CESGA Fundacion Publica Gallega Centro Tecnológico de Supercomputación

de Galicia, Spain, (3<sup>rd</sup> Party to BSC)

CINECA Consorzio Interuniversitario, Italy

CINES Centre Informatique National de l'Enseignement Supérieur, France (3<sup>rd</sup>

Party to GENCI)

CNRS Centre National de la Recherche Scientifique, France (3<sup>rd</sup> Party to

GENCI)

CSC Scientific Computing Ltd., Finland

CSIC Spanish Council for Scientific Research (3<sup>rd</sup> Party to BSC)

CYFRONET Academic Computing Centre CYFRONET AGH, Poland (3<sup>rd</sup> Party to

PNSC)

DTU Technical University of Denmark (3<sup>rd</sup> Party of UCPH)

EPCC at The University of Edinburgh, UK

EUDAT OY

ETH Zurich (CSCS) Eidgenössische Technische Hochschule Zürich – CSCS, Switzerland

GCS Gauss Centre for Supercomputing e.V., Germany

GÉANT Vereniging

GENCI Grand Equipement National de Calcul Intensif, France

GRNET National Infrastructures for Research and Technology, Greece ICREA Catalan Institution for Research and Advanced Studies (3<sup>rd</sup> Party to

BSC)

INRIA Institut National de Recherche en Informatique et Automatique, France

(3<sup>rd</sup> Party to GENCI)

IST-ID Instituto Superior Técnico for Research and Development, Portugal (3<sup>rd</sup>

Party to UC-LCA)

IT4I Vysoka Skola Banska - Technicka Univerzita Ostrava, Czech Republic

IUCC Machba - Inter University Computation Centre, Israel

JUELICH Forschungszentrum Jülich GmbH, Germany

KIFÜ (NIIFI) Governmental Information Technology Development Agency, Hungary

KTH Royal Institute of Technology, Sweden (3<sup>rd</sup> Party to SNIC-UU)

KULEUVEN Katholieke Universiteit Leuven, Belgium (3<sup>rd</sup> Party to

**UANTWERPEN**)

LiU Linkoping University, Sweden (3<sup>rd</sup> Party to SNIC-UU)

MPCDF Max Planck Gesellschaft zur Förderung der Wissenschaften e.V.,

Germany (3<sup>rd</sup> Party to GCS)

NCSA NATIONAL CENTRE FOR SUPERCOMPUTING APPLICATIONS.

Bulgaria

NTNU The Norwegian University of Science and Technology, Norway (3<sup>rd</sup>

Party to SIGMA2)

NUI-Galway National University of Ireland Galway, Ireland

PRACE Partnership for Advanced Computing in Europe aisbl, Belgium PSNC Poznan Supercomputing and Networking Center, Poland University of Southern Denmark (3<sup>rd</sup> Party to UCPH)

SIGMA2 UNINETT Sigma2 AS, Norway SNIC-UU Uppsala Universitet, Sweden

STFC Science and Technology Facilities Council, UK (3<sup>rd</sup> Party to UEDIN)

SURF SURF is the collaborative organisation for ICT in Dutch education

and research

TASK Politechnika Gdańska (3<sup>rd</sup> Party to PNSC) TU Wien Technische Universität Wien, Austria UANTWERPEN Universiteit Antwerpen, Belgium

UC-LCA Universidade de Coimbra, Labotatório de Computação Avançada,

**Portugal**

UCPH Københavns Universitet, Denmark UEDIN The University of Edinburgh

UHEM Istanbul Technical University, Ayazaga Campus, Turkey

UIBK Universität Innsbruck, Austria (3<sup>rd</sup> Party to TU Wien)

UiO University of Oslo, Norway (3<sup>rd</sup> Party to SIGMA2)

UL UNIVERZA V LJUBLJANI, Slovenia

ULIEGE Université de Liège; Belgium (3<sup>rd</sup> Party to UANTWERPEN)

U Luxembourg University of Luxembourg

UM Universidade do Minho, Portugal, (3<sup>rd</sup> Party to UC-LCA)

UmU Umeå University, Sweden (3<sup>rd</sup> Party to SNIC-UU)

UnivEvora Universidade de Évora, Portugal (3<sup>rd</sup> Party to UC-LCA)

UnivPorto Universidade do Porto, Portugal (3<sup>rd</sup> Party to UC-LCA)

UPC Universitat Politècnica de Catalunya, Spain (3<sup>rd</sup> Party to BSC)

WCSS Politechnika Wrocławska, Poland (3<sup>rd</sup> Party to PNSC)

**USTUTT-HLRS**

Universitaet Stuttgart – HLRS, Germany (3<sup>rd</sup> Party to GCS)

# **Executive Summary**

The work package 5 (WP5) – "HPC Planning and Commissioning" of PRACE-6IP builds on the work of previous PRACE-IP projects in terms of technology watch, know-how and best practices for energy-efficient High Performance Computing (HPC) Centre Infrastructures design and operations, and prototyping of HPC systems. The main aim is to deliver, in the general perspective of the EU HPC changing landscape and EuroHPC, information and guidance which could be useful for decision makers at different levels: PRACE aisbl, PRACE members, EuroHPC Joint Undertaking (JU) and other European HPC sites. On this direction, Task 5.1 – "Europe-Centred View of the Worldwide HPC Technology and Market Landscape" studies worldwide projects and strategies towards Exascale and compares what is happening in different parts of the world, in perspective of efforts in Europe. It also carries out market studies and overviews, focusing in particular on the market shares of European and non-European suppliers and the adoption of European technologies and complementary paradigms to HPC in Europe.

After extended discussions with EC, the Infrastructure Advisory Group (INFRAG), the Research & Innovation Advisory Group (RIAG) and European Extreme Data & Computing Initiative (EXDCI-2), it was decided to focus the work within Task 5.1 on specific topics. Six topics were chosen and presented separately through technical reports: "Edge Computing: An Overview of Framework and Applications", "Data Management Services and Storage", "State-of-the-Art and Trends for Computing and Interconnect Network Solutions for HPC and AI", "Quantum Computing – A European Perspective" and "Security in an Evolving European HPC Ecosystem", "User requirements influencing HPC technologies".

This document is the final deliverable of WP5, Task 5.1, which summarises the work done within this task during the project. It outlines the details of the technical reports selection process and briefly describes the conclusions derived within the reports.

#### 1 Introduction

Task 5.1 "Europe-Centred View of the Worldwide HPC Technology and Market Landscape" of PRACE-6IP Work Package 5 (WP5), is the continuation of a well-established effort of previous PRACE Implementation Phase projects (IP) to carry out an assessment of the HPC market based on market surveys, Top500 and Green500/HPCG lists analyses, supercomputing conferences (mainly ISC, SC and the European Workshops on HPC Infrastructures) and information exchange between vendors and WP5 experts who are involved in the work package. Since PRACE is the largest independent European HPC community, it can provide a neutral Technology Watch vision. The PRACE community has the expertise on how to introduce new technologies in advance. Early technology adoption ensures successful massive deployment and optimal exploitation of resources by the users communities.

Within the EuroHPC era, while PRACE-6IP WP5 is providing an exhaustive view on technologies that will fly on the market over the future years, the new scope defined after several discussions also focuses on worldwide market shares to understand how Europe is positioned compared to the worldwide landscape, i.e. at least US, China, and Japan.

The first three technical reports, published in December 2020, were:

- "Edge Computing: An Overview of Framework and Applications" explains why Edge Computing is needed and how the edge architecture is typically structured, presenting the technologies that help this cutting-edge model to function properly.

- "Data Management Services and Storage" summarises the history of this development and examines some of the technologies that are building blocks of nearfuture storage systems, both hardware and software required to manage the large amounts of data.

- "State-of-the-Art and Trends for Computing and Interconnect Network Solutions for HPC and AI" provides a consolidated view on the current and mid-term technologies (2019-2022+) for two important components of an HPC/AI system: computing (general purpose processor and accelerators) and interconnect capabilities and provides an outlook on future trends in terms of mid-term projections about what users may expect in the coming years.

Two technical reports were published in October-November 2021:

- "Quantum Computing A European Perspective" gives an overview of quantum computing, the present state of affairs, and future scenarios.

- "Security in an Evolving European HPC Ecosystem" analyses challenges and requirements related to security in the context of an evolving European HPC ecosystem, to provide selected strategies on how to address them, and to come up with a set of forward-looking recommendations.

The final technical report is expected in January 2022:

"User Requirements influencing HPC Technologies" will present how both software and hardware architectures are affected and can be adjusted to follow new computing trends and meet future needs. It is still under development given the timelines of PRACE-6IP PMO.

The remainder of this document is organised as follows. Chapter 2 describes the selection process of technical report topics, discusses the organisational aspects and the review process.

## Worldwide HPC technology and market landscape

**D5.2**

Chapter 0 presents brief descriptions of the technical reports that are (and will be) developed within PRACE-6IP. Chapter 4 provides the conclusion. Annex 1 gives the official published version of the five technical reports.

# 2 Approach of technical reports

### 2.1 Selection of topics

The outcome of Task 5.1 activities was originally planned to be published in 2 white papers on Market and Technology Watch in 2020 and 2021 and to be summarised in the final deliverable D5.2, following a format similar to previous PRACE market and technology watch white papers and deliverables. The participants had already agreed on the table of contents of the first white paper in May 2019 and authors and chapter editors were assigned.

However, after the final review of PRACE-5IP and EC recommendations, the scope of both the white papers and the deliverable has changed and turned to be more European centric, covering new, emergent and complementary paradigms to HPC. The scope and focus of the technology watch was also refined in collaboration with the INFRAG, the RIAG and EXDCI-2, to include topics of their interest and avoid overlaps with their work.

Finally, after several discussions, WP5 and PMO have decided to switch from an extensive monolithic annual market watch report to a series of technical reports that aim to describe the state-of-the-art and mid-term trends of the technology and market landscape in the context of HPC and Artificial Intelligence (AI), edge-, cloud- and interactive computing, big data and other related technologies. The series provides information and guidance useful for various European sites, members of PRACE and EuroHPC, and the EuroHPC Advisory Groups INFRAG and RIAG. Especially INFRAG is interested in a long-term analysis of the HPC market, user requirements, trends and comprehensive recommendations.

## 2.2 Organisation

Monthly teleconferences were organised that involved discussions on progress, pending issues, timelines, updates from partners involved, etc. Separate discussions were also organised by WP5 leader, Task 5.1 leader and PMO with INFRAG, RIAG and EXDCI-2 in order to be aligned on the topics selection and the final form and content of technical reports. Meeting minutes and presentation slides are uploaded to the project internal collaboration platform, BSCW.

The development activity was led by the Task 5.1 leader Norbert Meyer (PSNC) assisted by WP5 leader Volker Weinberg (BADW-LRZ), with the support of the technical reports lead authors:

- Andreas Johansson (SNIC): "Data Management Services and Storage"

- Christelle Piechurski (GENCI): "State-of-the-Art and Trends for Computing and Interconnect Network Solutions for HPC and AI"

- Dirk Pleiter (KTH): "Security in an Evolving European HPC Ecosystem"

- Ezhilmathi Krishnasamy (U Luxembourg): "Edge Computing: An Overview of Framework and Applications"

- Evangelia Athanasaki (GRNET)/Norbert Meyer (PSNC): "User Requirements influencing HPC Technologies"

- Mikael Johansson (CSC): "Quantum Computing A European Perspective"

#### 2.3 Review and Publication

The internal review of these technical reports followed the quality assurance process in place for all PRACE-IP deliverables and white papers – each report was internally reviewed by one member of the PMO and one project representative. This has further improved the quality of the published reports and deliverables. Prior to publication, the first set of three technical reports ready in December 2020 was sent for feedback also to INFRAG and RIAG, which confirmed the good quality and importance of these documents.

To facilitate further outreach of the technical reports, they are published on Zenodo and thus, have been assigned with a DOI.

# 3 Summaries of Technical Reports

Technical reports are publicly available, so this section only provides a brief overview on the six reports that have been developed within PRACE-6IP. The complete list of all market and technology watch reports published so far within the PRACE-IP projects, starting from 2016 within PRACE-4IP, can be found via [1] (Figure 1).

Figure 1: Snapshot illustrating PRACE web infrastructure for market and technology watch deliverables and technical reports

### 3.1 Edge Computing: An Overview of Framework and Applications

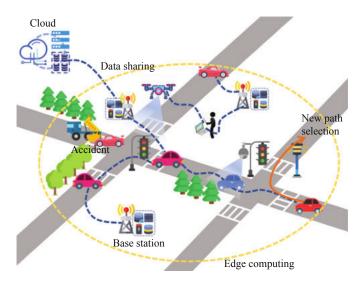

Presently, with the Internet of Things (IoT), we produce lots of data, and this data should be processed and analysed quickly, close to where it is produced. Edge Computing aims to solve these criteria, and it is considered an emerging technology. Cloud Computing and Supercomputers are also able to process and analyse a large volume of data. However, the major bottleneck with these infrastructures is data transfer latency. In particular, real-time applications such as camera and mobile phone data should be processed very quickly; this is where Edge Computing is applicable, because we cannot afford to lose time on data transfer from one location to another. More importantly, data privacy is a primary concern nowadays, and it is better to process the data within the premises where it is produced. Edge Computing is not meant to replace Cloud or Supercomputers; however, it is determined to share the computational burden.

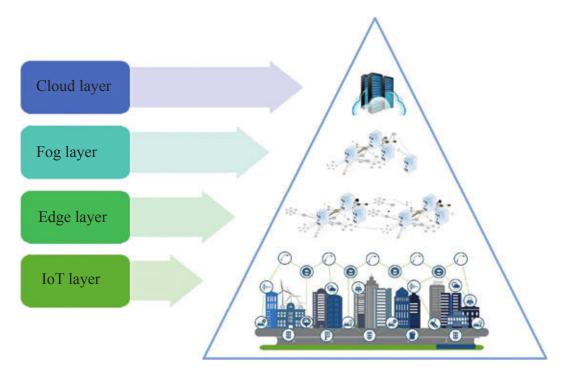

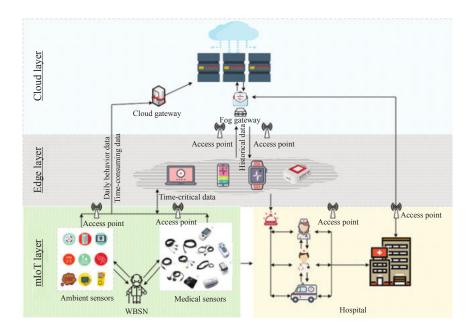

Edge Computing uses embedded architecture devices, which consume less power and are more powerful to process real-time data, such as car cameras and airplane sensors. The Edge Computing architecture hierarchies are IoT, Edge layer, Fog layer, and Cloud layer. The IoT refers to cameras and other sensors that can produce the data; the Edge layer means the data is analysed and processed with advanced embedded architecture. The Fog layer & Cloud layer are handling large volumes of data that cannot be processed at the Edge layer.

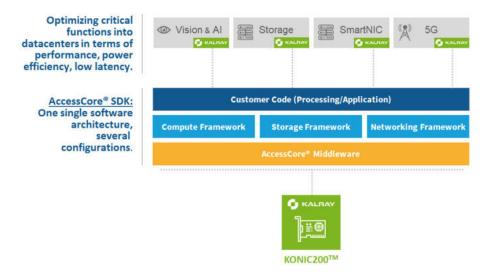

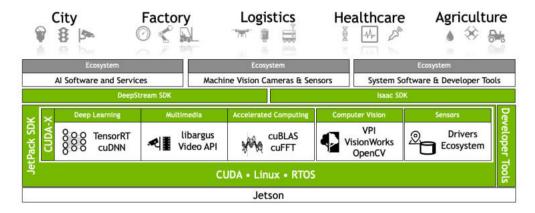

Recently, many vendors have launched advanced and energy efficient embedded architectures that can be used at the Edge layer. For example, Nvidia's Jetson AGX Xavier has 512 CUDA cores, 8 CPU cores with 32 GB memory; and Kalray's KONIC200-HP has 160 CPU cores. These machines have tensor cores and, more importantly, are designed to perform the AI/ML computations efficiently. Moreover, these modern embedded architectures support advanced AI/ML numerical libraries to run AI/ML computations.

However, these advanced architectures still depend on the Cloud and Supercomputers in two scenarios: heterogeneous data and distributed computing. Sometimes, at the Edge, IoT devices produce different types of data: it can be video, audio, and text; and it might be hard to solve at the Edge layer, and hence Cloud Computing can be helpful. Often, IoT devices produce large volumes of data; in these situations, part of the data should be processed very quickly and some not. This is where distributed computing is applicable where both Edge Layer and Cloud or Supercomputers share the computation.

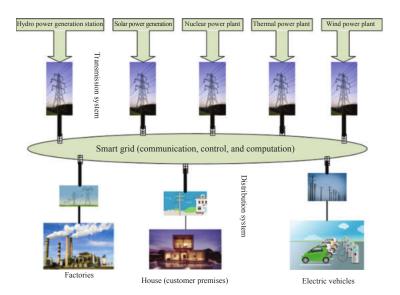

There are plenty of situations where Edge Computing applications are vital. They are medical applications, smart cities, industrial applications, and smart grid & public safety. Nevertheless, Edge Computing still faces some problems that prevent its applications from growing further in many areas. Notably, they are naming, programmability, and Edge device management. In particular, since Edge devices are heterogeneous, it is hard to program as an end-user compared to the cloud. For example, on the cloud, the end-users can deploy their application with minimal effort.

The complete technical report can be accessed via [2] on PRACE website or [3] on Zenodo.

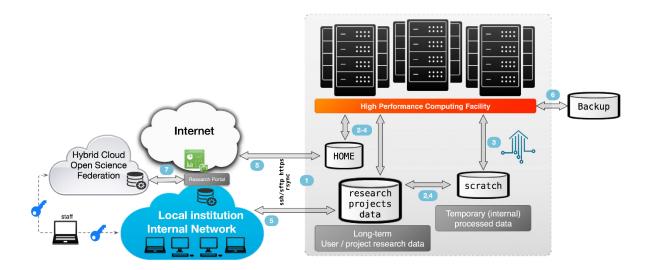

## 3.2 Data Management Services and Storage

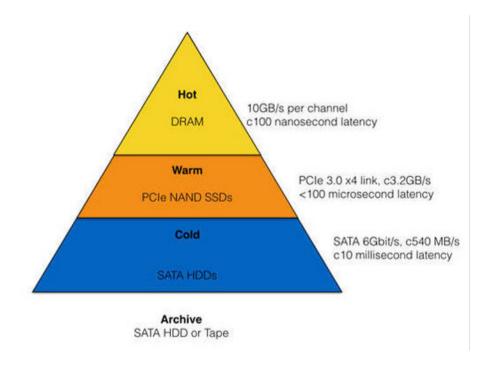

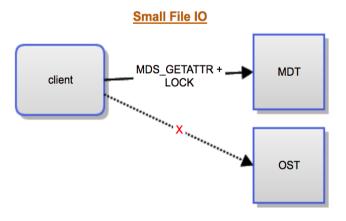

HPC storage systems have evolved from relatively simple systems attached to a single cluster to site-wide complex infrastructures supporting migration of data between storage tiers with different performance characteristics and I/O acceleration. Exascale systems and AI workloads will continue this trend by placing even greater demands on speedy access to data.

The report covers topics from the hardware substrate that sits at the base level of the storage infrastructure through file systems at the operating system level up to data management software and protocols that provides services to support research workflows.

One conclusion in the report is about the need for making data findable and accessible, and this requires software support for managing metadata.

#### Storage infrastructure

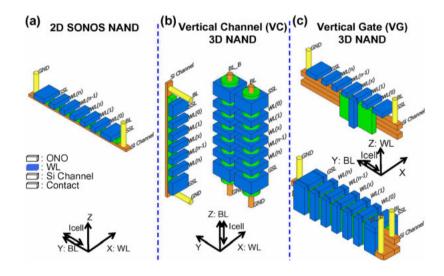

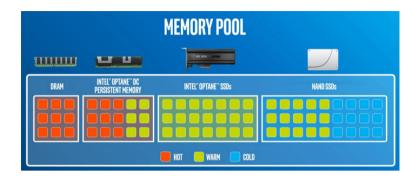

Hardware for storage needs to strike a compromise between cost, size and performance. Due to this need complex storage hierarchies have evolved and are now becoming even deeper as very high-performance flash devices using the NVMe protocol are placed closer to CPUs. Traditional hard drives are relegated to a supporting role as large volume storage devices. Flash technologies and storage solutions selected for the first announced Exascale systems are explored as well as hybrid disk arrays and tape libraries.

#### File systems

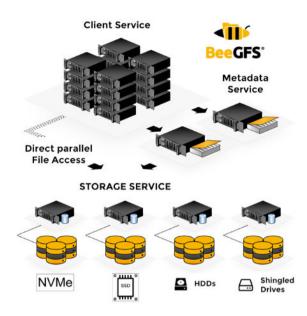

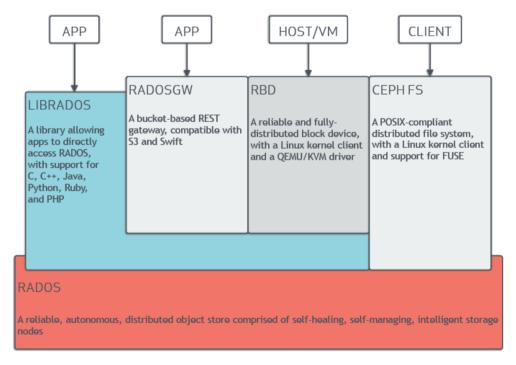

In this section some file systems commonly used at HPC sites are examined with regards to functionality (access protocols and tiering support for example) and how they have evolved over time. File systems covered are Lustre, Spectrum Scale, BeeGFS and Ceph.

While some of the file systems support object storage, the focus in this section is on their use as traditional POSIX file systems for compute clusters.

### Data management services

To meet future needs, new technologies for data management and tiering are becoming increasingly important and this section explores several available technologies.

Cloud storage system have standardised access methods for object storage, and these can also be used for HPC storage to enable workflows combining traditional clusters and cloud technologies.

Tiering can be used for both handling I/O acceleration for data used in computations, and moving data to systems suited for long-term storage of data that is rarely accessed. Both types are covered with multiple examples of each type.

Handling input data to jobs and their resulting output is increasingly requiring support systems as both jobs and data sets increase in size. Many software suites are available, ranging from very domain specific ones to more general-purpose data management packages. Some systems also support publication of data sets or workflow integration.

The complete technical report can be accessed via [4] on PRACE website or [5] on Zenodo.

# 3.3 State-of-the-Art and Trends for Computing and Interconnect Network Solutions for HPC and Al

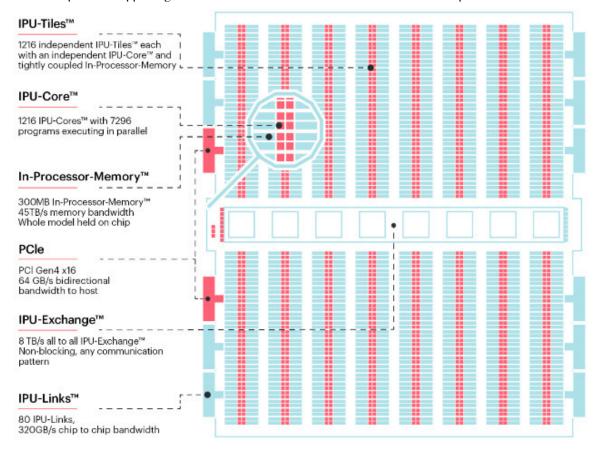

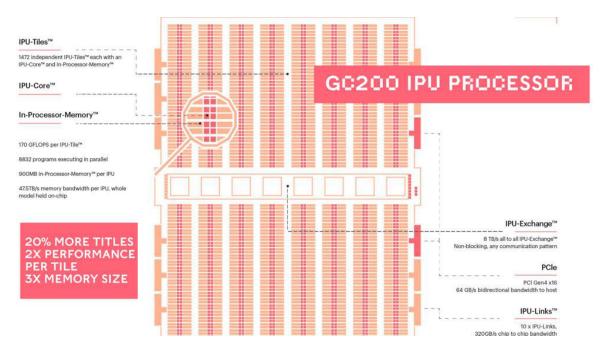

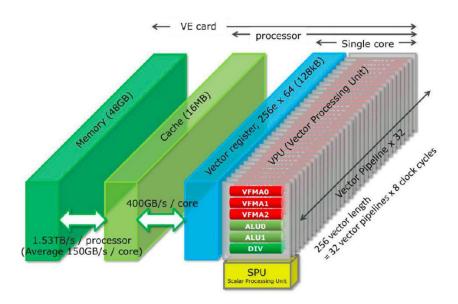

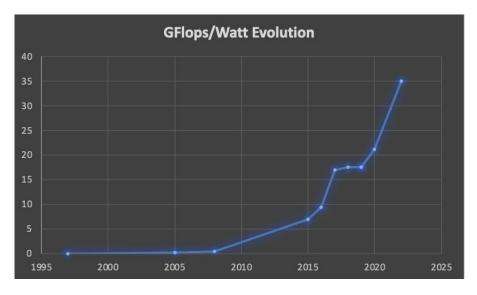

Since 2000, HPC resources have been extremely homogeneous in terms of underlying processors technologies. However, it becomes obvious that new trends tend to bring new microarchitectures for General Purpose Processors (GPPs) and new heterogeneous architectures, combining accelerators with GPPs, to sustain both numerical simulation and AI workflows. The report provides a consolidated view on 2019-2022+ most popular and known technologies both on general purpose processors and accelerators as interconnect capabilities starting by key factors influencing chips performance and their relation to architectural choices up to major trends below:

- The big CPU market players are still Intel and AMD (X86\_64) with a strong competition between the two. While the X86\_64 microarchitecture is still the most adopted in the HPC market, ARM processors are continuing to expand their market share through Fujitsu (A64FX), Marvell (ThunderX until their cancelation), Amazon (Graviton), Ampere (Altra) and SiPearl, the company which designs and will sell the EPI Rhea processor, the only European ARM-based processor with HPC features (HBM and SVE capabilities).

- Market focus is to be part both of HPC and AI markets, with the capability to provide both CPU and GPU and to improve the CPU-GPU interconnect performance and CPU/GPU cache memory coherency as well as the global memory bandwidth, either on pure DDR technology or by using HBM. Most of the high-end computing capabilities would, at least, partially, rely on accelerators with CPU technologies hosting either GPUs, accelerators and/or FPGAs. FPGAs might see their use increased in the future for HPC and AI. Similar to competitor technologies, it focuses on high interconnect and memory bandwidth and offers data types suitable for AI workloads.

- There are only a few players capable to power large scale supercomputers on the low-latency interconnect network (> 5000 nodes): Mellanox (IB), Atos (BXI, the only

European Inter-Node Interconnect), HPE Former Cray (Aries) and HPE Cray (Slingshot). Low latency Ethernet is a promising technology that will have to demonstrate its capabilities on the field.

- More advanced intra-node interconnect will allow to build a tighter integration between CPU and GPU (cache memory coherency, limit data movement between CPU and GPU, open to design an accelerated node with DDR-less CPU and memory consumed directly from GPU/accelerators' HBM). It will also help to support the adhesion of MCM design to go beyond the current process manufacturing limits and more powerful chips. Openness of intra-node interconnects will be key for a wide adoption and ensure hardware interoperability as ease software programming.

- While further near-terms developments might include merging CPUs and GPUs onto a single die to build an APU dedicated to HPC (and AI), longer-term investment could be quantum computing with a first approach, to another type of hybrid systems based on current computing technologies and quantum accelerators and/or simulator.

- Future Exascale systems target 50 GFlops/W to sustain a high energy efficiency. This ratio should be achievable in 2023 timeframe, either through heterogeneous architectures based on accelerator computing capabilities combined with ARM processors or through a future well-balanced ARM processor design with enhanced capabilities (AI, edge computing, etc.).

The complete technical report can be accessed via [6] on PRACE website or [7] on Zenodo.

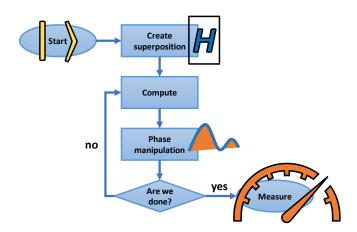

## 3.4 Quantum Computing - A European Perspective

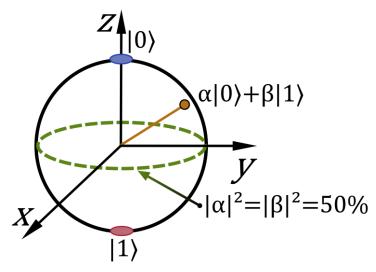

Quantum Computing (QC) is expected to bring a new revolutionary component to the high-performance computing (HPC) palette. It is expected to have an impact on practically all fields of science, research, development, and innovation that utilise, or *could* utilise computational modelling. When sufficiently mature, quantum computers can tackle problems that due to their size and complexity will forever stay beyond the reach of conventional computing alone.

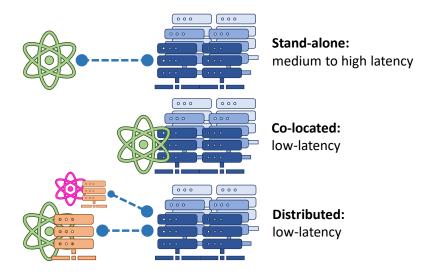

Incorporating QC into existing supercomputing infrastructure is essential. For real-world problems, quantum computers will never *replace* classical computers, but instead become an integral part of HPC. Europe has a unique opportunity to create world-leading supercomputing infrastructures incorporating quantum technology by capitalising on the established expertise of European HPC centres in conjunction with the European quantum technology ecosystem. Efforts should be pan-European, following the already proven success of the EuroHPC JU for setting up pre-Exascale computing facilities, and the plans for going to Exascale and beyond. This requires dedicated support for quantum hardware and software developments, as well as for education. Coordinated efforts for catalysing early adoption of quantum computing in academia and industry are essential.

As with the traditional supercomputing infrastructure, diversity is key when setting up a distributed European HPC+QC backbone. Endeavours should be concerted, but not overly concentrated. As QC technology is still in its early stages, it is essential to support different strategies for merging HPC and QC in Europe. Two main approaches for implementing HPC+QC that are suitable for the widest selection of algorithms, applications, and use cases exist: (1) the co-located approach, where quantum computers are placed in physical proximity to traditional HPC resources; (2) the more general distributed approach, where the quantum computers and the HPC infrastructure can be separated. Setup of both approaches should

commence immediately. The connection to the European efforts to set up a quantum internet, which in the future could connect and pool quantum computers over a distance should be actively maintained.

A specific challenge is to ensure commercial competitiveness on the global scene. In Europe, the industrial quantum ecosystem is largely start-up driven. Sustained, sufficiently long-term EU-level support for the emerging QC industry is needed to ensure that European competence and capacity in the field reaches a critical mass of self-sustainability and sovereignty.

Europe needs to raise its goals for quantum computing sufficiently high to keep up with global developments. Still, we need to remember that quantum computing is in its infancy. To reach the number and quality of qubits needed for truly disruptive quantum computing, the roughly one hundred noisy qubits that we have today have to be scaled up by four to five orders of magnitude. Significant support for basic research into quantum technologies is required. Only then can European competitiveness in the field be ensured. The basic research on quantum technologies performed for decades in partnership between all European countries, whether members of the European Union or not, has laid the seeds for the fruits we reap today. Global collaboration needs to continue, with minimal restriction, so that quantum computing can be harnessed for solving pressing challenges of our society as soon as possible.

The complete technical report can be accessed via [8] on PRACE website or [9] on Zenodo.

## 3.5 Security in an Evolving European HPC Ecosystem

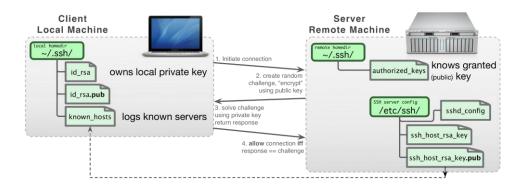

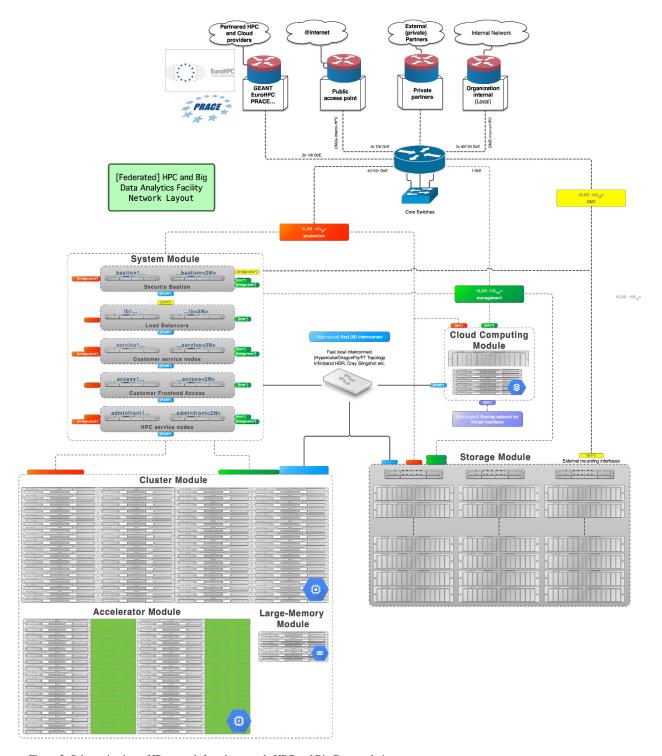

The goal of the technical report was to analyse challenges and requirements related to security in the context of an evolving European HPC ecosystem, to provide selected strategies on how to address them, and to come up with a set of forward-looking recommendations. A key assumption made in this technical report is that we are in a transition period from a setup, where HPC resources are operated in a rather independent manner, to centres providing a variety of e-infrastructure services, which are not exclusively based on HPC resources and are increasingly part of federated infrastructures. Furthermore, the changing risk assessment due to an increased risk of cyber-attacks as well as the need for a higher level of protection, e.g. in the context of the processing of sensitive data, has to be taken into account.

The technical report documents and discusses a selected set of approaches to improve security in the context of infrastructures that comprise HPC resources. This includes improving security for SSH-based access to HPC systems, making the design of networks within HPC centres more secure, and introduction of monitoring and intrusion detection systems (IDS). Based on a survey circulated to PRACE members it seems that IDS solutions are not yet widely used.

Due to the trend towards federation of services that are in parts based on HPC resources, security issues cannot be addressed at the level of a single data centre anymore, but rather need to be addressed at a federation level. One strategy to enhance security and establish common security levels is to leverage standards. The technical report therefore includes an analysis of different security standards that are relevant in this context.

The technical report formulates the following recommendations:

• Data centres should review their security strategies within the evolving European HPC ecosystem, where an increased number of services are provided beyond providing access to a supercomputer.

- With SSH being currently the most widely used network protocol for connecting to an HPC system, SSH configurations should be hardened for security, e.g. by enforcing DNS hostname checking, disabling password-based authentication, restricting access through white-listing methods, or by using SSH configuration scanners.

- Use of Intrusion Detection Systems should be further explored as relatively few sites seem to use these today.

- Security standards for HPC centres should be adopted at European level and should be

leveraged (or even be established) to realise a common security level within a European

infrastructure where services start to be federated, which would improve the usability

of this infrastructure by users with specific security requirements, e.g. in the context of

processing of sensitive data. The C5 catalogue from the German Federal Office for

Information Security is a promising starting point, because it prescribes concrete

measures.

- The collaboration between HPC centres in Europe should be strengthened to improve the response to security incidents, which in future are even more likely to affect more than one site. Such collaboration would also allow to harmonise security measures to avoid users having to deal with different security restrictions.

The complete technical report can be accessed via [10] on PRACE website or [11] on Zenodo[10].

#### 4 Conclusion

The series of market watch deliverables has been initiated in PRACE-4IP and has been continuously extended since then.

Within PRACE-6IP the scope and focus of the technology watch was refined in collaboration with INFRAG, RIAG and EXDCI-2, to include topics of their interest and avoid overlaps with their work and it was presented in the form of separate technical reports:

- "Edge Computing: An Overview of Framework and Applications", published in December 2020

- "Data Management Services and Storage", published in December 2020

- "State-of-the-Art and Trends for Computing and Interconnect Network Solutions for HPC and AI", published in December 2020

- "Quantum Computing A European Perspective", published in October 2021

- "Security in an Evolving European HPC Ecosystem", published in November 2021

- "User Requirements influencing HPC Technologies", will be published in January 2022

These reports are published on the PRACE website and Zenodo.

# 5 Annex 1: Technical reports

#### Available on-line at www.prace-ri.eu

#### Partnership for Advanced Computing in Europe

# Edge Computing: An Overview of Framework and Applications

Ezhilmathi Krishnasamy<sup>a,\*</sup>, Sebastien Varrette<sup>a</sup>, Michael Mucciardi<sup>b</sup>

<sup>a</sup>University Du Luxembourg, SnT, UL HPC, Luxembourg. <sup>b</sup>Barcelona Supercomputing Center, Spain.

#### Abstract

This report gives an overview of the Edge Computing paradigm and its applications. Indeed, with the advent of the Internet of Things (IoT) era, many electronic devices and sensors produce a vast volume of data which should be processed in a timely manner and this novel computing model is nowadays seen as a pertinent answer to this open challenge. This report thus explains why Edge Computing is needed and how the edge architecture is typically structured. It further presents the technologies that help this cutting-edge model to function properly. Since Edge Computing involves a heterogeneous architecture, it requires to adapt to a few technological recommendations for optimal performance. In this context, this report reviews the latest hardware technology trends tied to Edge Computing developments, and points out technical challenges implementing this innovative computing model. In particular, we analyse how High Performance Computing and Cloud Computing infrastructures can be efficiently organised to design an Edge Computing-based framework able to tackle cutting-edge issues solved by Artificial Intelligence techniques. Finally, this report presents selected real-world applications of the Edge Computing paradigm across multiple domains affecting our daily life, i.e. healthcare, smart city and grids, industry 4.0 and public safety.

1

26.11.2020

<sup>\*</sup>Corresponding author, e-mail: ezhilmathi.krishnasamy@uni.lu

# **Contents**

| 1. | Introduction                                                                                                                                                                                                    | 3              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2. | Why Edge Computing?                                                                                                                                                                                             | 3              |

| 3. | Comparison between the Cloud and Edge Computing Paradigms                                                                                                                                                       | 4              |

| 4. | Edge Computing Architecture and Technology4.1. Edge Computing Architecture4.2. Virtualisation4.3. Resource Management and Edge Orchestration4.4. Developing Platform enabling Data Analytics for Edge Computing | 7<br>7         |

| 5. | Latest Trends in Edge Computing 5.1. Nvidia Jetson                                                                                                                                                              | 11<br>12<br>12 |

| 6. | In Reality: Edge vs. Supercomputers/Cloud Computing                                                                                                                                                             | 14             |

| 7. | Selected Use Cases of Edge Computing enabled Applications 7.1. Medical Applications                                                                                                                             | 15<br>16       |

| 8. | Present Challenges                                                                                                                                                                                              | 18             |

| 9. | Summary                                                                                                                                                                                                         | 18             |

#### 1. Introduction

This technical report is part of a series of reports published in the Work Package "HPC Planning and Commissioning" (WP5) of the PRACE-6IP project. The series aims to describe the state-of-the-art and mid-term trends of the technology and market landscape in the context of High Performance Computing (HPC) and Artificial Intelligence (AI), Edge-, Cloud- and Interactive Computing, Big Data and other related technologies. It provides information and guidance useful for decision makers at different levels: PRACE aisbl, PRACE members, EuroHPC sites and the EuroHPC advisory groups "Infrastructure Advisory Group" (INFRAG) and "Research & Innovation Advisory Group" (RIAG) and other European HPC sites. Further reports published so far cover "State-of-the-Art and Trends for Computing and Network Solutions for HPC and AI" [1] and "Data Management Services and Storage Infrastructures" [2]. The series will be continued in 2021 with further selected highly topical subjects.

Edge Computing aims to process the data very close to the source where it is produced. Many electronic devices are currently connected to the Internet of Things (IoT), which will produce a massive volume of data, and it might be even larger with mobile phones in a 5G network. Cisco Global Cloud Index estimated in 2019 that IoT devices will generate around 500 zettabytes of data [3]. Furthermore, data traffic will be approximately 10.4 zettabytes, which is up from 3.4 zettabytes in 2014 [4]. Moreover, by 2020, 50 million streaming IoT devices will be in use [5].

Edge Computing refers to processing the data on the device and very close to the device. This massive volume of data might be hard to handle entirely on the Cloud Computing network. To face this challenge, Edge Computing offers the full computation or part of the computation that can process the data at the Edge network, which is in very close proximity to the data source. It enables low latency, faster response, and more comprehensive data analysis.

Usually, devices connected to the IoT provide the service in healthcare, smart cities, smart grid, transportation, multimedia, and security. In general, those services depend on AI methodologies, which are compute-intensive and use massive data. A few years back, these devices usually sent the data to the cloud or local data centre to process the data. With ongoing development in Edge Computing, the part of the data at the Edge node can be processed, thus minimising the application's overall latency.

The rest of this technical report is organised as follows: Section 2 focuses on why Edge Computing is needed. Section 3 gives a quick overview of the difference between Edge Computing and Cloud Computing. Section 4 explains the technologies and architectures that are available for Edge Computing. Furthermore, virtualisation, resource management, and development for Edge Computing platforms and how these categories define the proper working functionality of Edge Computing are described. Section 5 focuses on Edge Computing's latest architecture trends, giving more detail about Nvidia Jetson, Raspberry PI, Tinker, and Kalray MPPA. Section 6 presents how Edge Computing still depends on supercomputers/data centres or Cloud Computing for data-intensive applications, particularly AI methodologies. Section 7 focuses on the applications of Edge Computing in real-world applications. Four applications are categorised with more examples in each category, such as healthcare, smart city, industrial applications, smart grid, and public safety. Finally, Section 8 presents a few challenges while implementing Edge Computing, specifically about naming and programmability.

# 2. Why Edge Computing?

Currently, the entire world is going towards digitalisation, and lots of data is produced in various fields. Moreover, in most cases, this data needs to be processed in a short time to facilitate the present technology (real-time applications). A few years back, cloud technologies have been introduced, gradually reducing the need for small- and medium-scale companies and research institutes to own a computer to do the computations. Nevertheless, the end-users still need to send and receive the data to and from the location where the machine is located. In contrast, Edge Computing is an alternative option for doing computations where the data is located, and is especially suited for real-time applications.

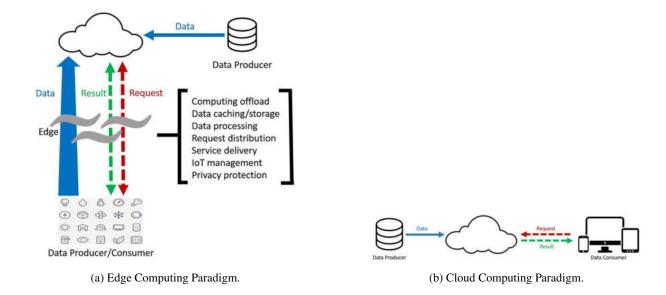

In particular, part of the IoT might require short response time, private data, and Big Data, which could be challenging for the network. However, Cloud Computing cannot handle few of these challenges. Figure 1a and 2 show the paradigm and schematic model of Edge Computing.

Edge Computing is not a direct competition to Cloud Computing or supercomputers, but it is certainly sharing computational burden with cloud technology and supercomputers. If the present trend continues, more robust and energy-efficient small/embedded machines will improve the computations in the future. The following items provide information about why Edge Computing is needed:

• *Push from the Cloud Services:* In general, Cloud Computing has proven to be very efficient in terms of computation, but in some situations, there has to be an alternative solution to avoid data transfer bottlenecks. Edge Computing is solving this problem. For example, a Boeing 787 produces 5 Gigabytes (GBs) of data every

Figure 1: Workflow Model of Cloud and Edge Computing Paradigm [7].

minute [6], and transferring this data to a satellite or the ground is not efficient for data processing. Yet another example could be autonomous vehicles, and its information needs to be processed very frequently to steer the vehicle in the right direction. It is not feasible to process these data in the cloud as the bandwidth of the network is a bottleneck. Moreover, Edge Computing consumes less energy compared to cloud technology due to the minimal consumption of embedded devices.

- Push from the Internet of Things: Presently, electronic devices such as LEDs, surveillance cameras, and air quality sensors are part of the IoT, and they produce and consume a lot of data. In future, there will be even more electronic devices that will be connected to the IoT. It is not feasible to process all the data in the cloud due to the bandwidth and latency. This means some of the data need to be processed at the level of Edge devices. Moreover, privacy is a big concern for cloud solutions, Edge Computing can minimise this concern by restricting the data within the Edge. Figure 1b shows the traditional cloud computing paradigm, where raw data is produced and transferred to the cloud and consumers are sending the request to access the data from the cloud. Basically, this structure is not optimal since a large amount of data needs to be transferred, and in some situations, data privacy is also a concern.

- Change from a Data Consumer to a Producer: A device at the Edge not only consumes the data from the cloud, but it also produces the data and uploads the data to the cloud. Watching a YouTube video from your mobile phone, using Facebook and Instagram, are examples where Edge users pull the data from the cloud. At the same time, Edge devices produce the data, such as taking pictures or recording videos. When the Edge users try to upload this data to the cloud, it could be a lot of data depending on the resolution. This would occupy even more bandwidth for the uploading. In a situation like this, the resolution can be adjusted at the Edge device before uploading the data to the cloud.

# 3. Comparison between the Cloud and Edge Computing Paradigms

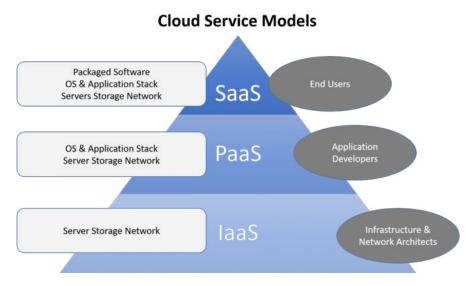

Edge Computing is a paradigm relying on similar concepts deployed within Cloud models. In Cloud Computing, either in public, private or hybrid types of accessibility models, data processing or computation occurs at the data centre, where it has a substantial computational resource and data needs to be transferred back and forth. The cost model that made this paradigm so popular since the last decade is that the end-users only pay for the resources they used, whether in terms of computing, storage or data transfer capacities. In practice, the following deployment models are traditionally considered within the Cloud Computing paradigm [9]:

**SaaS** "Software as a Service", this refers to using the existing software or applications from the cloud, for example, using Gmail, Office 365, etc. Here, a cloud provider is controlling software or applications, and end-users use the software.

PaaS "Platform as a Service", this refers to using your software but using the cloud resource as hardware, for exam-

4

26.11.2020

Figure 2: Edge Computing Example [8].

ple, using the cloud's hardware and operating system. Here, a cloud provider offers middleware, development tools, operating systems, hardware and other business tools for end-users or customers.

**IaaS** "Infrastructure as a Service", refers to providing infrastructure, such as computing, storage, and cloud technology to the end-users. Here, end-users can scale down or scale up their computational platform as they want.

Several derived models were recently proposed, such are HaaS (Hardware as a Service), but their developments are considered out of scope for this report. In all cases, Figure 3 illustrates the available Cloud service models. Furthermore, Cloud technologies lead to several benefits for customers: 1) no need to employ anyone to maintain the computer, 2) no need to update the hardware and 3) minimisation of overall processing costs. At the same time, this model exhibits some drawbacks as well, which are: 1) slow network connectivity and internet traffic which make cloud technologies slower 2) security concerns, and 3) local data which can be stored in foreign countries, not subjected to the same data protection regulation as the GDPR in European countries.

Figure 3: Overview of the main Cloud Computing deployment models [10].

It follows that even though Cloud Computing may be considered faster for data processing or computation, data transfer is a major bottleneck for Big Data analytics workflows. This is particularly relevant for IoT [11, 12, 13] environments, which tend to produce huge volume of data across interdisciplinary disciplines like technology, healthcare, environment, and transportation. In this case, a novel distributed and large-scale computing paradigm is required to effectively treat and analyse such large-scale dataset in a timely manner. That is how the Edge Computing model was introduced, with as its heart the idea to bring data storage and compute power closer to the device or data source where it is mostly needed. More specifically, the Edge Computing paradigm allows computing resources and appli-

cation services to be distributed along the communication path, via decentralised computing infrastructures organised to treat in a hierarchical fashion the data analytic workflow. The hierarchy coupled with the distribution of computing capabilities aims at solving the bandwidth bottleneck identified for general Cloud architectures.

## 4. Edge Computing Architecture and Technology

### 4.1. Edge Computing Architecture

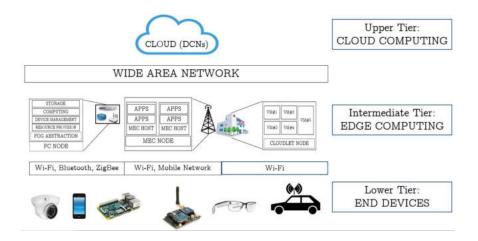

Edge Computing architectures are traditionally composed by several layers playing an essential role in the successful execution of the associated paradigm. Figure 4 and Table 1 show the schematic architecture and characteristics of an Edge Computing environment, which are thus categorised according to the following deployment models:

- Cloudlet Computing. This refers to computing resources (small cluster) connected via WLAN to the end-users. In general, it can be considered as a "data centre in a box" which provides support (computing and storage) to the end-users over the WLAN network. Cloudlet Computing is based on three layers: the component layer, the node layer, and the cloudlet layer. This is designed to have higher bandwidth, thus lowering the latency for the applications.

- Fog Computing, a decentralised computing resource that can be placed anywhere between the cloud and the end-users. It is based on the so-called Fog Computing Nodes (FCNs) [14]. All of these FCNs are heterogeneous, including switches, routers, and access points. FCNs heterogeneous environment facilitates the devices at different protocol layers and non-IP based technologies to communicate between the FCNs and the end device. These FCNs are hidden for the end-users, thus ensuring security.

- *Multi-access Edge Computing (MEC)*, which refers to implementing Edge Computing within the Radio Access Network to reduce the latency. Formally known as Mobile Edge Computing, it is an ETSI-defined network architecture located closer to the Radio Network Controller or macro base station. The edge orchestrator organises the MEC, provides network information about load and capacity, and offers information to the end-users about their location and network information.

- *IoT* (Internet of Things) contains a large set of devices and sensors that produce a huge volume of data. These also exchange the data through a modern communication network and monitor and control the infrastructure. Typically, end-users at the Edge use the IoT devices and sensors.

Figure 4: Overview of Edge Computing Architectures [15].

|                         | Edge Computing Architecture Layer |             |             |                   |

|-------------------------|-----------------------------------|-------------|-------------|-------------------|

| Characteristics         | IoT                               | Edge        | Fog         | Cloud             |

| Deployment              | Distributed                       | Distributed | Distributed | Centralised       |

| Components              | Physical devices                  | Edge Nodes  | Fog Nodes   | Virtual resources |

| Location awareness      | Aware                             | Aware       | Aware       | Aware             |

| Computational Limits    | Limited                           | Limited     | Limited     | Unlimited         |

| Storage Limits          | Very limited                      | Limited     | Limited     | Unlimited         |

| Data Source             |                                   | Process     | Process     | Process           |

| Distance to data source | The source                        | The nearest | Near        | Far               |

| Response time           | No response time                  | The fastest | Fast        | Slow              |

| Nodes count             | The largest                       | Very large  | Large       | Small             |

Table 1: Main characteristics and functionality within Edge Computing Architectures [15].

In general, Edge Computing involves complex or heterogeneous architecture. It is hard to ultimately make use of this complex architecture for some Edge Computing applications. However, many software platforms help to make Edge Computing work correctly and effectively. The following list provides more description about some of the important software platforms in Edge Computing.

#### 4.2. Virtualisation

Virtualisation refers to an abstraction of an Operating System (OS), computing resources, storage device, and/or network devices. Especially in computing, the term *virtualisation* often implies the reference to the creation of a Virtual Machine (VM) managed by a *hypervisor*, a middleware responsible for providing an abstraction or emulation layer from the hardware. The hardware running the hypervisor is called the host whereas all emulated VMs running inside them are referred to as *guests*. In practice, there exists two types of hypervisors illustrated in Figure 5b:

- 1. *Type-1 (Native) hypervisors* are running directly on hardware (hence often referred to as bare metal hypervisors). Xen [16], VMware ESXI [17] or Hyper-V [18] are examples of such hypervisors.

- 2. *Type-2 (Hosted) hypervisors* require a host operating system whose capabilities are used in order to perform virtualisation operations and emulations. Examples of such hypervisors includes KVM [19] or VirtualBox [20].

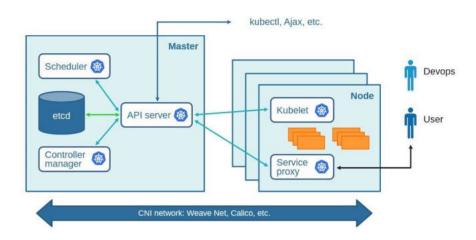

With the advent of Docker [21] in 2013, another virtualisation model became popular: *container*-based virtualisation, which does not emulate an entire computer. Instead, the host operating system is providing most features to the container software in order to isolate processes from other processes and containers as depicted in Figure 5a. It is indeed a built-in feature of the Linux kernel to provide such isolation capabilities to isolate processes. Other operating systems may provide similar mechanisms, such as FreeBSD's jails [22]. This allows to design lightweight images - a code-based file that includes all libraries and dependencies, which makes this technology particularly suitable for the development of Edge Computing architectures. Because there is no full emulation of hardware, software running in containers has to be compliant with the host system's kernel and CPU architecture. Furthermore, since containers are so small, there are usually hundreds of them loosely coupled together, which is why *container orchestration frameworks* such as Red Hat OpenShift [23] and Kubernetes [24] (depicted in the next section) are used to provision and manage them.

Virtualisation is of course considered in other components of large-scale computing infrastructures relevant for Edge Computing. At the level of the network backbone, network virtualisation comes under the form of *Software-Defined Networks* (SDN), a manageable and cost-effective approach to enable dynamic, programmatically efficient network configuration in order to improve network performance and monitoring. This makes this type of architecture suitable for the high-bandwidth and dynamic nature of the applications that run on top of Edge Computing devices. SDN decouples the forwarding process of network packets (or data plane) inherent to the physical network, from the routing and control process. Often composed by one or more controllers, the control plane is generally referred to as "brain of the network", where most of the crucial decisions are made as illustrated in Figure 6. Openflow [25] and OpenvSwitch [26] are a well-known Open-Source implementation frameworks in SDN network virtualisation.

#### 4.3. Resource Management and Edge Orchestration

Resource management is crucial in terms of allocating computing resources, CPU, memory, storage, and network on standard traditional HPC settings. Especially for Edge Computing, the energy resource is very important. For example, a mobile user does not want to recharge his or her smartphone often, and also some sensors should not need

(a) Container Environments [7].

(b) Type-1 (Bare-Metal) or Type-2 (Hosted) Hypervisors [7].

Figure 5: Main types of virtualisation frameworks.

Figure 6: A high-level architecture overview of SDN [7].

to be charged frequently. In particular, for the Edge analytics, developers should know how much power is needed for the specific application and how data could be pulled/pushed from the device. Eventually, this kind of problem falls into the optimisation problem of scheduling and workload placement. In general, there are some important requirements for Edge platforms management, summarised in Table 2.

The orchestration of Edge Computing resources is thus quite challenging and still a work in progress. We can cite several frameworks for which an adaptation to the management of Edge devices is on-going:

- Generic container orchestration middlewares such as OpenShift [23] (Red Hat) or Kubernetes [24] (Google).

Figure 7 depicts the generic working model architecture. In particular, Kubernetes features the following characteristics:

- It is automatically bin-packing the containers based on the containers' resources and other constraints. For example, in Edge Computing, the computing resource of the Edge might host multiple users and applications. It is important to schedule them in an optimised way to use the Edge resources to minimise the energy consumption and achieve lower latency.

- Kubernetes has a feature of self-healing, which is a significant factor for Edge Computing. For example, when there is a sudden failure or nodes are killed, users do not want to get notified; instead, the service and application should be recovered/migrated to other resources.

- Another feature of Kubernetes is load balancing, which is based on the IP address and a single DNS name for a set of containers.

| Requirement         | Description                                                                                           |

|---------------------|-------------------------------------------------------------------------------------------------------|

| Scalability         | Ability to address a large number of Edge devices of different type and capabilities with appropriate |

|                     | deployment and communicating protocol.                                                                |

| Security            | Privacy preserving for security tokens and support for integrity checks within the infrastructure     |

| Heterogeneity       | Support for a high degree of heterogeneity within hardware/software                                   |

| Volatility          | Support for volatile availability and mobile hardware/software components                             |

| Data Protection     | GDPR Compliance, ensure all data is kept locally and on-the-fly encrypted                             |

| Infrastructure Per- | Very low latency, lightweight publish-subscribe network protocol as MQTT [27]. High performance       |

| formance            | containerised resources with fast (Zero-touch) provisioning allowing easy system upgrades             |

| Application Porta-  | Unified architecture view via MEC compliance enabling Function as a Service (FaaS) capabilities       |

| bility              |                                                                                                       |

| Data Analytics      | Supports for Data Management and Data Analytics Pipeline Engine.                                      |

Table 2: General requirement for Edge devices management and orchestration.

Figure 7: A high-level architecture overview of Kubernetes [7].

Among other initiatives, the KubeEdge [28] project is dedicated to making an open platform, which is built upon Kubernetes and provides fundamental infrastructure support for network, application deployment and metadata synchronization between Cloud and Edge architectures. To enable fast and lightweight communications between all the Edge devices, i.e. from low power single board computers to full-capable servers and HPC compute nodes), the MQTT [27] protocol implemented over the Mosquitto [29] message broker service is used.

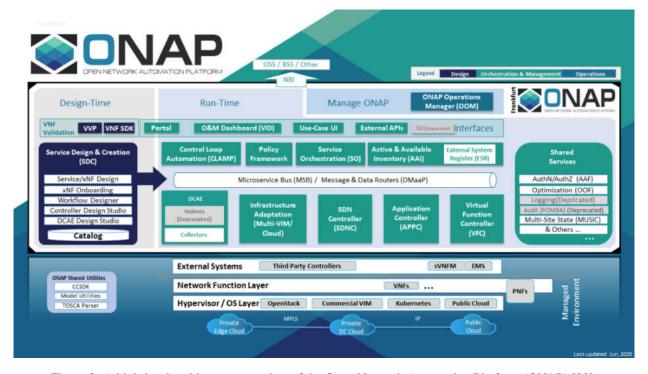

• ONAP (Open Network Automation Platform) [30], a comprehensive platform for orchestration, management, and automation of network and Edge Computing services for network operators, cloud providers, and enterprises. More tailored to MEC management and allowing to orchestrate physical and virtual network functions synchronously. The ONAP project provides a unified operating framework for vendor-agnostic, policy-driven service design, implementation, analytics and lifecycle management for large-scale workloads and services. A high-level overview of the ONAP platform architecture is proposed in Figure 8.

#### 4.4. Developing Platform enabling Data Analytics for Edge Computing

Edge Analytics refers to processing the data of the crucial application and service entirely or partially. For example, in healthcare, monitoring the older adults at home using the ECG (ElectroCardioGram) or EEG (ElectroEncephalo-Gram), it is better to perform the data processing at home, and only if something abnormal happens send out the data to the hospital or the doctor. Thus, the data flow between home and hospital is minimised, which reduces the data failure between two points. Not only the healthcare system can leverage this model, nowadays, but electronic devices which are connected to IoT networks can also process the data and exchange the essential information. For example, such devices can be drones, robots, cameras, and sensors, etc.

As mentioned in Table 2, data analytics capabilities are required within the development tools and platforms, enabling an Edge Computing infrastructure. If the Edge appliances cannot process the data, then it has to send the data to the cloud. In this context, there are several open-source tools available as software platforms supporting the data analytics pipeline engine for Edge Computing.

Figure 8: A high-level architecture overview of the Open Network Automation Platform (ONAP) [30].

- TensorFlow [31], a framework that supports Machine Learning (ML)/AI computations. It also supports a wide range of architectures, including, CPUs, GPUs, embedded and mobile systems. TensorFlow supports different programming languages, such as C/C++, Python, and Java. It even supports heterogeneous capability (CPU+GPU) computation.

- OpenCV [32], a software platform that supports computer vision computations. It has more than 250 optimised algorithms that can detect and recognise, i.e. faces, identify objects, classify human actions in videos, etc. OpenCV also provides an API for Java, C/C++, and Python.

- Apache Edgent [33], an analytic tool that runs on the Edge device based on the Apache incubator project. It allows to store fewer data on the Edge device and limits the amount of data to be transmitted to the analytic server. Apache Edgent supports the Java API, and it makes Edge systems to be more autonomous.

- TensorFlow Lite [34], an open-source and designed for on-device inference, used for the AI/ML/ Deep Learning (DL) applications. In particular, it is used for image classification, object detection, and text classification.

- Apache MXNet [35], supporting a distributed computing platform with up to eight programming language bindings. Libraries in MXNet enables use-cases in computer vision and natural language problems. It is also has a rich eco-system that supports the other AI/ML/DL libraries for Edge Computing, i.e. MXFusion [36], Keras-MXNet [37], and InsightFace [38].

## 5. Latest Trends in Edge Computing

Edge Computing will have to deal with ongoing developments in AI/ML/DL to do computational analysis and data processing. To do such complex arithmetic calculations, powerful embedded devices are required to perform these calculations are needed. There are lots of embedded hardware solutions available nowadays to support these requirements. Here we explain selected embedded architectures that will make Edge Computing more efficient and optimised.

#### 5.1. Nvidia Jetson