## SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

# INFRA-2007-2.2.2.1 - Preparatory phase for 'Computer and Data Treatment' research infrastructures in the 2006 ESFRI Roadmap

### **PRACE**

### Partnership for Advanced Computing in Europe

Grant Agreement Number: RI-211528

D8.3.2

Final technical report and architecture proposal

#### Final

Version: 1.0

Author(s): Ramnath Sai Sagar (BSC), Jesus Labarta (BSC), Aad van der Steen (NCF), Iris

Christadler (LRZ), Herbert Huber (LRZ)

Date: 25.06.2010

### **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-2115                                         | 528                           |

|---------------|-----------------------------------------------------------------|-------------------------------|

|               | Project Title: Final technical report and architecture proposal |                               |

|               | Project Web Site: http                                          | p://www.prace-project.eu      |

|               | Deliverable ID: : <                                             | D8.3.2>                       |

|               | Deliverable Nature: Report                                      |                               |

|               | Deliverable Level:                                              | Contractual Date of Delivery: |

|               | PU *                                                            | 30 / 06 / 2010                |

|               |                                                                 | Actual Date of Delivery:      |

|               |                                                                 | 30 / 06 / 2010                |

|               | EC Project Officer: Bernh                                       | nard Fabianek                 |

<sup>\* -</sup> The dissemination level are indicated as follows: PU - Public, PP - Restricted to other participants (including the Commission Services), RE - Restricted to a group specified by the consortium (including the Commission Services). CO - Confidential, only for members of the consortium (including the Commission Services).

### **Document Control Sheet**

|          | Title: : Final technical | report and architecture proposal |

|----------|--------------------------|----------------------------------|

| Document | <b>ID:</b> D8.3.2        |                                  |

|          | Version: 1.0             | Status: Final                    |

|          | Available at:            |                                  |

### **Document Keywords and Abstract**

| Keywords: | PRACE, HPC, Research Infrastructure                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract: | This document describes the activities in Work Package 8 Task 8.3 (WP8.3) updating and analysing results reported in D8.3.1 for the different WP8 prototypes. The document also suggests potential architectures for future machines, the level of performance we should expect and areas where research efforts should be dedicated. |

#### **Copyright notices**

© 2010 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract **RI-211528** for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

### **Table of Contents**

|      |          |                | ole Information Sheet                                       |     |

|------|----------|----------------|-------------------------------------------------------------|-----|

|      |          |                | reet                                                        |     |

|      |          | •              | and Abstract                                                |     |

|      |          |                |                                                             |     |

| List | of Figui | es             |                                                             | vi  |

| List | of Table | es             |                                                             | ix  |

| Refe | rences a | and Appli      | cable Documents                                             | . X |

|      |          |                |                                                             |     |

| 1    |          |                |                                                             |     |

| _    | 1.1      |                | l Structure of the Report                                   |     |

| 2    | WP8 n    |                | and Research Activities                                     |     |

| -    | 2.1      |                | 95                                                          |     |

|      |          | 2.1.1          | eOPACE                                                      |     |

|      |          | 2.1.2          | BAdW-LRZ/GENCI-CINES Phase1 (CINES Part)                    |     |

|      |          | 2.1.3          | BAdW-LRZ/GENCI-CINES Phase2 (LRZ Part)                      |     |

|      |          | 2.1.4          | Intel Many Integrated Core (MIC) architecture               |     |

|      |          | 2.1.5          | ClearSpeed-Petapath                                         |     |

|      |          | 2.1.6          | Hybrid Technology Demonstrator                              |     |

|      |          | 2.1.7          | Maxwell FPGA                                                |     |

|      |          | 2.1.8          | XC4-IO                                                      |     |

|      |          | 2.1.9          | SNIC-KTH                                                    |     |

|      |          | 2.1.10         | RapidMind                                                   | 13  |

|      | 2.2      | Research       | activities                                                  | 14  |

|      |          | 2.2.1          | PGAS language compiler                                      | 14  |

|      |          | 2.2.2          | Research on Power Efficiency                                |     |

|      |          | 2.2.3          | Parallel GPU                                                |     |

|      |          | 2.2.4          | Performance Predictions                                     |     |

| 3    | WP8 ev   |                | results                                                     |     |

|      | 3.1      | Performa       | nce experiments on prototype hardware                       |     |

|      |          | 3.1.1          | Reference performance                                       |     |

|      |          | 3.1.2          | Numerical issues                                            |     |

|      |          | 3.1.3          | Accelerated Programming Languages and Compilers             |     |

|      |          | 3.1.4          | FPGA experiments                                            |     |

|      |          | 3.1.5          | LRZ + CINES (Phase 1)                                       |     |

|      |          | 3.1.6          | LRZ + CINES (Phase 2)                                       |     |

|      |          | 3.1.7          | Intel MIC Architecture                                      |     |

|      |          | 3.1.8          | Petapath experiments                                        |     |

|      | 3.2      | •              | -6 - 6                                                      | 53  |

|      |          |                | MPI+OpenMP                                                  |     |

|      |          | 3.2.2          | MPI+CUDA                                                    |     |

|      | 2.2      | 3.2.3          | MPI + CellSs                                                |     |

|      | 3.3      |                | le Bandwidth                                                |     |

|      |          | 3.3.1<br>3.3.2 | Triads (RINF1) benchmark results (BAdW-LRZ)                 |     |

|      |          | 3.3.2<br>3.3.3 | Random Access Results                                       |     |

|      | 3.4      |                | Host to accelerator bandwidth (NCF)le Communication Network |     |

|      | 3.4      | 3.4.1          | eOPACE                                                      |     |

|      |          | 3.4.2          | BAdW-LRZ                                                    |     |

|      | 3.5      |                | nguages                                                     |     |

|      | 3.3      | 3.5.1          | Chapel experiments.                                         |     |

|      |          | 3.5.2          | Co-Array Fortran experiments                                |     |

|      |          | 3.5.3          | UPC Experiments                                             |     |

|      | 3.6      |                | : XC4-IO experiments                                        |     |

|      |          | 3.6.1          | Lustre Architecture                                         |     |

|      |          | 3.6.2          | Throughput tests                                            |     |

|      |          | 3.6.3          | File striping tests                                         |     |

|      |          | 3.6.4          | Tests on the Metadata device technology                     |     |

|      |          | 3.6.5          | Metadata server load tests                                  |     |

|      |          |                |                                                             |     |

|      | 3.6.6          | Parallel I/O libraries test                                  | 81  |

|------|----------------|--------------------------------------------------------------|-----|

|      | 3.6.7          | Preliminary tests on pNFS                                    |     |

|      | 3.6.8          | Conclusion                                                   |     |

| 3.7  |                | efficiency                                                   |     |

|      | 3.7.1          | The SNIC-KTH system                                          |     |

|      | 3.7.2          | PSNC results                                                 |     |

|      | 3.7.3          | STFC results                                                 |     |

|      | 3.7.4          | BAdW-LRZ results                                             |     |

| 3.8  |                | nance predictions                                            |     |

| 3.0  | 3.8.1          | Impact of basic system components                            |     |

|      | 3.8.2          | Non ideal node level parallelisation                         |     |

|      | 3.8.3          | Prediction for ICE                                           |     |

|      | 3.8.4          | ·                                                            |     |

|      |                | Prediction for BG/P                                          |     |

| 2.0  | 3.8.5          | General analysis                                             |     |

| 3.9  |                | ry of conclusions                                            |     |

|      | 3.9.1          | Node/core performance: Accelerators vs. general purpose CPUs |     |

|      | 3.9.2          | Memory bandwidth                                             |     |

|      | 3.9.3          | Network bandwidth                                            |     |

|      | 3.9.4          | Hybrid                                                       |     |

|      | 3.9.5          | I/O                                                          |     |

|      | 3.9.6          | Energy Efficiency                                            |     |

| Reco |                | ions for next generation Petascale machines                  |     |

| 4.1  | Foreseea       | able architectures                                           | 118 |

|      | 4.1.1          | General architecture                                         | 118 |

|      | 4.1.2          | Some straw man examples                                      | 120 |

| 1.2  | Relevan        | t issues                                                     | 121 |

|      | 4.2.1          | Power and Energy efficiency                                  | 121 |

|      | 4.2.2          | Programming models and compilers                             |     |

|      | 4.2.3          | Accelerators                                                 |     |

|      | 4.2.4          | Network Interconnects                                        |     |

|      | 4.2.5          | Memory bandwidth and latency                                 |     |

|      | 4.2.6          | Memory per node and core                                     |     |

|      | 4.2.7          | Performance tools                                            |     |

|      | 4.2.8          | Load balance                                                 |     |

|      | 4.2.9          | Runtime Systems                                              |     |

|      | 4.2.10         | Resilience                                                   |     |

|      |                |                                                              |     |

|      | 4.2.11         | Arithmetic                                                   |     |

|      | 4.2.12         | Benchmarks                                                   |     |

|      | 4.2.13         | Libraries                                                    | 127 |

|      | 4.2.14         | Applications                                                 |     |

|      |                | d Final remarks                                              |     |

| Anne |                |                                                              |     |

| 6.1  | Benchm         | arks                                                         |     |

|      | 6.1.1          | EuroBen – Synthetic Benchmarking Suite                       | 130 |

|      | 6.1.2          | High Performance LINPACK                                     | 130 |

|      | 6.1.3          | Intel MPI Benchmark (IMB)                                    |     |

|      | 6.1.4          | Triads (RINF1) Benchmark                                     |     |

|      | 6.1.5          | Random Access Benchmark                                      |     |

|      | 6.1.6          | APEX Benchmark                                               |     |

|      | 6.1.7          | STREAM Benchmark                                             |     |

|      | 6.1.8          | IOR Benchmark                                                |     |

|      | 0.1.8<br>6.1.9 | CPU Burn-in                                                  |     |

|      | 0.1-17         |                                                              |     |

|      | 6.1.10         | CacheBench                                                   |     |

|      | 6.1.11         | IOzone                                                       |     |

| 5.2  |                | tions                                                        |     |

|      | 6.2.1          | GADGET                                                       |     |

|      | 6.2.2          | <i>NAMD</i>                                                  |     |

|      | 6.2.3          | RAxML                                                        |     |

|      | 6.2.4          | DL-POLY                                                      | 135 |

# **List of Figures**

| Figure 1: QPACE Architecture                                                                    | 4  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2: Prototype configuration and integration layout                                        | 6  |

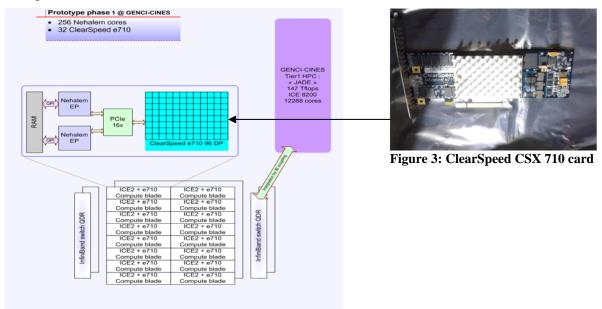

| Figure 3: ClearSpeed CSX 710 card                                                               | 6  |

| Figure 4: Hybrid system prototype installed at BAdW-LRZ                                         | 7  |

| Figure 5: Scheme of Intel MIC architecture prototype                                            |    |

| Figure 6: x86-based core and associated system blocks.                                          | 8  |

| Figure 7: Block diagram of vector processing unit (VPU)                                         | 8  |

| Figure 8: Clearspeed-Petapath prototype                                                         | 8  |

| Figure 9: Overview of HMPP components                                                           | 9  |

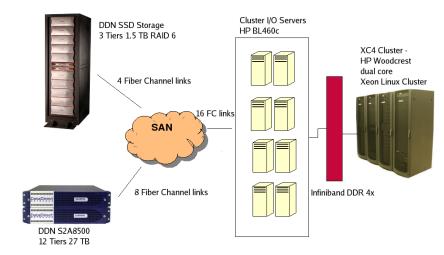

| Figure 10: I/O & File System Prototype architectural scheme.                                    | 11 |

| Figure 11: Prototype's motherboard                                                              | 12 |

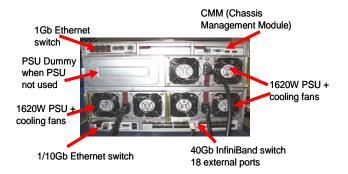

| Figure 12: 10-blade chassis                                                                     | 12 |

| Figure 13: Chassis features                                                                     | 12 |

| Figure 14: Rack of prototype                                                                    | 13 |

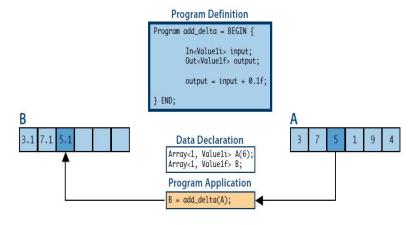

| Figure 15: Data-stream processing in RapidMind                                                  | 13 |

| Figure 16: Connection diagram                                                                   |    |

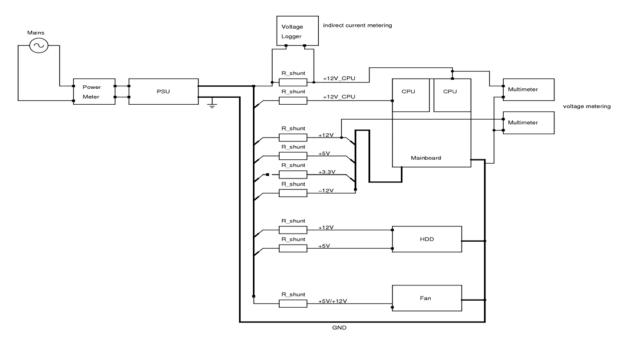

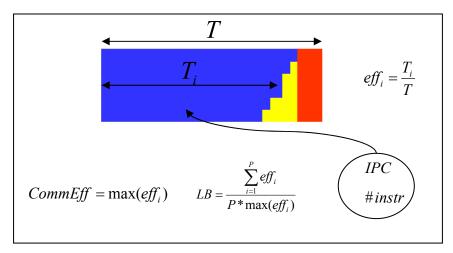

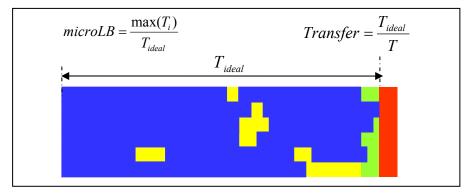

| Figure 17: Gant diagram and efficiency model                                                    | 20 |

| Figure 18: Model including microscopic load balance and serialization                           | 20 |

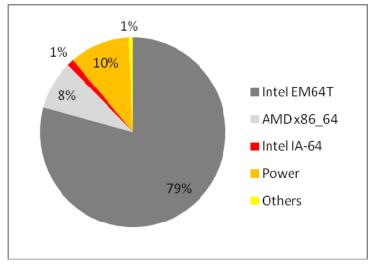

| Figure 19: Processor family share in the November 2009 Top500 list                              |    |

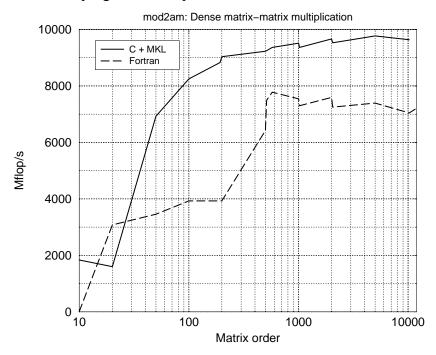

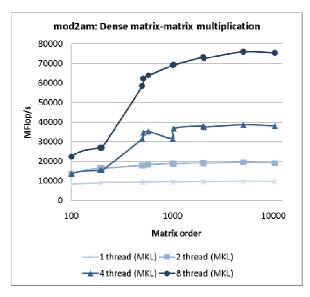

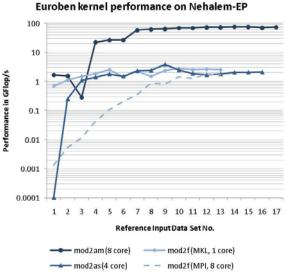

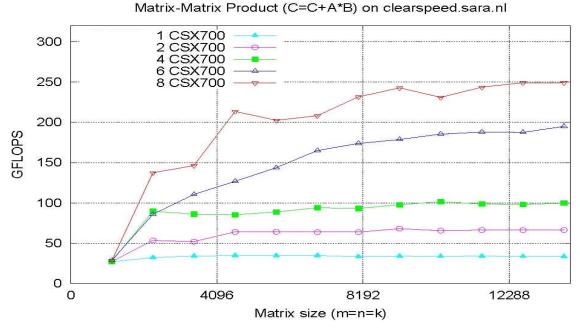

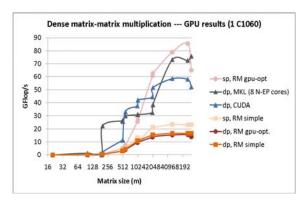

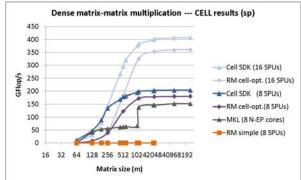

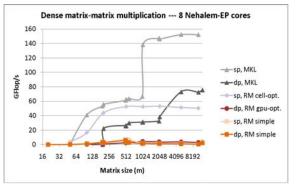

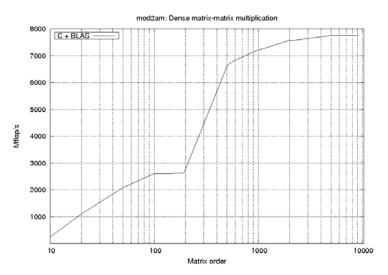

| Figure 20: Reference performance of dense matrix-matrix multiplication                          |    |

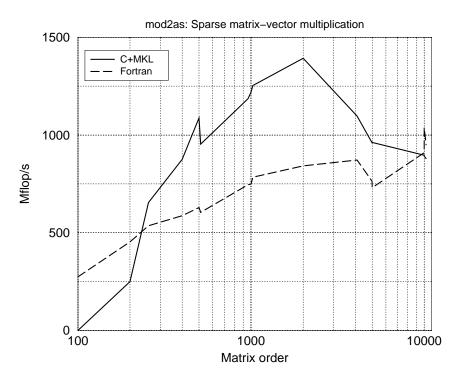

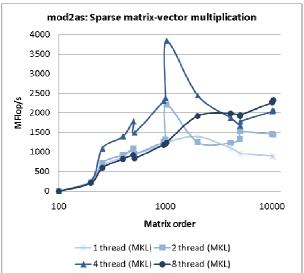

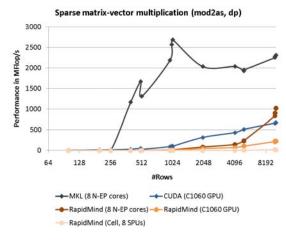

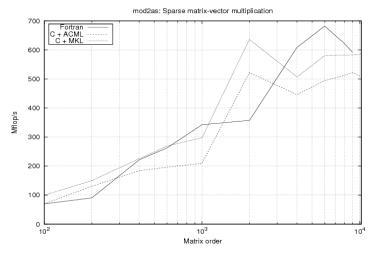

| Figure 21: Reference performance of sparse matrix-vector multiplication                         | 23 |

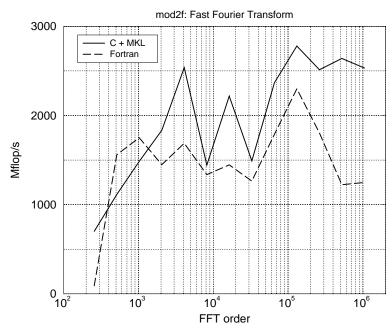

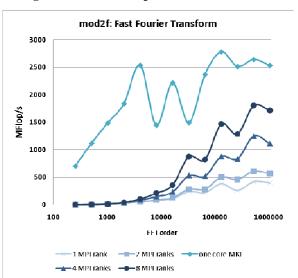

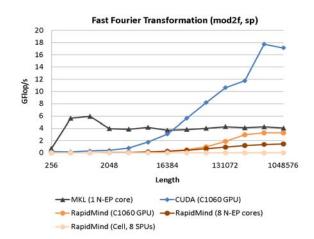

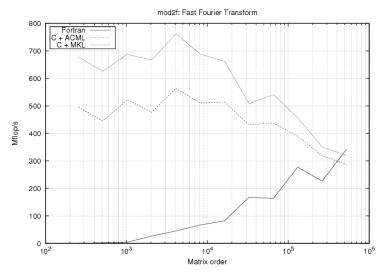

| Figure 22: Reference performance of 1-D complex-to-complex FFT                                  |    |

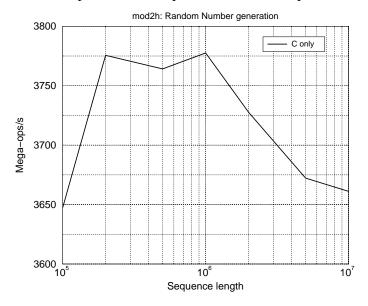

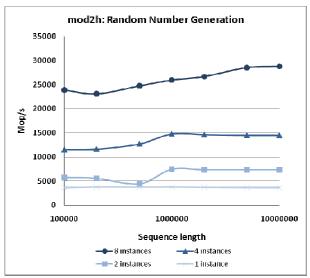

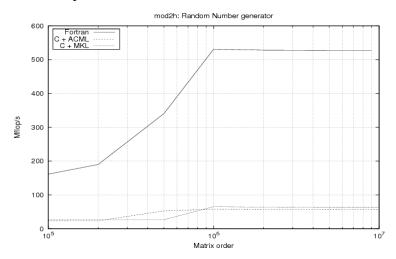

| Figure 23: Reference performance of the random number generator                                 |    |

| Figure 24: Reference performance of dense matrix-matrix and sparse matrix-vector multiplication |    |

| Figure 25: Reference performance of FFT and random number generation                            |    |

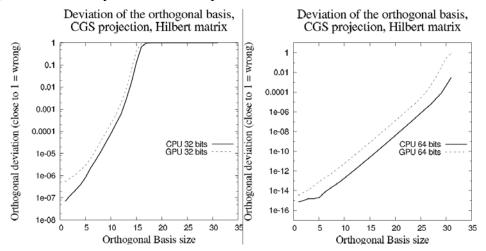

| Figure 26: Precision of the CGS Arnoldi Projection of a 10240 square Hilbert matrix             |    |

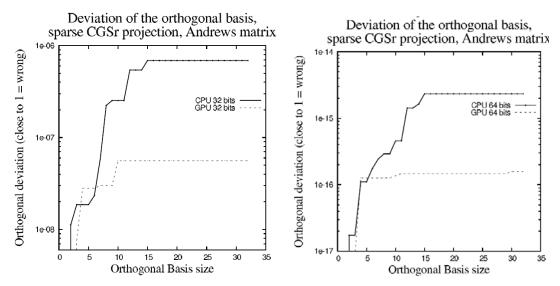

| Figure 27: Precision of the sparse CGSr process on sparse Andrews matrix                        |    |

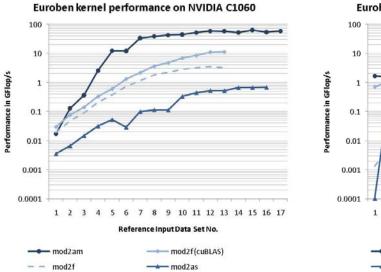

| Figure 28: Comparison of the CUDA kernels on nVIDIA c1060 GPUs                                  |    |

| Figure 29: Comparison of the MKL kernels on Nehalem-EP                                          |    |

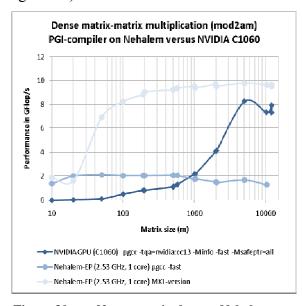

| Figure 30: mod2am on a single core Nehalem vs. nVIDIA C1060                                     |    |

| Figure 31: mod2as on a single core Nehalem vs. nVIDIA C1060                                     |    |

| Figure 32: Example illustrating the richness of expression offered by HMPP's set of directives  |    |

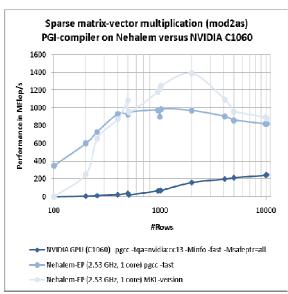

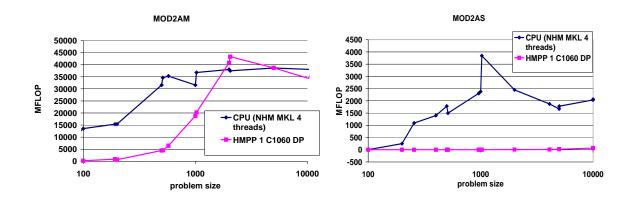

| Figure 33: Nehalem-EP single socket mod2am performance versus nVIDIA C1060 using HMPP           |    |

| Figure 34: Nehalem-EP single socket mod2as performance versus nVIDIA C1060 using HMPP           |    |

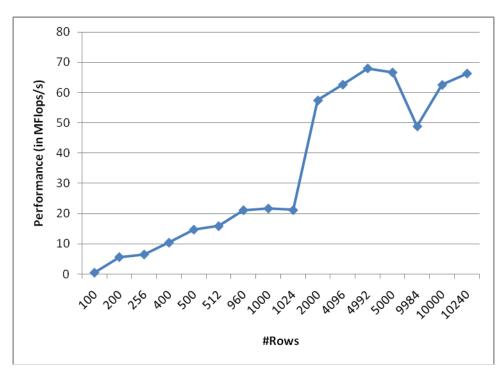

| Figure 35: Performance of mod2am using CellSs on Maricel                                        |    |

| Figure 36: Performance of mod2as using CellSs on Maricel                                        | 33 |

| Figure 37: Performance of mod2am using GPUSs on nVIDIA Tesla                                    |    |

| Figure 38: Performance of mod2am on Nehalem EP using SMPSs                                      | 34 |

| Figure 39: Performance of mod2as on Nehalem using SMPSs                                         |    |

| Figure 40: Performance of mod2am using ClearSpeedSs on the ClearSpeed-Petapath prototype        |    |

| Figure 41: RapidMind results for mod2am (GPU)                                                   |    |

| Figure 42: RapidMind results for mod2am (CELL)                                                  |    |

| Figure 43: RapidMind results for mod2am (x86)                                                   |    |

| Figure 44: RapidMind results for mod2as                                                         |    |

| Figure 45: RapidMind results for mod2f                                                          |    |

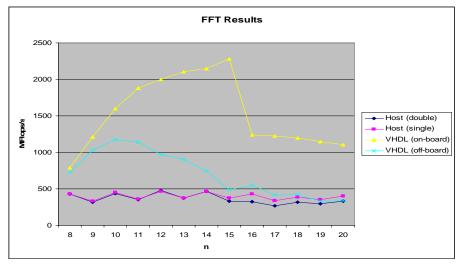

| Figure 46: Performance of mod2f for different problem sizes                                     |    |

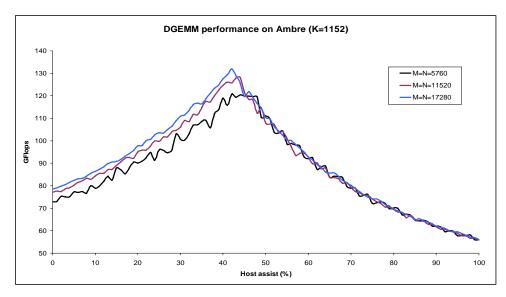

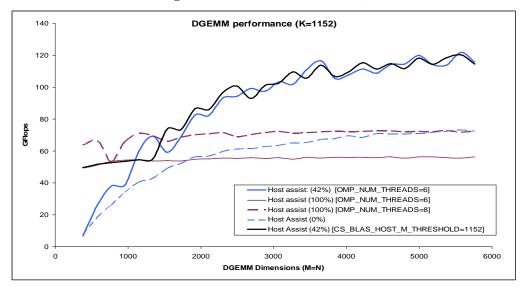

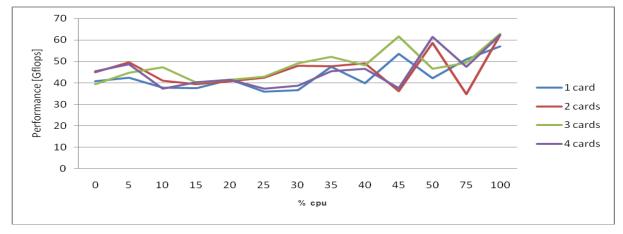

| Figure 47: CPU/CSX710 (K = 1152)                                                                |    |

| Figure 48: CPU / CX710 across matrix sizes                                                      |    |

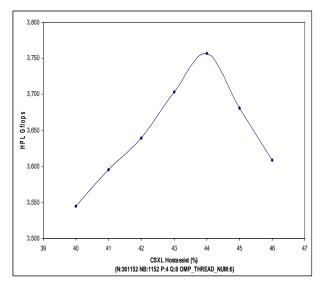

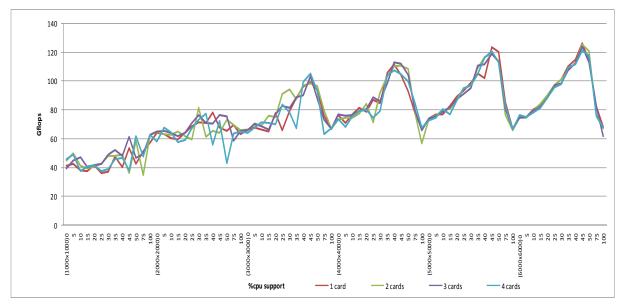

| Figure 49: HPL / 32 node + CSXL with varying hostassist                                         |    |

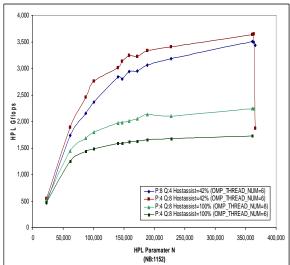

| Figure 50: HPL / 32 node + CSXL with varying memory size                                        |    |

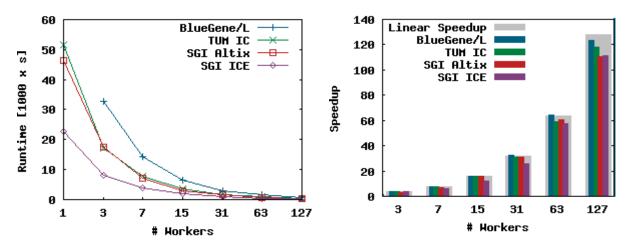

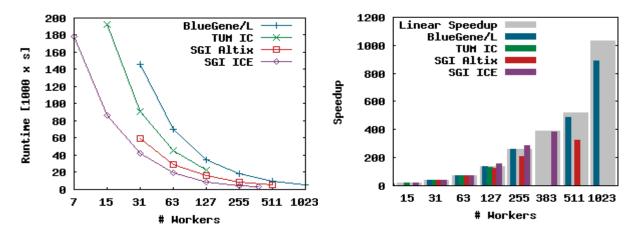

| Figure 51: Runtimes and Speedups for synthetic DNA dataset with 50 sequences                    |    |

| Figure 52: Runtimes and Speedups for synthetic DNA dataset with 250 sequences                   |    |

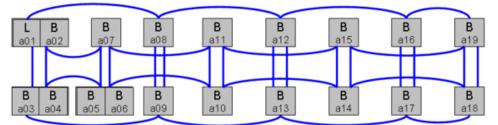

| Figure 53: Network topology of 9728-core SGI Altix4700 system HLRB II at BAdW-LRZ               |    |

|                                                                                                 |    |

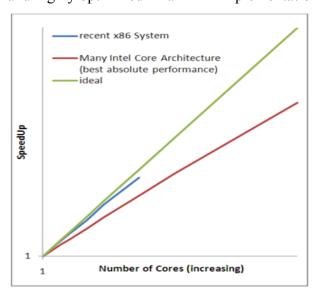

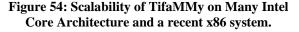

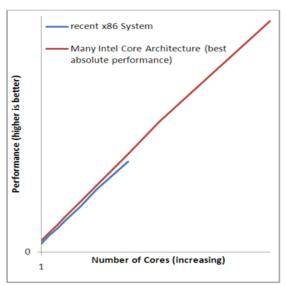

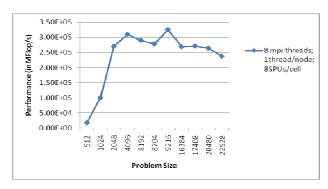

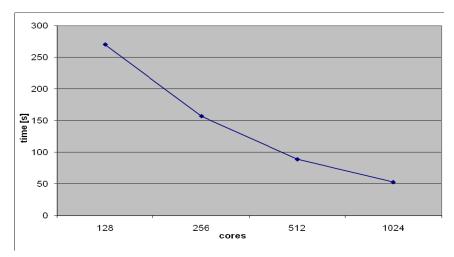

| Figure 54: Scalability of TifaMMy on Many Intel Core Architecture and a recent x86 system           |    |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 55: Absolute performance of TifaMMy on Many Intel Core Architecture and a recent             |    |

| system                                                                                              |    |

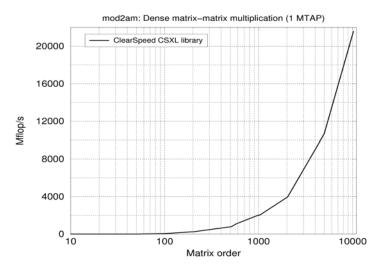

| Figure 56: Performance of mod2am on 1 MTAP                                                          | 51 |

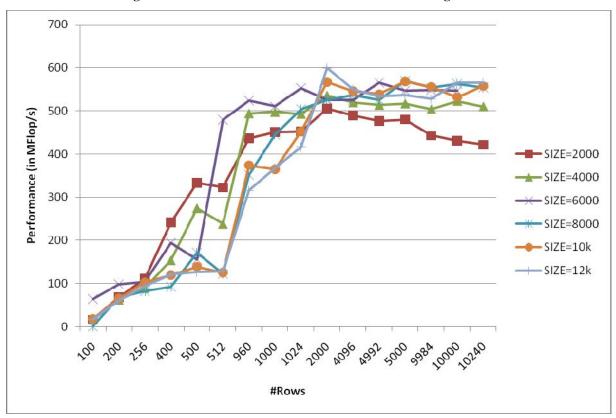

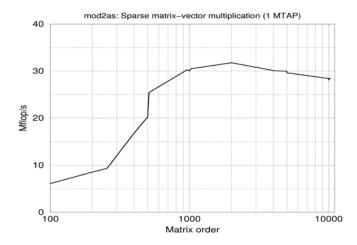

| Figure 57: Performance of mod2as on 1MTAP                                                           | 52 |

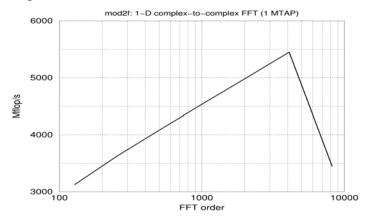

| Figure 58: Performance for mod2f on 1MTAP                                                           | 52 |

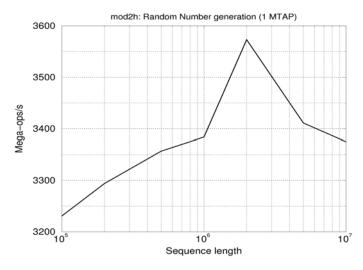

| Figure 59: Performance for mod2h on 1 MTAP                                                          | 53 |

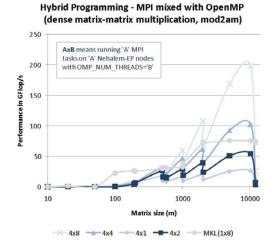

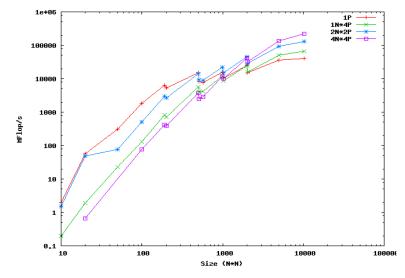

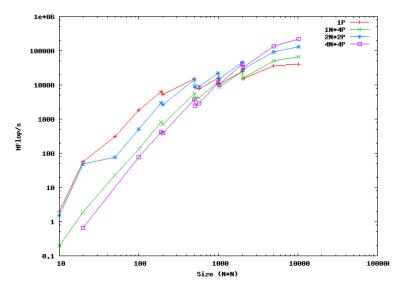

| Figure 60: Hybrid MPI+OpenMP results for mod2am                                                     |    |

| Figure 61: Hybrid MPI+OpenMP results for mod2as                                                     | 54 |

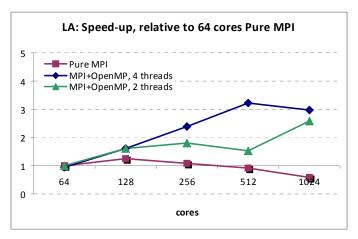

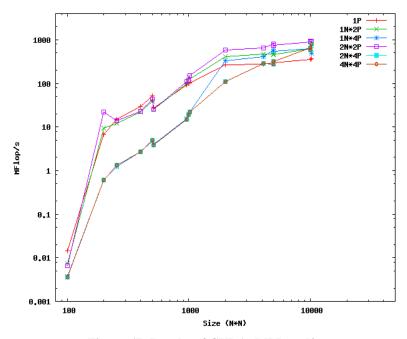

| Figure 62: Speedup of the Linear Algebra subtask of a Car-Parrinello simulation                     | 54 |

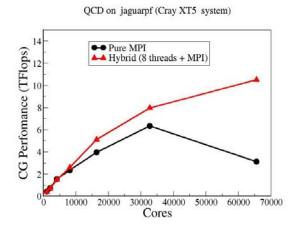

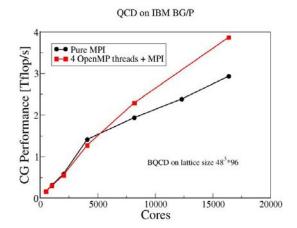

| Figure 63: BQCD scaling results on Cray XT5 system                                                  |    |

| Figure 64: BQCD scaling results on IBM BlueGene/P                                                   |    |

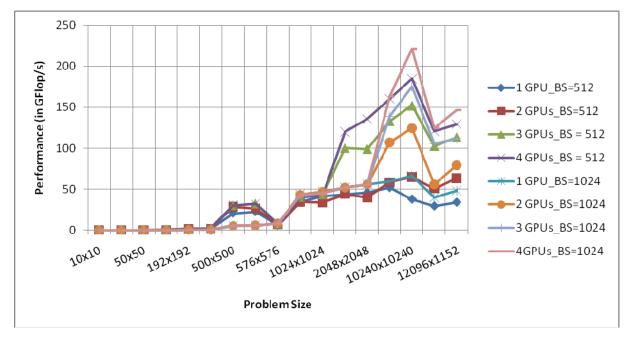

| Figure 65: Results of CUDA+MPI mod2am with a reference mxm routine                                  |    |

| Figure 66: Results of CUDA+MPI mod2am with a CUBLAS mxm routine                                     |    |

| Figure 67: Results of CUDA+MPI mod2as                                                               |    |

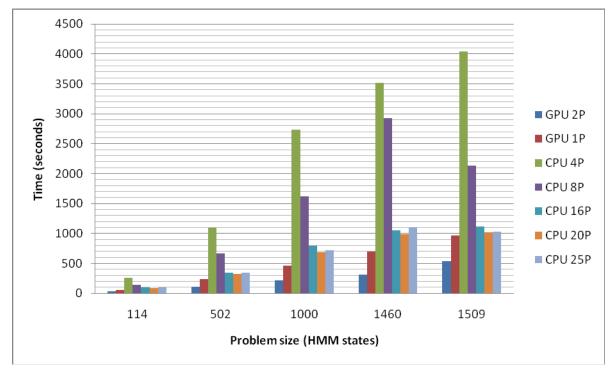

| Figure 68: Runtime of CPU vs. GPU HMMER                                                             |    |

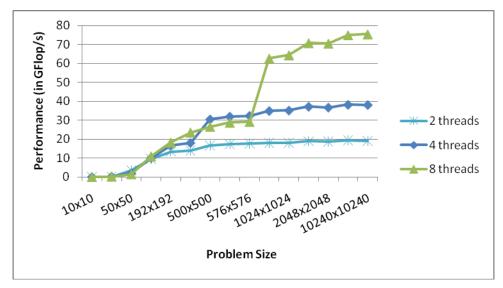

| Figure 69: Performance of mod2am with MPI+CellSs on Maricel.                                        |    |

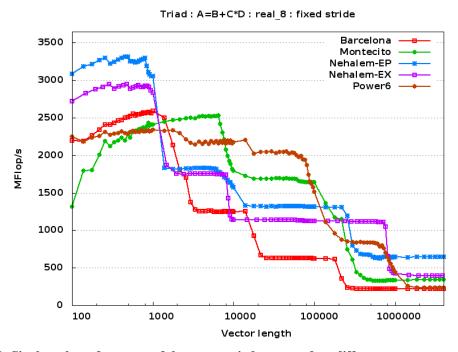

| Figure 70: Single task performance of the vector triad measured on different processor architecture |    |

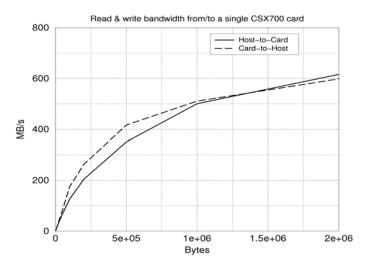

| Figure 71: Measured host-card bandwidth 1 MTAP                                                      |    |

| Figure 72: QPACE network processor                                                                  |    |

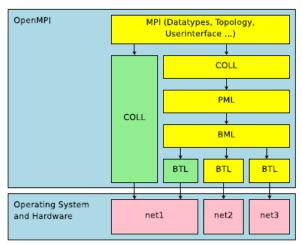

| Figure 73: Open MPI Modular Component Architecture                                                  |    |

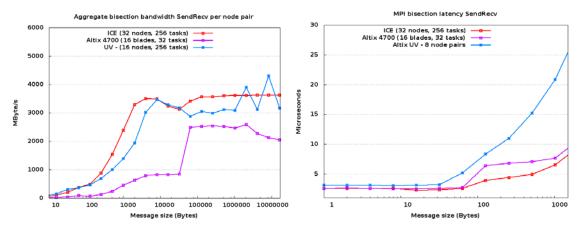

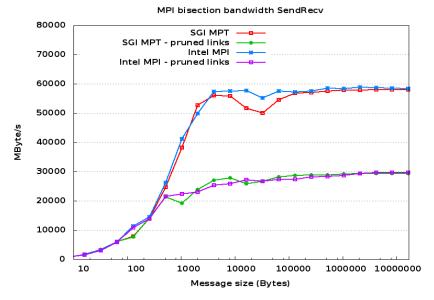

| Figure 74: MPI bisection bandwidths (left figure) and MPI send receive latencies (right figure)     |    |

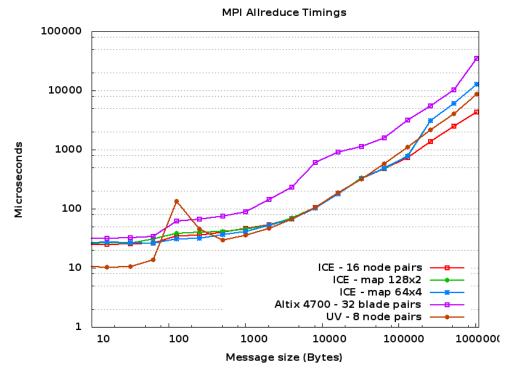

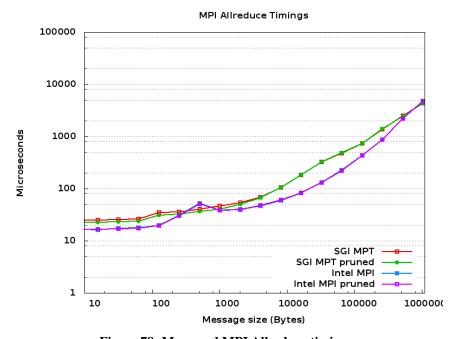

| Figure 75: MPI Allreduce timings for SGI Altix4700, ICE and UltraViolet                             |    |

| Figure 76: Measured Altix ICE MPI bisection bandwidths                                              |    |

| Figure 77: Measured Altix ICE MPI bisection latencies.                                              |    |

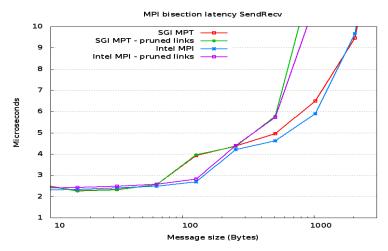

| Figure 78: Measured MPI Allreduce timings                                                           |    |

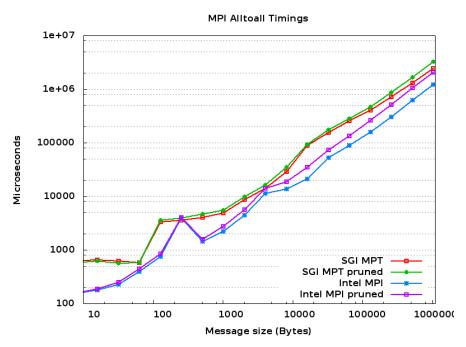

| Figure 79: Measured MPI Alltoall timings                                                            |    |

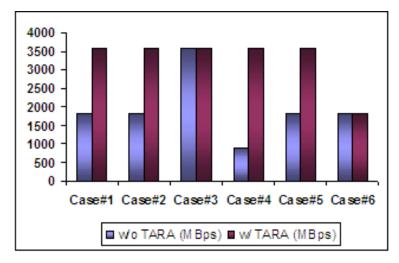

| Figure 80: Measured MPI send/receive link bandwidths with and without traffic aware routing         |    |

| Figure 81: Cray XT5 (left) and Cray X2 (right) processing nodes                                     |    |

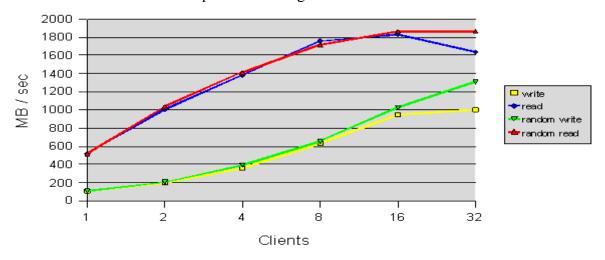

| Figure 82: Lustre throughput performances                                                           |    |

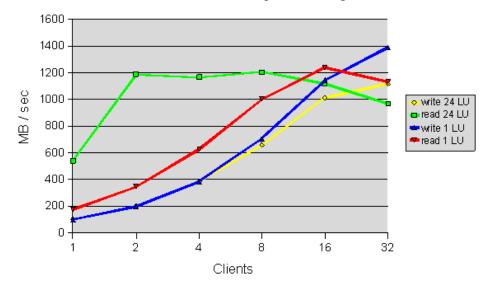

| Figure 83: Bandwidth (in MB/s) for Read and Write operations with different striping count          |    |

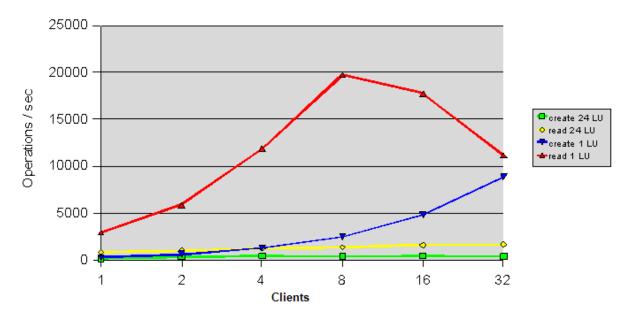

| Figure 84: Performance (I/O ops/s) with different stripe count with a large number of files         |    |

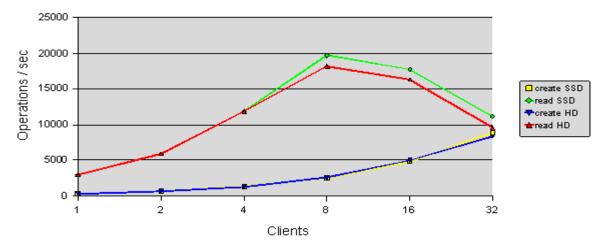

| Figure 85: Comparison between SSDs and magnetic Hard Disks (I/O ops/s)                              |    |

| Figure 86: Comparison between SSDs and magnetic Hard Disks (% cpu utilization of the MDS)           |    |

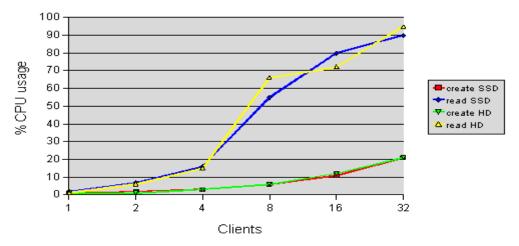

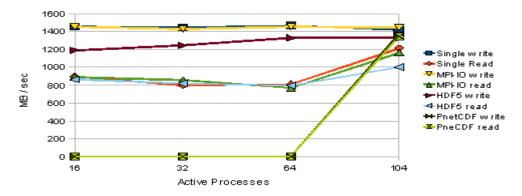

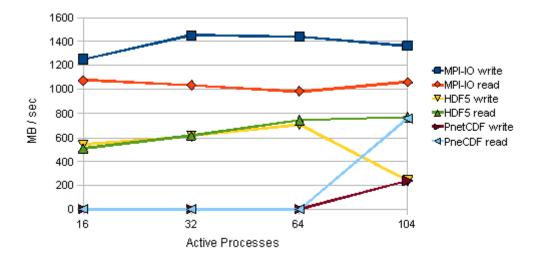

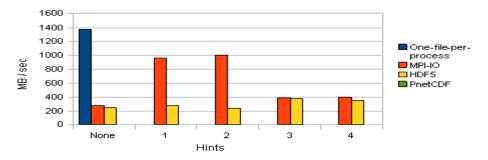

| Figure 87: IOR results (MB/s) using individual communication                                        |    |

| Figure 88: IOR results (MB/s) using collective communication.                                       |    |

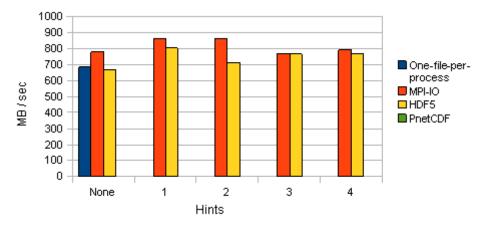

| Figure 89: RAMSES Test (MB/s) reads                                                                 |    |

| Figure 90: RAMSES Test (MB/s) writes                                                                |    |

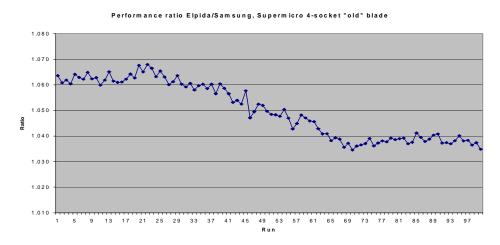

| Figure 91: Performance ratio of Elpida/Samsung, Supermicro 4-socket blade                           |    |

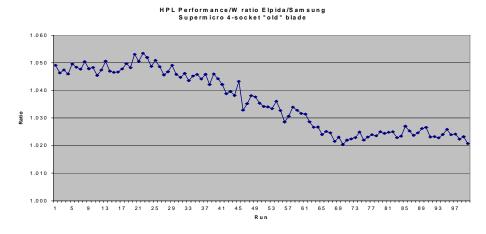

| Figure 92: Performance/W ratio for Elpida/Samsung Supermicro 4-socket blade                         |    |

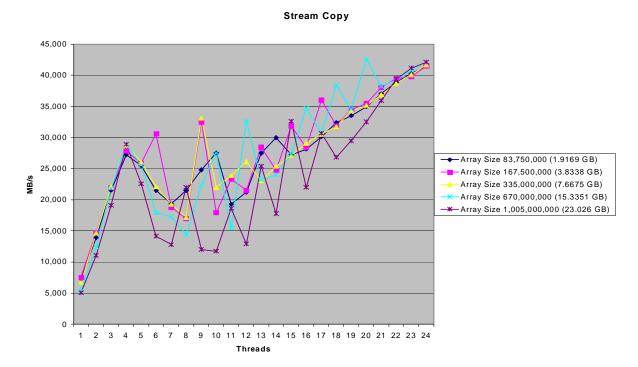

| Figure 93: Stream Copy                                                                              |    |

| Figure 94: Near linear relation between tasks and updates for StarRandomAccess                      |    |

| Figure 95: Relation between tasks and updates for MPIRandomAccess                                   |    |

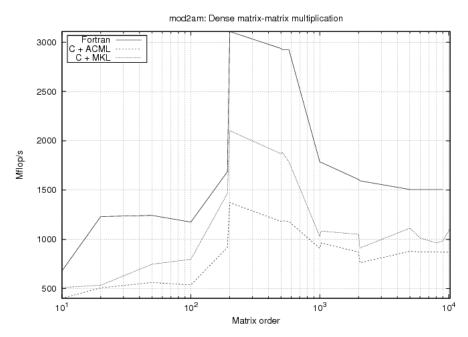

| Figure 96: Comparison of the performance of the dense matrix-matrix multiplication kernel for       |    |

| different implementations: Fortran, C with ACML and C with MKL                                      |    |

| Figure 97: Performance of the dense matrix-matrix multiplication with GotoBLAS2 libraries           |    |

| Figure 98: Performance of the sparse matrix-vector multiplication                                   |    |

| Figure 99: of the random number generator kernel                                                    |    |

| Figure 100: Performance of the fast Fourier transform kernel                                        |    |

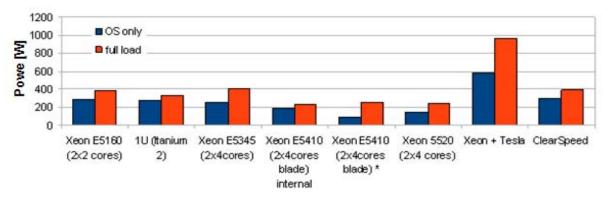

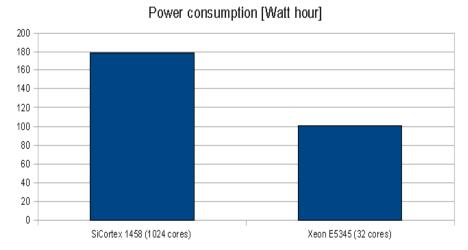

| Figure 101: Summary of Power consumption of tested servers                                          |    |

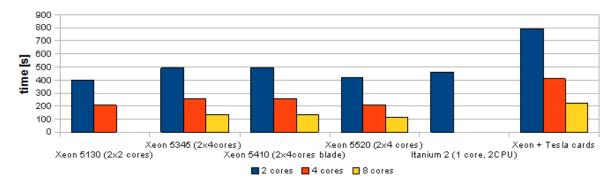

| Figure 102: NAMD execution times                                                                    |    |

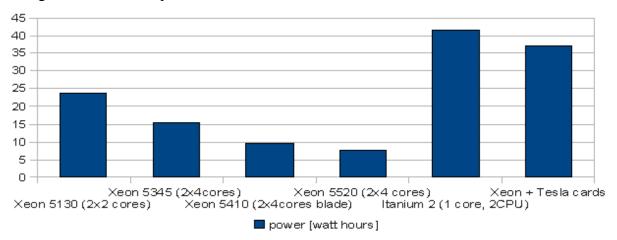

| Figure 103: Power consumption - NAMD appoal benchmark                                               |    |

| Figure 104: Gromacs run time on SiCortex                                                            |    |

| Figure 105: Power consumption of SiCortex and Xeon E5345                                            |    |

| Figure 106: Performance reported by the dgemm application                                           |    |

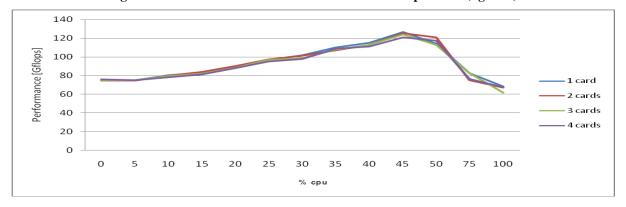

| Figure 107: Performance for the 1k x 1k matrix multiplication (dgemm)                               | 97 |

| Figure 108: Performance for the 6k x 6k matrix multiplication                                     | 97    |

|---------------------------------------------------------------------------------------------------|-------|

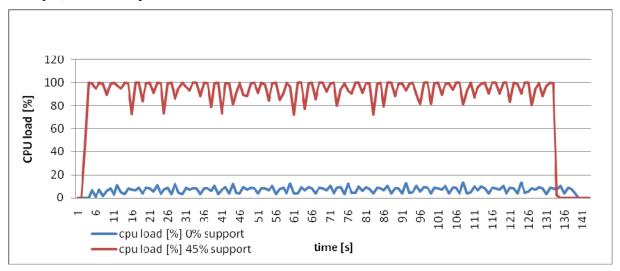

| Figure 109: The CPU load while running the four instances of the dgemm test                       | 98    |

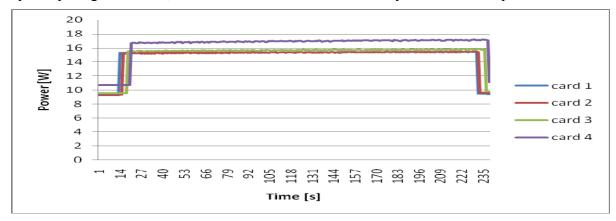

| Figure 110: Power consumption reported by the cards while running a single dgemm application      | 98    |

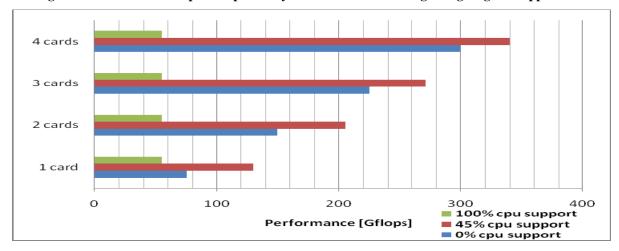

| Figure 111: Computational performance                                                             | 98    |

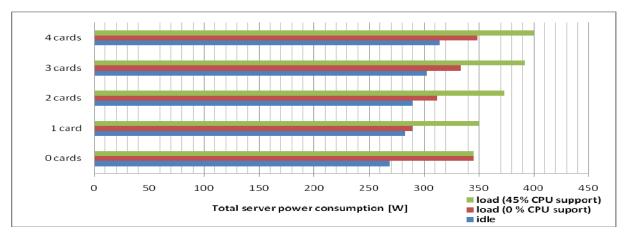

| Figure 112: Server power consumption                                                              | 99    |

| Figure 113: Performance/power ratio of the test server                                            | 99    |

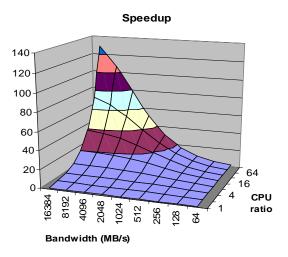

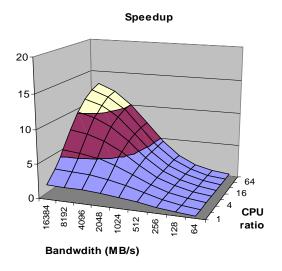

| Figure 114: Impact of node performance and Interconnect bandwidth (in MB/s) for 64 processes      | . 103 |

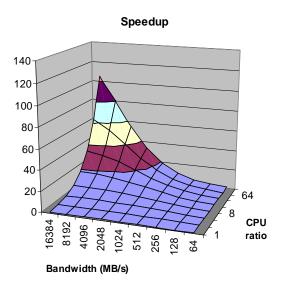

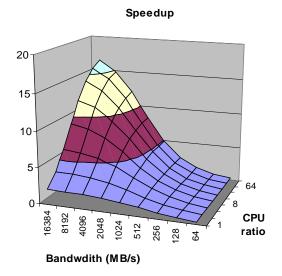

| Figure 115: Impact of node performance and Interconnect bandwidth (in MB/s) for 128 processes.    |       |

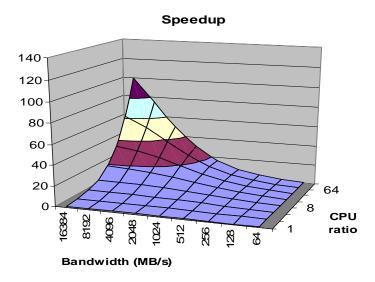

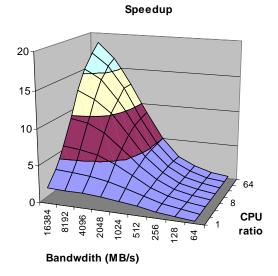

| Figure 116: Impact of node performance and Interconnect bandwidth (in MB/s) for 256 processes.    |       |

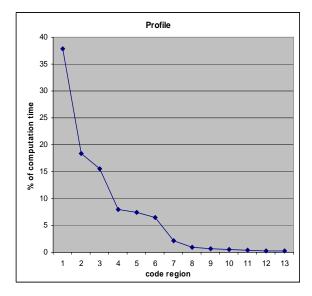

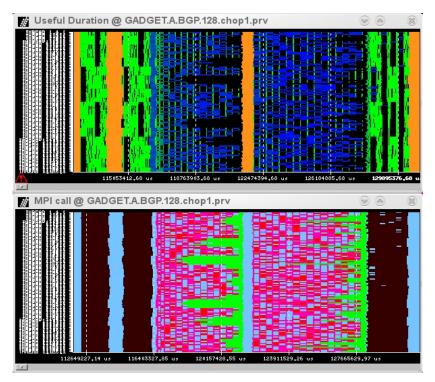

| Figure 117: Profile of computation regions in GADGET for 128 processors in MareNostrum            |       |

| Figure 118: Impact of bandwidth and acceleration factor applied to major computation bursts       | rep-  |

| resenting 93.67 % of the original computation time                                                |       |

| Figure 119: Impact of bandwidth and acceleration factor applied to major computation bursts       |       |

| resenting 97.49 % of the original computation time                                                |       |

| Figure 120: Impact of bandwidth and acceleration factor applied to major computation bursts       | rep-  |

| resenting 99.11 % of the original computation time                                                |       |

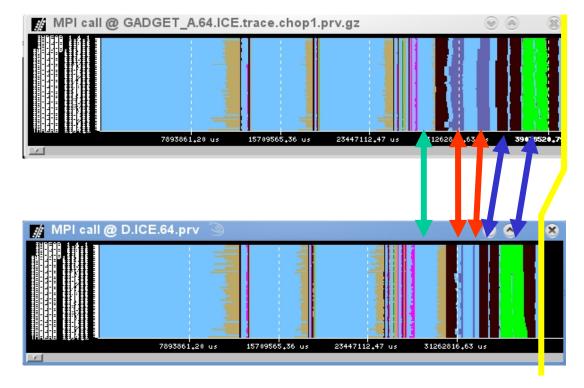

| Figure 121: MPI calls for real run (top) and prediction (bottom) for 128 processes on ICE         | . 106 |

| Figure 122: MPI calls for real run (top) and prediction (bottom) for 128 processes on ICE         | . 107 |

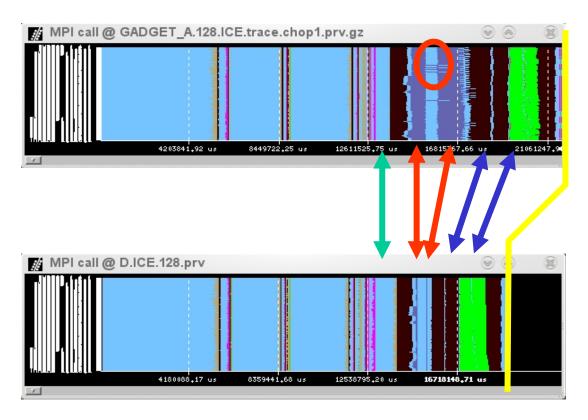

| Figure 123: MPI calls for real run (top) and prediction (bottom) for 128 processes on Jugene      | . 108 |

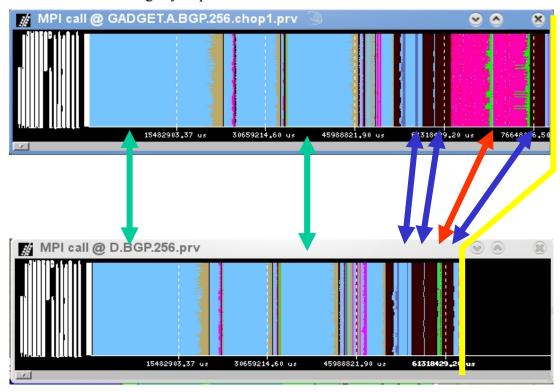

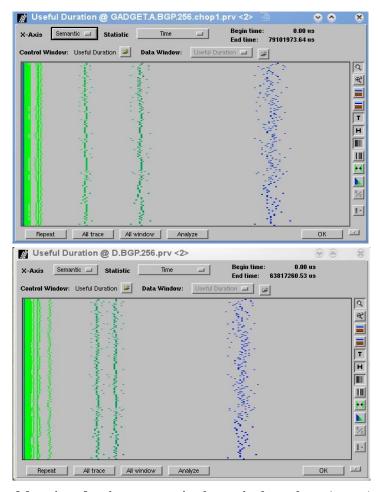

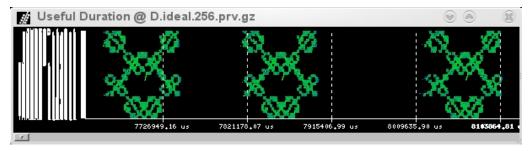

| Figure 124: Histogram of duration of major computation bursts in the real run (on top) and predic | ction |

| (bottom)                                                                                          | . 109 |

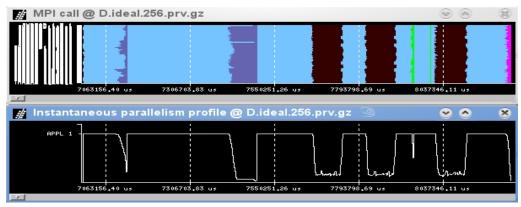

| Figure 125: Zoom of duration of computation phases (top) and MPI calls (bottom) in exchange re    | gion  |

|                                                                                                   |       |

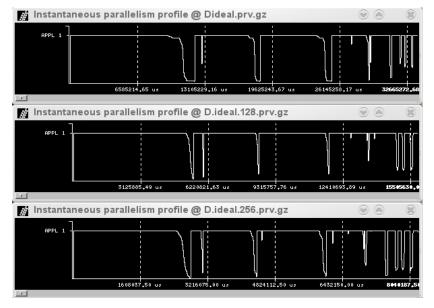

| Figure 126: Instantaneous parallelism profile for 64, 128 and 266 processor runs on ICE           | . 111 |

| Figure 127: Instantaneous efficiency in the communication phase of the 256 processor trace from   |       |

| assuming ideal interconnect                                                                       |       |

| Figure 128: Serialized computations pattern                                                       | . 112 |

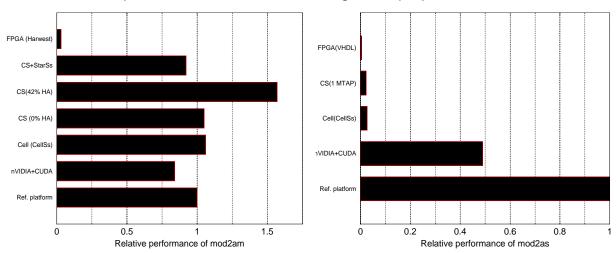

| Figure 129: Performance relative to reference platform of mod2am                                  |       |

| Figure 130: Performance relative to reference platform of mod2as                                  | . 112 |

| Figure 131: Performance relative to reference platform of mod2f                                   | . 113 |

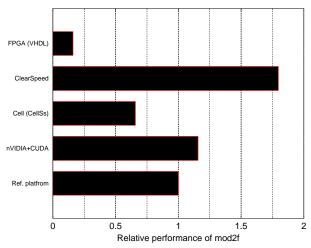

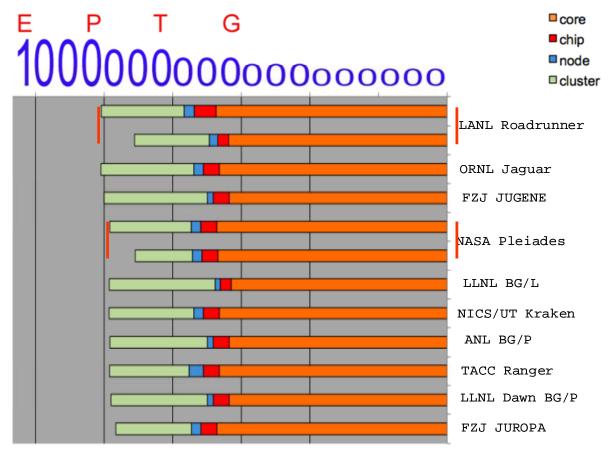

| Figure 132: current structure and performance of top machines in Top500 list                      | . 118 |

| Figure 133: Possible evolution of supercomputer dimensioning                                      |       |

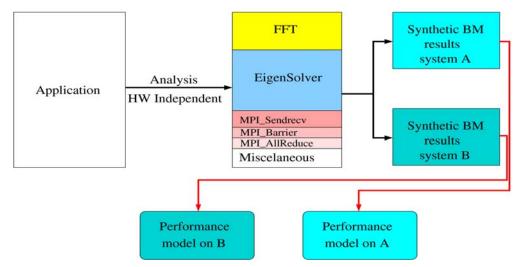

| Figure 134: Kernel-based performance modeling                                                     |       |

|                                                                                                   |       |

### **List of Tables**

| Table 1: Hardware used in the RapidMind experiments.                                           | 35     |

|------------------------------------------------------------------------------------------------|--------|

| Table 2: mod2am performance results                                                            |        |

| Table 3: mod2am performance results                                                            | 38     |

| Table 4: mod2f performance results                                                             | 39     |

| Table 5: mod2h performance results                                                             | 40     |

| Table 6: Measured execution time of 256-core GADGET runs                                       | 46     |

| Table 7: Memory bandwidth and spatial degradation factors of different processor platforms     | 59     |

| Table 8: Measured random access memory latencies of different processor architectures          | 60     |

| Table 9: MPI send/receive benchmark results.                                                   | 64     |

| Table 10: Measured barrier latencies                                                           | 67     |

| Table 11: Influence of different MPI versions and network pruning on execution time of GADGE   | ET. 68 |

| Table 12: Test system configurations and roadmap                                               |        |

| Table 13: STREAM benchmark results for the CAF compiler                                        | 73     |

| Table 14: CAF STREAM results (GB/s) on X2                                                      |        |

| Table 15: Impact of alternate image mapping configurations on a CAF code execution             |        |

| Table 16: Two equivalent alternatives to distribute the iterations for array arr between the   | hreads |

| according to data locality                                                                     | 75     |

| Table 17: Summary of experiences with CAF and UPC compilers available as part of the           |        |

| framework on the Cray XT5 platform (options added since the previous release are highlighted). |        |

| Table 18: Power consumption of powered off servers                                             |        |

| Table 19: Xeon 5130 server - internal power consumption                                        |        |

| Table 20: NAMD, STMV benchmark, 500 steps                                                      |        |

| Table 21: LINPACK power efficiency on different architectures                                  |        |

| Table 22: Prediction and error with respect to actual iteration time on the ICE prototype      |        |

| Table 23: Prediction and error with respect to actual iteration time on the Jugene prototype   |        |

| Table 24: Global performance model for GADGET                                                  |        |

| Table 25: Point-to-point performance                                                           |        |

| Table 26: MPI performance of collective calls                                                  |        |

| Table 27: STREAM Benchmark Kernels                                                             | 132    |

#### **References and Applicable Documents**

- [1] <u>http://www.prace-project.eu</u>

- [2] D8.3.1 Technical Component Assessment and Development Report

- [3] D8.1.4 Signing of AHTP contract

- [4] D8.2.2 Architectural specifications from user requirements

- [5] D2.7.2 Final report on selection of prototypes

- [6] D2.7.2-Addendum Report on selection of 2<sup>nd</sup> prototypes

- [7] D5.4 Report on the Application Benchmarking Results of Prototype Systems

- [8] D6.6 Report on Petascale Software Libraries and Programming Models

- [9] CAPS Entreprise <a href="http://www.caps-entreprise.com/index.php">http://www.caps-entreprise.com/index.php</a>

- [10] HARWEST Compiling Environment (HCE): <a href="http://www.ylichron.it/index.php">http://www.ylichron.it/index.php</a>

- [11] Paraver: http://www.bsc.es/plantillaA.php?cat\_id=485

- [12] Dimemas: <a href="http://www.bsc.es/plantillaA.php?cat\_id=475">http://www.bsc.es/plantillaA.php?cat\_id=475</a>

- [13] EuroBen: http://www.euroben.nl/

- [14] CUDA Zone: http://www.nvidia.com/object/cuda home.html

- [15] Efficient Sparse Matrix-Vector Multiplication on CUDA" by Nathan Bell and Michael Garland http://www.nvidia.com/object/nvidia research pub 001.html

- [16] RapidMind developer site, <a href="https://developer.rapidmind.com/sample-code/matrix-multiplication-samples/rm-sgemm-gpu-5938.zip">https://developer.rapidmind.com/sample-code/matrix-multiplication-samples/rm-sgemm-gpu-5938.zip</a>

- [17] http://hmmer.janelia.org/

- [18] <a href="http://mpihmmer.org/">http://mpihmmer.org/</a>

- [19] NAMD Input set: http://www.ks.uiuc.edu/Research/namd/utilities/apoa1.tar.gz

- [20] James C. Phillips, Rosemary Braun, Wei Wang, James Gumbart, Emad Tajkhorshid, Elizabeth Villa, Christophe Chipot, Robert D. Skeel, Laxmikant Kale, and Klaus Schulten. Scalable molecular dynamics with NAMD. Journal of Computational Chemistry, 26:1781-1802, 2005. <a href="http://www.ks.uiuc.edu/Research/namd/">http://www.ks.uiuc.edu/Research/namd/</a>

- [21] HPL High-Performance LINPACK, http://www.netlib.org/benchmark/hpl/

- [22] "Evaluation of ClearSpeed Accelerators for HPC", I. N. Kozin, STFC technical report DL-TR-2009-1, <a href="http://www.cse.scitech.ac.uk/disco/publications/DLTR-2009-001.pdf">http://www.cse.scitech.ac.uk/disco/publications/DLTR-2009-001.pdf</a>

- [23] Gilles Kempf, Aad J. van der Steen, Christian Caremoli, Wei-Ying Thang: Simulation of Scientific Programs on Parallel Architectures, HPCN Conference, Brussels, 1996.

- [24] http://software.intel.com/en-us/articles/intel-mpi-benchmarks/

- [25] http://icl.cs.utk.edu/projectsfiles/hpcc/RandomAccess

- [26] https://ftg.lbl.gov/ApeX/ApeX.shtml

- [27] http://www.cs.virginia.edu/stream/

- [28] http://users.bigpond.net.au/CPUburn/

- [29] www.cs.utk.edu/~mucci/DOD/cachebench.ps

- [30] http://www.iozone.org/docs/IOzone msword 98.pdf

- [31] V. Springel, "The cosmological simulation code GADGET-2", Mon. Not. R. Astron. Soc. 364, 1105-1134 (2005).

- [32] http://www.mpa-garching.mpg.de/gadget/

- [33] JAMES C. PHILLIPS et al., "Scalable Molecular Dynamics with NAMD", 2005 Wiley Periodicals, Inc. J Comput Chem 26: 1781–1802, 2005

- [34] Alexandros Stamatakis, Michael Ott, and Thomas Ludwig: "RAxML-OMP: An Efficient Program for Phylogenetic Inference on SMPs". In Proceedings of 8th International Conference on Parallel Computing Technologies (PaCT2005), Volume 3606 of Lecture Notes in Computer Science, 288-302, Springer Verlag, September 2005.

- [35] http://www.cse.scitech.ac.uk/ccg/software/DL POLY/

- [36] GROMACS: <a href="http://www.gromacs.org/">http://www.gromacs.org/</a>

- [37] M. Allalen, M. Brehm and H. Stüben, Performance of quantum chromodynamics (QCD) simulations on the SGI Altix 4700, COMPUTATIONAL METHODS IN SCIENCE AND TECHNOLOGY 14(2), 69-75 (2008).

- [38] <a href="http://arxiv.org/pdf/0911.2174">http://arxiv.org/pdf/0911.2174</a>

- [39] Green 500 List: <a href="http://www.green500.org/lists/2009/11/top/list.php">http://www.green500.org/lists/2009/11/top/list.php</a>

- [40] Matrix Market: <a href="http://math.nist.gov/MatrixMarket/">http://math.nist.gov/MatrixMarket/</a>

- [41] I. Christadler, V. Weinberg, RapidMind: Portability across Architectures and its Limitations, to appear in: Facing the Multicore Challenge (Conference Proceedings), Heidelberg, 2010. http://arxiv.org/abs/1001.1902

- [42] D.Brinkers. 2010. Multigrid Algorithms on QPACE. Diploma Thesis, University of Erlangen-Nuremberg.

- [43] TifaMMy (TifaMMy isn't the fastest Matrix Multiplication, yet), http://tifammy.sourceforge.net,version 2.2.0.

- [44] Heinecke, A., Bader M.: Parallel matrix multiplication based on space-filling curves on shared memory multicore platforms, Proceedings of the 2008 ACM Research Computing Frontiers Conference and collocated workshops: MAW'08 and WRFT'08, p. 385-392, 2008.

- [45] Heinecke, A., Bader M.: Towards many-core implementation of LU decomposition using Peano Curves, Proceedings of the 2009 ACM Research Computing Frontiers Conference and co-located workshops: Proceedings of the combined workshops on UnConventional high performance computing workshop plus memory access workshop, p. 21-30, 2009.

- [46] OpenMP 3.0: The OpenMP API specification for parallel programming, http://openmp.org/, 2009.

- [47] Michael Abrash: A First Look at the Larrabee New Instructions (LRBni), Dr Dobbs Journal, April 1, 2009.

- [48] http://blogs.intel.com/technology/2010/05/an update on our graphics-rela.php

#### **List of Acronyms and Abbreviations**

ACF Advanced Computing Facility

ACML AMD Core Math Library

ADP Average Dissipated Power

AMD Advanced Micro Devices

APGAS Asynchronous PGAS (language)

API Application Programming Interface

APML Advanced Platform Management Link (AMD)

ASIC Application-Specific Integrated Circuit

ATI Array Technologies Incorporated (AMD)

BAdW Bayerischen Akademie der Wissenschaften (Germany)

BCO Benchmark Code Owner

BLAS Basic Linear Algebra Subprograms

BSC Barcelona Supercomputing Center (Spain)

BTL Byte Transfer Layer CAF Co-Array Fortran

CAL Compute Abstraction Layer CCE Cray Compiler Environment

ccNUMA cache coherent NUMA

CEA Commissariat à l'Energie Atomique (represented in PRACE by GENCI,

France)

CGS Classical Gram-Schmidt

CGSr Classical Gram-Schmidt with re-orthogonalisation

CINECA Consorzio Interuniversitario, the largest Italian computing centre (Italy)

CINES Centre Informatique National de l'Enseignement Supérieur (represented in

PRACE by GENCI, France)

CLE Cray Linux Environment CPU Central Processing Unit

CSC Finnish IT Centre for Science (Finland)

CSCS The Swiss National Supercomputing Centre (represented in PRACE by ETHZ,

Switzerland)

CSR Compressed Sparse Row (for a sparse matrix)

CSXL ClearSpeed math Library

CT Current Transformer

CUDA Compute Unified Device Architecture (NVIDIA)

DARPA Defense Advanced Research Projects Agency

DDN DataDirect Networks

DDR Double Data Rate

DGEMM Double precision General Matrix Multiply

DIMM Dual Inline Memory Module

DMA Direct Memory Access

DNA DeoxyriboNucleic Acid

DP Double Precision, usually 64-bit floating point numbers

DRAM Dynamic Random Access Memory

EC European Community

EESI European Exascale Software Initiative

EoI Expression of Interest

EP Efficient Performance, e.g., Nehalem-EP (Intel)

EPCC Edinburg Parallel Computing Centre (represented in PRACE by EPSRC,

United Kingdom)

EPSRC The Engineering and Physical Sciences Research Council (United Kingdom)

eQPACE extended QPACE, name of the FZJ WP8 prototype

ETHZ Eidgenössische Technische Hochschule Zuerich, ETH Zurich (Switzerland)

EX Expandable, e.g., Nehalem-EX (Intel)

FC Fiber Channel

FFT Fast Fourier Transform FHPCA FPGA HPC Alliance

FP Floating-Point

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FZJ Forschungszentrum Jülich (Germany)

GASNet Global Address Space Networking

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte

Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GDDR Graphic Double Data Rate memory

GENCI Grand Equipment National de Calcul Intensif (France)

GFlop/J Giga (=10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per Joule

GFlop/s Giga (=  $10^9$ ) Floating point operations (usually in 64-bit, i.e. DP) per second,

also GF/s

GHz Giga (=  $10^9$ ) Hertz, frequency =  $10^9$  periods or clock cycles per second

GigE Gigabit Ethernet, also GbE

GLSL OpenGL Shading Language

GNU GNU's not Unix, a free OS

GPGPU General Purpose GPU

GPU Graphic Processing Unit

GRU Global Register Unit (SGI, Altix UV)

GS Gram-Schmidt

GUI Graphical User Interface

GUPS Giga (= 10<sup>9</sup>) Updates Per Second

GWU George Washington University, Washington, D.C. (USA)

HBA Host Bus Adapter HCA Host Channel Adapter

HCE Harwest Compiling Environment (Ylichron)

HDD Hard Disk Drive HE High Efficiency

HLL High Level Language HMM Hidden Markov Model

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hewlett-Packard

HPC High Performance Computing; Computing at a high performance level at any

given time; often used synonym with Supercomputing

HPCC HPC Challenge benchmark, <a href="http://icl.cs.utk.edu/hpcc/">http://icl.cs.utk.edu/hpcc/</a>

HPCS High Productivity Computing System (a DARPA programme)

HPL High Performance LINPACK

HT HyperTransport channel (AMD)

HWA HardWare Accelerator

IB InfiniBand

IBA IB Architecture

IBM Formerly known as International Business Machines

ICE (SGI)

IDRIS Institut du Développement et des Ressources en Informatique Scientifique (re-

presented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IESP International ExasSale Project

IL Intermediate Language

IMB Intel MPI Benchmark

I/O Input/Output

IOR Interleaved Or Random IPC Instruction Per Cycle

IPMI Intelligent Platform Management Interface

IWC Inbound Write Controller

JSC Jülich Supercomputing Centre (FZJ, Germany) KB Kilo (=  $2^{10} \sim 10^3$ ) Bytes (= 8 bits), also KByte

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC, Sweden)

LB Load Balance

LBE Lattice Boltzmann Equation

LINPACK Software library for Linear Algebra

LLNL Lawrence Livermore National Laboratory, Livermore, California (USA)

LOV Logical Object Volume

LQCD Lattice QCD

LRZ Leibniz Supercomputing Centre (Garching, Germany)

LS Local Store memory (in a Cell processor)

LU Logical Unit

MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (=  $10^6$ ) Bytes (= 8 bits) per second, also MByte/s

MDT MetaData Target

MFC Memory Flow Controller

MFlop/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit, i.e. DP) per second,

also MF/s

MGS Modified Gram-Schmidt, also, ManaGement Server (Lustre file system)

MHz Mega (= 10<sup>6</sup>) Hertz, frequency = 10<sup>6</sup> periods or clock cycles per second

MIC Many Integrated Core (Intel)

MIPS Originally Microprocessor without Interlocked Pipeline Stages; a RISC proces-

sor architecture developed by MIPS Technology

MKL Math Kernel Library (Intel)

ML Maximum Likelihood

Mop/s Mega (=  $10^6$ ) operations per second (usually integer or logic operations)

MPI Message Passing Interface

MPP Massively Parallel Processing (or Processor)

MPT Message Passing Toolkit MRAM Magnetoresistive RAM

MTAP Multi-Threaded Array Processor (ClearSpead-Petapath)

MTBF Mean Time Between Failure

MUPS Mega (=  $10^6$ ) Updates Per Second

mxm DP matrix-by-matrix multiplication mod2am of the EuroBen kernels

NAND Logical operation NOT AND, also NAND flash memory, a type of memory

technology

NAS Network-Attached Storage

NCF Netherlands Computing Facilities (Netherlands)

NDA Non-Disclosure Agreement

NoC Network-on-a-Chip NFS Network File System

NIC Network Interface Controller

NUMA Non-Uniform Memory Access or Architecture

OFED OpenFabric Enterprise Distribution

OpenCL Open Computing Language

OpenGL Open Graphic Library

Open MP Open Multi-Processing

OS Operating System

OSS Object Storage Server

OST Object Storage Target

PBS Portable Batch System

PCIe Peripheral Component Interconnect express, also PCI-Express

PCI-X Peripheral Component Interconnect eXtended PCRAM Phase-change memory, also PCM or PRAM

PGAS Partitioned Global Address Space

PGI Portland Group, Inc.

pNFS Parallel Network File System POSIX Portable OS Interface for Unix

PPE PowerPC Processor Element (in a Cell processor)

PPL Parallel Programming Laboratory

PPU Power Processor Unit (in a Cell processor)

PRACE Partnership for Advanced Computing in Europe; Project Acronym

PSNC Poznan Supercomputing and Networking Centre (Poland)

PSU Power Supply Unit

D8.3.2

QCD Quantum Chromodynamics

QCDOC Quantum Chromodynamics On a Chip

QDR Quad Data Rate

QPACE QCD Parallel Computing on the Cell

QR QR method or algorithm: a procedure in linear algebra to compute the eigen-

values and eigenvectors of a matrix

RAM Random Access Memory

RDMA Remote Data Memory Access

RIDS Reference Input Data Sets

RISC Reduce Instruction Set Computer

RNG Random Number Generator

RM RapidMind language

RMS Record Management Services (Open VMS)

RPM Revolution per Minute SAN Storage Area Network

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SAS Serial Attached SCSI

SATA Serial Advanced Technology Attachment (bus)

SDK Software Development Kit

SDSC San Diego Supercomputing Center

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SHMEM SHare MEMory access library (Cray)

SIMD Single Instruction Multiple Data

SM Streaming Multiprocessor, also Subnet Manager

SMC SGI Management Center

SMT Simultaneous MultiThreading

SMP Symmetric MultiProcessing

SNIC Swedish National Infrastructure for Computing (Sweden)

SP Single Precision, usually 32-bit floating point numbers

SPE Synergistic Processing Element (core of Cell processor)

SPH Smoothed Particle Hydrodynamics

spmxv DP sparse-matrix-by-vector multiplication mod2as of the EuroBen kernels

SPU Synergistic Processor Unit (in each SPE)

SSD Solid State Disk or Drive

SSE Streaming SIMD Extensions (Intel)

D8.3.2

STFC Science and Technology Facilities Council (represented in PRACE by EPSRC,

United Kingdom)

STRATOS PRACE advisory group for STRAtegic TechnOlogieS

STT Spin-Torque-Transfer

TARA Traffic Aware Routing Algorithm

TB Tera (=  $2^{40} \sim 10^{12}$ ) Bytes (= 8 bits), also TByte TCB Theoretical and Computational biophysics Group

TDP Thermal Design Power

TFlop/s Tera (=  $10^{12}$ ) Floating-point operations (usually in 64-bit, i.e. DP) per second,

also TF/s

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this context the

Supercomputing Research Infrastructure would host the Tier-0 systems; na-

tional or topical HPC centres would constitute Tier-1

TSMC Taiwan Semiconductor Manufacturing Company, Limited

TUM Technical University Munich

UFM Unified Fabric Manager (Voltaire)

UPC Unified Parallel C UV Ultra Violet (SGI)

VHDL VHSIC (Very-High Speed Integrated Circuit) Hardware Description Language

VPU Vector Processing Unit WP PRACE Work Package

WP5 PRACE Work Package 5 – Deployment of prototype systems

WP6 PRACE Work Package 6 – Software enabling for Petaflop/s systems

WP8 PRACE Work Package 8 – Future Petaflop/s computer technologies beyond

2010

#### **Executive Summary**

The PRACE project [1] started a process in its Work Package 8 (WP8) aiming at the evaluation of components and technologies that can be useful or will be required for future High Performance Computing (HPC) systems. This process will be continued in the permanent pan-European Research Infrastructure. It includes technology surveys and prototype evaluation.

During the first year of the PRACE project, WP8 identified the most promising systems and components that should be evaluated in depth and worked on. Based on the results of this survey, PRACE partners proposed a number of prototypes for detailed evaluation which have been evaluated by external experts to obtain a wide coverage of technologies and to exploit the specific expertise of the partners. Finally twelve WP8 prototypes were selected by PRACE and have been approved by the European Commission (EC) and their HPC technology experts. These prototypes include:

- Programming models/languages such as Chapel, CUDA, RapidMind, HMPP, OpenCL, StarSs(CellSs), UPC and CAF;

- Computing nodes based on NVIDIA as well as AMD GPUs, Cell, ClearSpeed-Petapath, FPGAs, Intel Nights Ferry co-processor and Intel Nehalem and AMD Barcelona and Istanbul processors;

- Systems to assess memory bandwidth, interconnect, power consumption and I/O performance as well as hybrid and power-efficient solutions.

In deliverable D8.3.1 [2] the installation status of the prototypes (hardware and software) and evaluation work performed until mid of September 2009 is described in detail. This deliverable summarises all evaluation results obtained by WP8 during the PRACE PP project and tries to rate the applicability of these different technologies for future European Tier-0 HPC systems.

Two components that have been mainly addressed and evaluated are the programming models and accelerator based nodes. Although some of the prototypes used specific kernels or applications (GADGET, NAMD etc.) in the evaluation, an effort was made to use common benchmark kernels to make the results comparable. WP8 selected 4 kernels from the EuroBen benchmark suite, a dense matrix/matrix multiplication (mod2am), a sparse matrix/vector multiplication (mod2as), a 1-D radix-4 fast Fourier transformation (mod2f) and a random number generator (mod2h) to be ported to different programming languages and processing architectures. These kernels are sufficiently simple to be ported to different programming languages and still do provide significant information concerning ease of use as well as performance.

The experience does show that the performance achievable with the accelerator-based approach is promising but very dependent on the actual coupling between the characteristics of the algorithm and the device. One of the major bottlenecks, the memory bandwidth between the host processor and accelerator has to be addressed in future implementations eventually leading to tightly coupled heterogeneous processing cores in a node. Also the programmability of these devices is still in general far from ideal especially if aiming at very high performance and non trivial codes. At the network level, interconnects with dynamic rerouting capability based on the network load are needed. Also new programming models helping the user to more easily develop and scale parallel applications as well as tools for performance analysis and prediction will be of critical importance in order to be able to efficiently use future European multi-Petascale systems. Equally important will be the development of new scientific libraries which are able to address different optimization criteria such as performance or energy efficiency and support new programming models. Concerning system architecture,

both homogeneous and accelerated clusters with ten thousands compute nodes as well as massively parallel systems with several hundred thousand low power compute nodes seem to be the dominating architectures for the next five years.

#### 1 Introduction

To stay at the forefront of High Performance Computing, PRACE Work Packages WP7 and WP8 have collaboratively started a process to work with technology leaders to prepare for the next generations of multi-Petaflop/s systems. This includes novel components and software technologies to exploit next generation architectures. Close contacts have been established with all major HPC system vendors as well as more than 26 technology providers which are active in areas such as communications network, mass storage and file systems, memory, processing units, programming languages and compilers, system software and tools. The ultimate goal is to engage European industry to develop products for the strategic HPC market and to catch-up and eventually excel in selected fields.

This is not a one-time activity but a continuous process which will be an integral part of the permanent pan-European Research Infrastructure. A major milestone towards the establishment of PRACE as a competent technology partner was the creation of STRATOS (see deliverable D8.1.4 [3]), the PRACE advisory group for Strategic Technologies. STRATOS, founded by twelve PRACE partners and the open Interest Group of European and International users, providers and technology drivers "PROSPECT e.V.", is open to and encourages participation by all PRACE partners but also by other organizations or individuals with an interest to contribute to the evolution of European HPC. With the accession of the French consortium Ter@tec, made up of IT companies, research institutes and industrial users, STRATOS has become a unique European HPC Coordination, Research and Development Consortium consisting of European supercomputing centres and (through PROSPECT e.V. and Ter@tec) over 60 European and world-wide technology providers.

During the first year of the PRACE project, WP8 identified the most promising systems and components that should be evaluated in depth and worked on. With the documentation of these findings in deliverable D8.2.2 [4], a second major milestone of WP8 was reached at the end of 2008. Finally twelve WP8 prototypes were selected by PRACE (see D2.7.2 [5] and its addendum [6]) and have been approved by the European Commission (EC) and their HPC technology experts. These prototypes include:

- Programming models/languages such as Chapel, CUDA, RapidMind, HMPP, OpenCL, StarSs(CellSs), UPC and CAF;

- Computing nodes based on NVIDIA as well as AMD GPUs, Cell, ClearSpeed-Petapath, FPGAs, Intel Nights Ferry co-processor and Intel Nehalem-EP and AMD Barcelona and Istanbul processors;

- Systems to assess memory bandwidth, interconnect, power consumption and I/O performance as well as hybrid and power-efficient solutions.

Their evaluation has led to new insights which will be reported in detail in this document. Due to late delivery of some prototypes the work on these technologies could not be completed in 2009. This deliverable summarizes all work performed by WP8 during the PRACE Preparatory Phase project and it's extension period. The following chapters and subsections of this document contain completely new or updated information:

• Chapters 2.1.3, 2.1.4, 2.1.10, 2.2.1

- Chapter 3.1.6 LRZ + CINES (Phase 2)

- Chapter 3.1.7 Intel MIC Architecture

- Chapter 3.3.1 Triads (RINF1) benchmark results (BAdW-LRZ)

- Chapter 3.3.2 Random Access Results

- Chapter 3.4 Inter Node Communication Network

- Chapter 3.5 PGAS Languages

- Chapter 3.7.1 The SNIC-KTH system

- Chapter 3.7.2 PSNC results

- Chapter 3.7.3 STFC results

- Chapter 3.9.3 Network bandwidth

#### 1.1 Scope and Structure of the Report

This deliverable summarises all evaluation results obtained by WP8 so far and tries to rate the applicability of these different technologies for future European Tier-0 HPC systems. The document also aims at suggesting directions of potential research interest in order to develop European technology towards the Exaflop/s era.

In Chapter 2 each prototype together with its key evaluation objectives are briefly described.

Chapter 3 describes the experiments that have been performed on the different WP8 prototypes. The advanced nature of the WP8 prototypes makes a strongly structured approach for the assessment, as it was taken by WP5/7 impossible. The assessment reports are arranged under several sub-chapters such as "GPGPU Programming Languages and Accelerated Compilers", "Hybrid Programming Models", "Intra-node Bandwidth", "Inter-node Communication Network", "PGAS Languages", "Novel I/O" and "Energy Efficiency" as far as their evaluation objective matches with these categories. Since the influence of the communication network and processor performance on application scaling often cannot be tested on real hardware because future Tier-0 systems are expected to contain new hard- and software components which are not available at the time important system design decisions will have to be made, performance prediction tools might become a key system design technology for the PRACE Legal Entity in future. Section 3.8 describes the experiment to identify issues that may be relevant when scaling or porting applications to future architectures. Finally, a short summary of the evaluation results together with concluding remarks are given in Section 3.9.

In Chapter 4 recommendations for future multi-Petascale architectures are given based on the prototype assessment and the PRACE technology surveys.

Chapter 5 gives final conclusions and remarks.

Chapter 6, an annex, gives a brief description of the benchmarks and applications used for the prototype evaluations and for the research activities listed in Section 2.2.

#### 2 WP8 prototypes and Research Activities

#### 2.1 Prototypes

All WP8 prototypes are addressing the area of the emerging technologies for Petascale systems. Their aim is to investigate a specific and vertical set of hardware and software issues. In this section the prototypes acquired for evaluation within Work Package 8 are succinctly described. In addition, the lead partners and the key evaluation objectives for each prototype are listed. Section 2.2 describes common research activities of WP8 parties on WP7 and WP8 prototype hardware.

#### 2.1.1 eQPACE

Key Objective: Evaluation and extension of special-purpose cluster architecture

QPACE regarding applications beyond QCD.

Lead Partner: FZJ.

QPACE (Quantum Chromodynamics Parallel Computing on the Cell) is a massively parallel and scalable computer architecture optimized for lattice Quantum Chromodynamics (LQCD) which is developed among several academic institutions (SFB TR 55) and the IBM development lab in Böblingen, Germany.

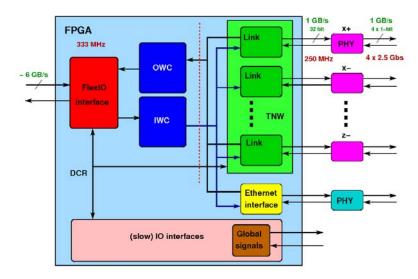

Figure 1: QPACE Architecture

The building block of QPACE is a node card comprising an IBM PowerXCell 8i processor and a custom FPGA-based network processor. The 3D-torus network supports SPE-centric nearest-neighbour communication between the SPE cores of adjacent nodes and data transfer between its Local Stores.

32 node cards are mounted on a single backplane. One dimension of the 3D-torus network is completely routed within the backplane where the nodes are arranged as one partition of  $1 \times 4 \times 8$  nodes or as multiple smaller partitions. For larger partitions, cables interconnect several backplanes. Eight backplanes reside in one rack, hosting a total of 256 node cards corresponding to an aggregate peak performance of 26 TFlop/s (DP).

The 3D-torus network interconnects the node cards with nearest-neighbour communication links driven by a lean custom protocol optimized for low latencies. For the physical layer of

the links 10 Gigabit Ethernet PHYs<sup>1</sup> are used providing a bandwidth of 1 GB/s per link and direction.

On each node card, the network processor is also connected to a Gbit-Ethernet transceiver. The Ethernet ports of all node cards connect to standard Ethernet switches housed within the QPACE rack. Depending on the I/O requirements, the Ethernet bandwidth between a QPACE rack and a front-end system can be adjusted by changing the bandwidth of the uplinks of the switches.

The backplanes in the rack, which holds 32 node cards, are connected to a liquid-cooled coldplate which acts as a heat conductor thus making QPACE a highly energy efficient ecosystem. An upper limit for the power consumption is about 125 W per node card. To remove the generated heat a cost-efficient liquid cooling system has been developed, which enables high packaging densities. The maximum power consumption of one QPACE rack is about 32 kW.

An IBM e1350 cluster serves as front-end system. It comprises login and master nodes as well as six nodes intended to provide a parallel Lustre file system with two meta data and four object storage servers. The disk storage amounts to five enclosures, each with  $14 \times 72$  GB disks.

#### Goals of eQPACE are:

- Extend the features of QPACE to make the system suitable for a range of applications beyond QCD;

- Leverage the feature that an FPGA is used to implement the torus interconnects and use different versions of FPGA bitstreams;

- Extend the software stack, e.g., by development of a subset of MPI functions for the torus API.

#### 2.1.2 BAdW-LRZ/GENCI-CINES Phase1 (CINES Part)

Key Objective: Evaluation of a hybrid thin node system based (Bi Nehalem-EP and

ClearSpeed e710).

Lead Partner: GENCI – CINES.

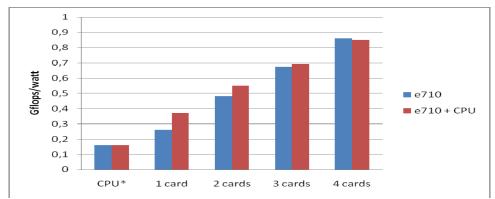

The prototype installed at CINES focuses on assessing the ClearSpeed accelerator, one characteristic of which is energy efficiency. The evaluation process has to take advantage of both node processors and accelerator, by determining the optimal repartition of computing load has to be found.

The platform is integrated in the Tier-1 HPC platform JADE (128 TFlop/s LINPACK), sharing Lustre parallel file system, PBSPro Batch scheduler.

The targeted SGI-ICE / ClearSpeed-Petapath platform (Figure 2) configuration is:

SGI hosting platform:

32 Blades XE

64 Processors Intel Nehalem-EP

256 Cores

4 GB per core

Infiniband QDR

Estimated peak performance is 2.53 TFlop/s

ClearSpeed-Petapath accelerators:

32 x e710 card

**PRACE - RI-211528** 5 25.06.2010

<sup>&</sup>lt;sup>1</sup> PHY is a chip where the lowest PHY sical layer of a network is implemented

One per ICE blade 4 GFlop/s / Watt Software development toolkit

Estimated peak performance is 3 TFlop/s. The total accumulated peak performance is 5.53 TFlop/s.

Figure 2: Prototype configuration and integration layout

#### 2.1.3 BAdW-LRZ/GENCI-CINES Phase2 (LRZ Part)

Key Objective: Evaluation of a hybrid system architecture containing thin nodes, fat

nodes and compute accelerators with a shared file system.

Lead Partner: Leibniz Supercomputing Centre (BAdW-LRZ).

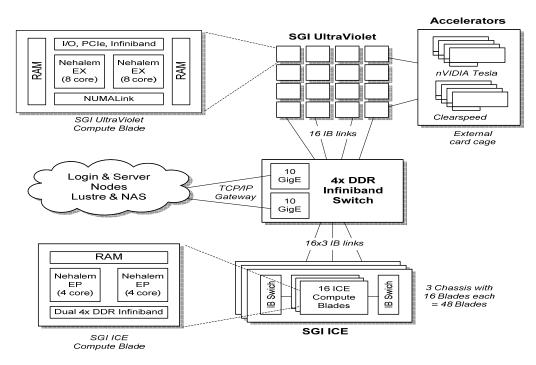

The joint prototype proposal from BAdW-LRZ (referred to as LRZ) and GENCI-CINES (referred to as CINES) shown in Figure 4 focuses on the last generation systems from SGI which are able to scale up to peak performances of multi-PFlop/s. It is composed of ccNUMA (UltraViolet, UV) and MPP (Altix ICE 8200LX) systems and accelerated with ClearSpeed-Petapath Advance e710 and nVIDIA Tesla 1060 accelerators<sup>2</sup>.

While the focus of the CINES prototype lies in the evaluation of using ClearSpeed-Petapath boards to accelerate real applications and enhance their energy efficiency dramatically, the main objective of the LRZ part is to assess the advantages of hybrid systems for the LRZ workload. The evaluation focus of this approach divides up into the following axes of assessment:

- Hybrid system consisting of Intel Nehalem-EP-based thin nodes and Nehalem-EX-based fat nodes with ClearSpeed-Petapath and nVIDIA compute accelerators;

- Performance/Power efficiency and ease of use for different scientific areas;

- Support for new programming languages like CAF, UPC and RapidMind.

-

<sup>&</sup>lt;sup>2</sup> Originally it was planned to evaluate the suitability of Intel Larrabee GPGPUs for accelerating HPC applications. Since Intel changed its product plans [48], LRZ started to assess GPGPU programming with nVIDIA hardware. During the PRACE extension phase, Intel provided LRZ with a prototype software development vehicle for the new Intel Many Integrated Cores (MIC) architecture.

Figure 4: Hybrid system prototype installed at BAdW-LRZ

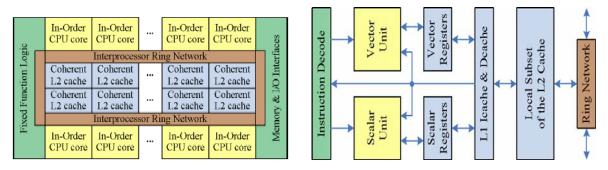

#### 2.1.4 Intel Many Integrated Core (MIC) architecture

Key Objective: Evaluation of the ease of use of the Intel "Many Integrated Core" (MIC)

architecture for HPC applications.

Lead Partner: Leibniz Supercomputing Centre (BAdW-LRZ).

Figure 5 shows a scheme of the Intel MIC architecture prototype. It uses 32 in-order x86-based processor cores that are augmented by a 512 bit wide vector processing unit (VPU) (see Figure 6). All cores are interconnected by a bi-directional on-chip ring network. This ring network also provides a path for the L2 caches to access memory. The L2 cache is shared between all cores. The instruction decoder of the Intel MIC architecture supports the standard Pentium x86 instruction set as well as new instructions for explicit cache control and vector type operations.

Each core has access to its 256 KByte local subset of a coherent L2 cache. The L1 cache sizes are 32 KByte for instructions and 32 KByte for data. Furthermore each scalar unit supports 4 threads of execution, with separate register sets per thread. Hence thread switching can be extensively used to cover cases such as pipeline stalls and cache misses.

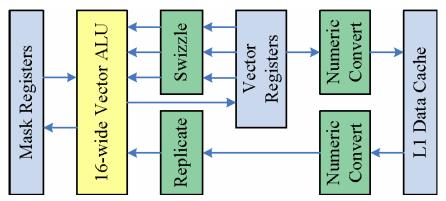

Figure 7 shows a block diagram of the 16-wide vector processing unit. A set of new VPU instructions allow a variety of instructions on both integer and floating point data types such as:

- Standard arithmetic operation including fused multiply-add;

- Standard logical operations;

- Gather and scatter operations.

The VPU instructions allow up to three source operands, one of which can directly come from the L1 cache. 8-bit and 16-bit integer and floating point numbers can be directly converted to 32-bit integer and floating point numbers without loss of performance. The VPU supports swizzling of register data in a variety of ways and replication of data from memory across the VPU lanes.

Figure 5: Scheme of Intel MIC architecture prototype.

Figure 6: x86-based core and associated system blocks

Figure 7: Block diagram of vector processing unit (VPU).

The focus on the assessment of this Intel MIC architecture is to evaluate the ease of use of this parallel SMP cache coherent prototype processor platform for HPC.

#### 2.1.5 ClearSpeed-Petapath

Key Objective: Evaluation of the Petapath Feynman e740 and e780 prototype products

based on ClearSpeed technology within cluster configuration.

Lead Partner: NCF.

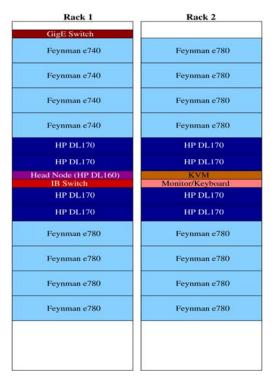

The configuration is given in the Figure 8. The light blue boxes labelled "Feynman e740/e780" contain 4 or 8 ClearSpeed CSX700 processors for a total of 112. The dark blue HP DL170 host nodes each connect to two Feynman boxes by PCI Express Gen. 2 16× (8 GB/s).

The HP host nodes are connected by 4× DDR Infiniband (IB) in order to employ them, and the attached accelerator boxes, in parallel via MPI.

Internally a Feynman e780 connects to its 8 processors through a PLX 8648 PCIe switch. The bandwidth to each individual processor is 1 GB/s. The e740 boxes contain only 4 CSX700 processors but the bandwidth to/from the individual processors is doubled to 2 GB/s. This should help for bandwidth-hungry applications. The peak performances are 768 GFlop/s and 384 GFlop/s in 8-Byte precision (DP) for a Feynman e780 and e740, respectively. The energy efficiency is very high:  $\approx$  4

Figure 8: Clearspeed-Petapath prototype

GFlop/s/Watt.

The HP DL170h G6 host nodes contain 2 Intel X5550 Nehalem-EP processors at 2.67 GHz and 24 GB of DDR3 memory/node. Furthermore, each host node contains dual disks of 250 and 500 GB, for system and user data, respectively. Access to the system is provided through the HP DL160 G6 head node. The system is divided in a development part (1 DL170 + 2 Feynman e740s) and an application assessment part (7 DL170s + 2 Feynman e740s + 12 Feynman e780s).

#### 2.1.6 Hybrid Technology Demonstrator

Key Objective: Evaluating GPGPU and HMPP.

Lead Partner: GENCI-CEA.

The Hybrid technology Demonstrator is a platform to study the impact of GPU computing in terms of programming languages. Based on nVIDIA TESLA servers, this machine can run different programming environments such as CUDA, RapidMind, OpenCL, Ct and HMPP.

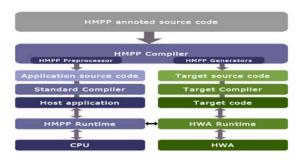

On this prototype, we have focused on the HMPP environment provided by [9] to study the impact of a directive-based programming model in terms of ease of development as well as effective performances.

The prototype is a cluster of 5 nodes. The first node is a login node featuring four Intel Nehalem-EP processors. The last four nodes are BULL R422 servers featuring 2 Intel Harpertown CPU with 16 GB of RAM each. The BULL servers are connected through a PCI-Express 16× to two nVIDIA TESLA servers. Interconnects between the nodes are Infiniband DDR.

A TESLA server has 2 PCI-Express 16× links with 2 C1060 graphic boards on each. A C1060 features 30 multiprocessors at 1.3 GHz and has 4 GB of memory. One multiprocessor has 8 single precision (SP) units and 1 double precision (DP) unit. Therefore, a C1060 can have 240 SP (30 DP) units running in parallel. The peak performance of a C1060 is 78 GFlop/s DP and 624 GFlop/s SP.

The main component to be assessed is HMPP since we consider the TESLA as a product which has already been extensively studied. New languages such as OpenCL or Ct were not available at the beginning of this project.

We run the HMPP Workbench software, release 2.1.0sp1 as of the writing of this report. We started our evaluation with release 1.5.3. Since HMPP is a source code generator (a preprocessor) we use the usual Intel compiler (version 11.1) for the host program and the CUDA 2.3 environment for the TESLA part of the software.

HMPP relies on directives which are in the form of special comments in the source code for FORTRAN or pragmas for C. HMPP has the ability to generate code for different types of targets. Here we will focus only on the CUDA one as it is the native environment for a nVIDIA TESLA platform. A future study of different targets (for example CAL/IL) needs to be done.

Figure 9: Overview of HMPP components

Our work will consist in adding directives to the proposed codes, evaluate the difficulty of this task and then modify the codes to get the best performances with the HMPP/CUDA driver.

For comparison sake, we have concentrated our efforts on two of the EuroBen benchmarks. We have selected mod2am and mod2as because they are very frequent kernels in scientific codes. Mod2am implements a matrix multiplication which can be easily compared with some vendor libraries (here the CUBLAS one). Mod2as implements a reduction which is well known for being hard to parallelize. Therefore it appeared to us that these two kernels would be good challenges for the HMPP software.

#### 2.1.7 Maxwell FPGA

Key Objective: Evaluate the performance and usability of HARWEST Compiling Envi-

ronment.

Lead Partner: EPSRC-EPCC.

#### **Objective**

Our objective is to evaluate the performance and usability of state-of-the-art FPGA programming tools. We plan to port the 4 EuroBen kernels to the FPGA hardware in Maxwell using a C-to-gates compiler, the Harwest Compilation Environment from Ylichron [10].

We will evaluate the performance of the ported kernels, compared to the original kernels running in software. Where possible we will also compare their performance to that of a hand-coded VHDL (Very-High Speed Integrated Circuit Hardware Description Language) implementation of similar algorithms. Finally, we will evaluate the usability of the compiler (how much effort it takes to port a C program to it, how much specialist hardware knowledge is required to get an adequate result, etc.).

#### Architecture

In 2007, the FPGA High Performance Computing Alliance (FHPCA) completed work on the Maxwell – a pre-production technology demonstrator system built using 32 accelerator cards from Alpha Data Ltd and 32 from Nallatech Ltd using Virtex-4 FPGAs supplied by Xilinx Corp. These accelerator cards are hosted in a 32 node IBM HS21-based BladeCenter system. Each node therefore consists of a single-core 2.8 GHz Xeon processor with two accelerator cards connected on a PCI-X bus. The main novelty in the design of the system is its use of the RocketIO connections on the FPGAs to create a nearest neighbour two-dimensional mesh interconnect between the FPGAs. This can allow a complete numerical algorithm to be executed in parallel with no need for the FPGAs to communicate over the (relatively) slow PCI-X bus.

#### Major components to be assessed