## SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

INFRA-2007-2.2.2.1 - Preparatory phase for 'Computer and Data Treatment' research infrastructures in the 2006 ESFRI Roadmap

## **PRACE**

## Partnership for Advanced Computing in Europe

**Grant Agreement Number: RI-211528**

# D6.6 Report on petascale software libraries and programming models

#### **FINAL**

Version: 1.0

Author(s): Giovanni Erbacci (CINECA)

Carlo Cavazzoni (CINECA) Filippo Spiga (CINECA) Iris Christadler (LRZ)

Date: 26/10/2009

## **Project and Deliverable Information Sheet**

| PRACE Project                             | Project Ref. №: RI-211528                                                                 |                |  |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------|----------------|--|--|--|--|

|                                           | Project Title: Partnership for Advanced Computing in Europe                               |                |  |  |  |  |

|                                           | Project Web Site: <a href="http://www.prace-project.eu/">http://www.prace-project.eu/</a> |                |  |  |  |  |

|                                           | Deliverable ID: D6.6                                                                      |                |  |  |  |  |

|                                           | Deliverable Nature: Report                                                                |                |  |  |  |  |

|                                           | Deliverable Level: Contractual Date of Delivery:                                          |                |  |  |  |  |

|                                           | PU                                                                                        | 31 / 10 / 2009 |  |  |  |  |

| Actual Date of Delivery:                  |                                                                                           |                |  |  |  |  |

|                                           | 30 / 10 / 2009                                                                            |                |  |  |  |  |

| EC Project Officer: Maria Ramalho-Natario |                                                                                           |                |  |  |  |  |

<sup>\* -</sup> The dissemination level are indicated as follows: **PU** – Public, **PP** – Restricted to other participants (including the Commission Services), **RE** – Restricted to a group specified by the consortium (including the Commission Services). **CO** – Confidential, only for members of the consortium (including the Commission Services).

#### **Document Control Sheet**

|            | Title: Report on petascale software libraries and programming models |                                         |  |  |  |  |

|------------|----------------------------------------------------------------------|-----------------------------------------|--|--|--|--|

| Document   | ID: D6.6                                                             |                                         |  |  |  |  |

|            | Version: 1.0                                                         | Status: Final                           |  |  |  |  |

|            | Available at: <a href="http://w">http://w</a>                        | ww.prace-project.eu/                    |  |  |  |  |

|            | Software Tool: Microso                                               | oft Word 2003                           |  |  |  |  |

|            | File(s): D6.6.dd                                                     | oc                                      |  |  |  |  |

|            | Written by:                                                          | Giovanni Erbacci (CINECA),              |  |  |  |  |

| Authorship |                                                                      | Carlo Cavazzoni (CINECA),               |  |  |  |  |

|            |                                                                      | Filippo Spiga (CINECA),                 |  |  |  |  |

|            |                                                                      | Iris Christadler (LRZ)                  |  |  |  |  |

|            | Contributors:                                                        | Reinhold Bader (LRZ), Mark Bull (EPCC), |  |  |  |  |

|            |                                                                      | Guillaume Colin de Verdiere (GENCI),    |  |  |  |  |

|            |                                                                      | Maciej Cytowski (PSNC), Montse Farreras |  |  |  |  |

|            |                                                                      | (BSC), Maciej Filocha (PSNC), Georgios  |  |  |  |  |

|            |                                                                      | Goumas (GRNET), Jose Gracia (HLRS),     |  |  |  |  |

|            |                                                                      | Hans Hacker (BAdW-LRZ), Pierre-         |  |  |  |  |

|            |                                                                      | Francois Lavalleee (IDRIS), Olli-Pekka  |  |  |  |  |

|            |                                                                      | Letho (CSC), Walter Lioen (SARA), James |  |  |  |  |

|            |                                                                      | Perry (EPSRC), Sami Saarinen (CSC),     |  |  |  |  |

|            |                                                                      | Ramnath Sai Sagar (BSC), Tim Stitt      |  |  |  |  |

|            |                                                                      | (CSCS), Aad Van der Steen (NCF), Volker |  |  |  |  |

|            |                                                                      | Weinberg (BADW-LRZ)                     |  |  |  |  |

|            | Reviewed by:                                                         | Thomas Eickermann (FZJ),                |  |  |  |  |

|            |                                                                      | Stefan Wesner (HLRS)                    |  |  |  |  |

|            | Approved by:                                                         | Technical Board                         |  |  |  |  |

## **Document Status Sheet**

| Version | Date              | Status        | Comments               |

|---------|-------------------|---------------|------------------------|

| 0.1     | 26/March/2009     | Draft         | Initial Draft          |

| 0.2     | 27/July/2009      | Draft         | Chapters 3-5 improved  |

| 0.3     | 15/September/2009 | Draft         | Chapter 6 and 8        |

|         |                   |               | improved               |

| 0.4     | 5/October/2009    | Draft         | Included Chapter 7 and |

|         |                   |               | Appendixes             |

| 0.5     | 12/October/2009   | Final Draft   | For PRACE QA           |

| 1.0     | 26/October/2009   | Final version | For EC                 |

## **Document Keywords and Abstract**

| Keywords: | PRACE, HPC, Research Infrastructure, Petascale, Software libraries, Parallel Programming models and languages.                                                                                                                                                                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract: | This deliverable identifies and analyses the programming models and the software libraries required by petascaling applications in the PRACE implementation phase.                                                                                                                                                                                                                                           |

|           | The work starts from an analysis of the applications mainly identified in D6.1 and D6.2.2, covering a broad range of scientific areas, and representative of the European HPC usage, to assess the state of the art with particular attention to programming languages, programming models and scientific libraries.                                                                                         |

|           | Starting from this basis an accurate survey and analysis of the new upcoming programming models and languages suitable for petascale applications is presented, trying to identify gaps and opportunities provided in terms of performance and efficiency and benefit for parallelism.                                                                                                                       |

|           | Furthermore, three numerical kernels, typical of the most important computational applications, have been selected, and coded, using twelve of the different programming languages and paradigms under investigation. This coding experience and the consequent porting and assessment on the prototypes selected by WP8, greatly contributed to better complete the analysis objective of this Deliverable. |

#### Copyright notices

© 2009 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-211528 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

## **Table of Contents**

| Pro | ject a | and Deliverable Information Sheet                                   | i  |

|-----|--------|---------------------------------------------------------------------|----|

| Do  | cume   | nt Control Sheet                                                    | i  |

| Do  | cume   | nt Status Sheet                                                     | i  |

| Do  | cume   | nt Keywords and Abstract                                            | ii |

|     |        | Contents                                                            |    |

|     |        | igures                                                              |    |

|     |        | ables                                                               |    |

|     |        |                                                                     |    |

|     |        | ces and Applicable Documents                                        |    |

|     |        | cronyms and Abbreviations                                           |    |

| Exe | ecutiv | e Summary                                                           | 1  |

| 1   | Intr   | oduction                                                            |    |

|     | 1.1    | Objectives                                                          |    |

|     | 1.2    | Methodology                                                         |    |

|     | 1.3    | Structure of the Report                                             |    |

| 2   |        | alysis of current HPC applications                                  |    |

|     | 2.1    | Current programming models in PRACE application list                |    |

| 2   |        | • •                                                                 |    |

| 3   |        | I, OpenMP, mixed MPI-OpenMP: current standards and their evolution  |    |

|     | 3.1    | 3.1.1 Current standard (MPI 2.2).                                   |    |

|     |        | 3.1.2 Overview of support in current implementations                |    |

|     |        | 3.1.3 Future: MPI 3.0                                               |    |

|     | 3.2    | OpenMP                                                              |    |

|     |        | 3.2.1 Current standard (OpenMP 3.0)                                 |    |

|     |        | 3.2.2 Overview of support in current implementations                |    |

|     | 3.3    | Mixed mode (MPI+OpenMP)                                             |    |

|     |        | 3.3.1 Current status                                                | 12 |

|     |        | 3.3.2 Overview of support in current implementations                |    |

|     |        | 3.3.3 Future                                                        |    |

|     | 3.4    | Final remarks                                                       |    |

| 4   |        | titioned Global Address Space (PGAS) Programming Languages          |    |

|     | 4.1    | Unified Parallel C (UPC)                                            |    |

|     | 7.1    | 4.1.1 The Execution and Memory Model                                |    |

|     |        | 4.1.2 Current Implementations                                       |    |

|     | 4.2    | Coarray Fortran (in the context of the Fortran 2008 Draft Standard) |    |

|     |        | 4.2.1 The Execution and Memory Model                                |    |

|     | 4.3    | 4.2.2 Current Implementations                                       |    |

|     | 4.3    | 4.3.1 The Execution and Memory model                                |    |

|     |        | 4.3.2 Current Implementation                                        |    |

| 5   | Nex    | t Generation Programming Languages and Models                       | 21 |

| -   | 5.1    | Chapel                                                              |    |

|     |        |                                                                     |    |

|   |            | 5.1.1 The Chapel Programming Model                            | 21       |

|---|------------|---------------------------------------------------------------|----------|

|   |            | 5.1.2 Chapel Developments                                     | 22       |

|   | 5.2        | X10                                                           | 22       |

|   |            | 5.2.1 The X10 Programming Model                               | 23       |

|   |            | 5.2.2 X10 Developments                                        | 23       |

|   | 5.3        | Fortress                                                      | 23       |

|   |            | 5.3.1 The Fortress Programming Model                          | 24       |

|   |            | 5.3.2 Fortress Developments                                   | 25       |

|   | 5.4        | Transactional Memory                                          | 25       |

|   |            | 5.4.1 Basic concepts                                          | 25       |

|   |            | 5.4.2 Current implementations                                 | 26       |

| 6 | Lar        | nguages, Paradigms and Environments for Hardware Accelerators | 28       |

|   | 1          | Assessment of the libraries                                   |          |

|   | 6.1        | Cell programming                                              |          |

|   | 6.2        | CUDA (by NVIDIA)                                              |          |

|   |            | 6.2.1 Programming Model                                       |          |

|   |            | 6.2.2 Memory Model                                            |          |

|   |            | 6.2.3 Current support and libraries availability              |          |

|   | 6.3        | OpenCL                                                        |          |

|   |            | 6.3.1 OpenCL Architecture                                     |          |

|   |            | 6.3.2 Execution Model                                         |          |

|   |            | 6.3.3 Memory Model                                            |          |

|   |            | 6.3.4 The OpenCL framework and runtime                        |          |

|   |            | 6.3.5 Portability and know limitations                        |          |

|   | 6.4        | CAPS HMPP                                                     |          |

|   |            | 6.4.1 Programming interface                                   |          |

|   |            | 6.4.2 Description of the runtime                              |          |

|   |            | 6.4.3 Current implementation                                  |          |

|   | 6.5        | RapidMind                                                     |          |

|   |            | 6.5.1 Architecture and programming model                      |          |

|   |            | 6.5.2 Portability and known limitations                       |          |

|   |            | 6.5.3 Future Developments                                     |          |

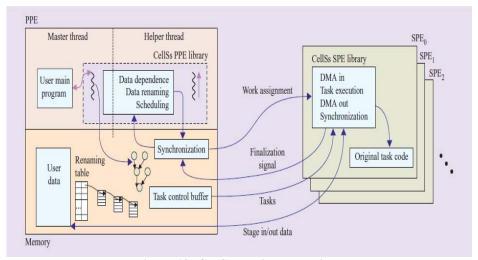

|   |            | CellSs (StarSs programming models family)                     |          |

| _ | 6.7        | Cn for ClearSpeed accelerators                                |          |

| 7 |            | essment of the languages and porting activity                 |          |

|   | 7.1        | The concept of productivity in the HPC context                |          |

|   | 7.2        | Measuring Productivity                                        |          |

|   | 7.3        | Porting Results                                               |          |

|   |            | 7.3.1 Number of Source Lines                                  |          |

|   |            | 7.3.2 Development Time                                        |          |

|   | (          | Comparing MKL versus MPI+OpenMP                               |          |

|   |            | New and old PGAS languages                                    |          |

|   |            | GPGPU languagesGPGPU languages                                |          |

|   |            | Languages for accelerators                                    |          |

|   |            | 7.3.4 Considerations about the reporting template             |          |

|   |            | 7.3.5 Lessons learned                                         |          |

| 0 | <b>A</b> ~ |                                                               |          |

| 8 |            | essment of libraries for petascale systems                    |          |

|   | 8.1        | 8 1 1 Linear Algebra                                          | 71<br>71 |

|   |            | A L L LINEUL ALVENIU                                          | / 1      |

|    |      | 8.1.2 Fast Fourier Trasform                                        | 72 |

|----|------|--------------------------------------------------------------------|----|

|    | 8.2  | I/O Libraries                                                      |    |

|    | 0.2  | 8.2.1 <i>POSIX I/O.</i>                                            |    |

|    |      | 8.2.2 MPI-I/O                                                      |    |

|    |      | 8.2.3 HDF5                                                         |    |

|    |      | 8.2.4 NetCDF-4                                                     |    |

|    |      | 8.2.5 Parallel NetCDF                                              |    |

|    |      | 8.2.6 Preliminary results testing I/O parallel libraries           |    |

|    |      | 8.2.7 Conclusion on parallel I/O libraries                         |    |

|    | 8.3  | High Level Libraries                                               |    |

|    |      | 8.3.1 ScaLAPACK                                                    |    |

|    |      | 8.3.2 <i>PETSc</i>                                                 |    |

|    |      | 8.3.3 Vendor libraries                                             | 81 |

|    |      | 8.3.4 <i>NAG</i>                                                   | 81 |

|    | 8.4  | Communication libraries                                            | 82 |

|    | 8.5  | Special Purpose Libraries                                          | 82 |

|    | 8.6  | Conclusion of the assessment                                       | 83 |

| 9  | Con  | iclusions and final remarks                                        | 84 |

| 10 |      | Annex A: Reference Input Data Sets (RIDS)                          |    |

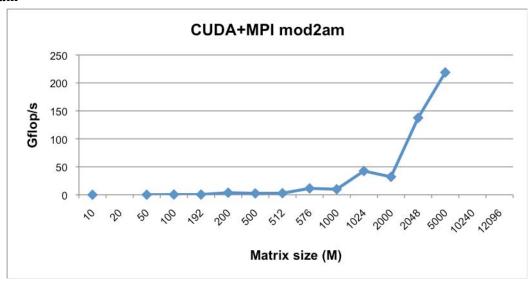

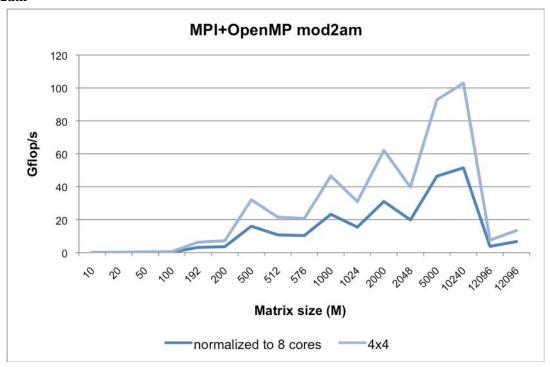

| 10 | 10 1 | mod2am                                                             |    |

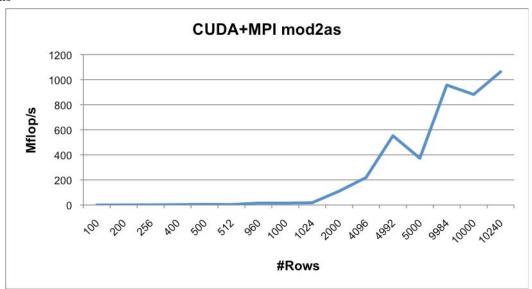

|    |      | mod2as                                                             |    |

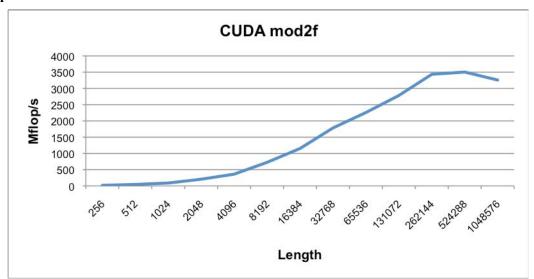

|    |      | mod2f                                                              |    |

|    |      | mod2h                                                              |    |

|    | 10.4 |                                                                    |    |

| 11 |      | Annex B: Hardware Overview                                         |    |

|    |      | 11.1 System "clearspeed-petapath" (WP8-NCF)                        |    |

|    |      | 11.2 System "itanium" (LRZ)                                        |    |

|    |      | 11.4 System "louhi" (WP7-CSC)                                      |    |

|    |      | 11.5 System "cell-cluster" (PSNC)                                  |    |

|    |      | 11.6 System "maxwell" (WP8-EPCC)                                   |    |

|    |      | 11.7 System "nehalem" ("ice" WP8-LRZ, "inti" WP7-CEA, "baku" HLRS) |    |

|    |      | 11.8 System "uchu" (WP8-CEA)                                       |    |

| 12 |      | Annex C: Software Engineering Metrics                              | 93 |

|    | 12.1 | SLOC: Source Lines of Code                                         |    |

|    |      | NCSS: Non-Commented Source Code Statements                         |    |

|    |      | Time to solution & others                                          |    |

| 13 | 12.0 | Annex D: Template of the Porting Diary                             |    |

| _  |      |                                                                    |    |

| 14 | 141  | Annex E: Reported Results for all Languages                        |    |

|    |      | Coarray Fortran (CAF)                                              |    |

|    |      | Developer Diary                                                    |    |

|    |      | Porting Results on Cray XT (CSC)                                   |    |

|    |      | Porting Results on SGI Altix (LRZ)                                 |    |

|    |      | Performance Measurements                                           |    |

|    |      | CAPS HMPP                                                          |    |

|    |      | Basic Information                                                  |    |

|    |      | Developer Diary                                                    |    |

|    |      | Porting Results                                                    |    |

|    |      | Performance Measurements                                           |    |

| 14.3 Cell-Superscalar (CellSs)                | 101 |

|-----------------------------------------------|-----|

| Basic Information                             |     |

| Developer Diary                               |     |

| Porting Results                               |     |

| Performance Measurements                      |     |

| 14.4 Chapel                                   |     |

| Basic Information                             |     |

| Developer Diary                               |     |

| Porting Results                               |     |

| Performance Measurements                      |     |

| 14.5 ClearSpeed Cn                            |     |

| Basic Information                             |     |

| Developer Diary                               |     |

| Porting Results                               |     |

| Performance Measurements                      |     |

| 14.6 CUDA                                     |     |

| Basic Information                             |     |

| Developer Diary                               |     |

| Porting Results                               |     |

| Performance Measurements                      | 118 |

| 14.7 CUDA+MPI                                 | 120 |

| Basic Information                             | 120 |

| Developer Diary                               | 120 |

| Porting Results                               |     |

| Performance Measurements                      | 122 |

| 14.8 FPGA (VHDL and/or Harwest C)             |     |

| Basic Information                             | 123 |

| Developer Diary                               |     |

| Porting Results                               | 123 |

| Performance Measurements                      | 125 |

| 14.9 MPI+OpenMP                               | 126 |

| Basic Information                             |     |

| Developer Diary                               | 126 |

| Porting Results                               | 128 |

| Performance Measurements                      | 131 |

| 14.10 OpenCL                                  | 132 |

| Basic Information                             | 132 |

| Developer Diary                               | 132 |

| Porting Results                               | 132 |

| Performance Measurements                      | 133 |

| 14.11 RapidMind                               |     |

| Basic Information                             | 134 |

| Developer Diary                               | 134 |

| Porting Results                               |     |

| Performance Measurements                      | 137 |

| 14.12 Unified Parallel C (UPC)                | 138 |

| Basic Information                             | 138 |

| Developer Diary                               |     |

| Porting Results on System louhi (Cray XT)     |     |

| Porting Results on System itanium (SGI Altix) |     |

| Porting Results on System Huygens (Power5)    | 140 |

## D6.6 Report on petascale software libraries and programming models

| Performance Measurements | 142 |

|--------------------------|-----|

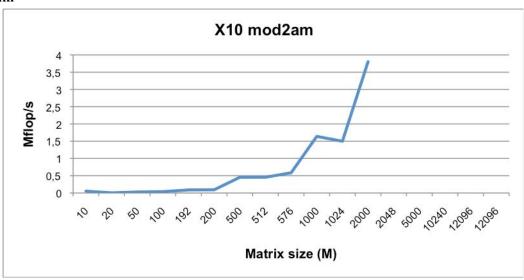

| 14.13 X10                | 144 |

| Basic Information        | 144 |

| Developer Diary          |     |

| Porting Results          |     |

| Performance Measurements |     |

## **List of Figures**

| Figure 1: Message Passing, Shared Memory and PGAS models                                        |     |

|-------------------------------------------------------------------------------------------------|-----|

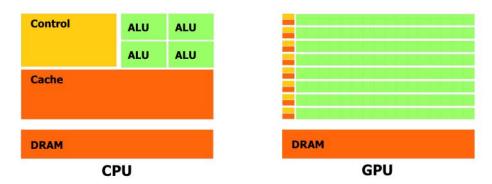

| Figure 2: Differences between CPUs and GPUs                                                     |     |

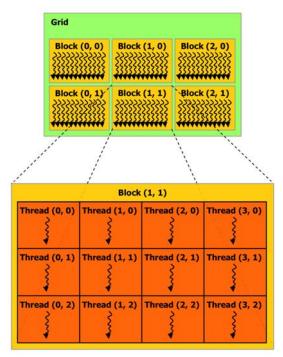

| Figure 3: CUDA two-level hierarchy of thread organization                                       |     |

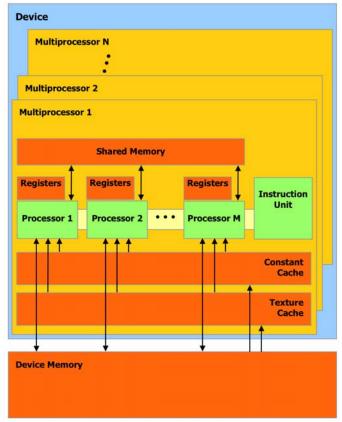

| Figure 4: CUDA memory device model                                                              |     |

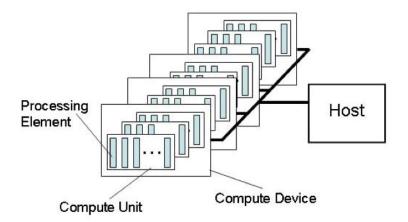

| Figure 5: OpenCL Architecture Model                                                             |     |

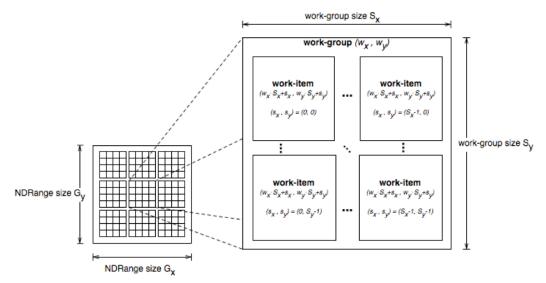

| Figure 6: OpenCL Work-Groups and Work-Items organization                                        | 36  |

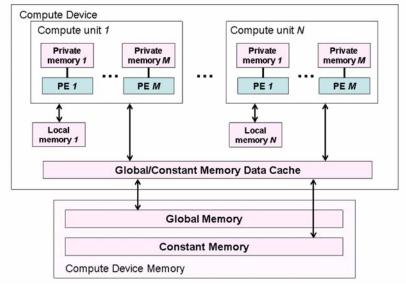

| Figure 7: OpenCL Memory Model                                                                   |     |

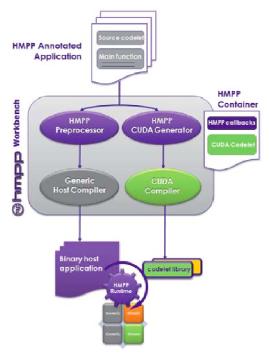

| Figure 8: HMPP code generation flow                                                             | 39  |

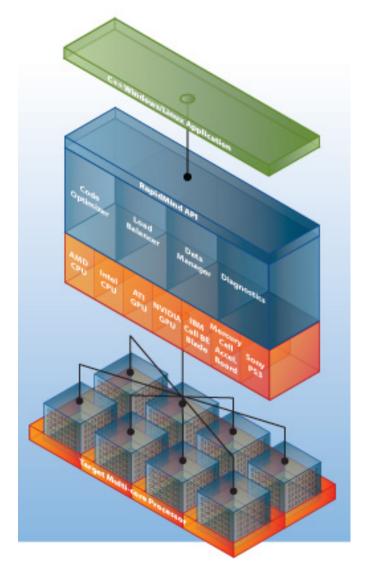

| Figure 9: RapidMind runtime                                                                     | 40  |

| Figure 10: CellSs runtime behaviour                                                             | 43  |

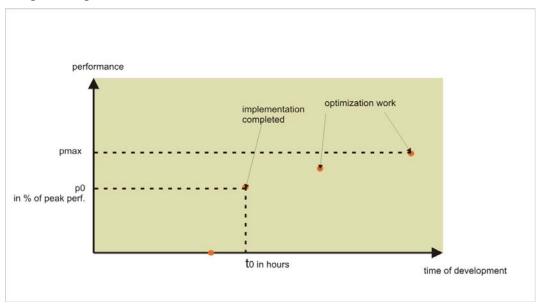

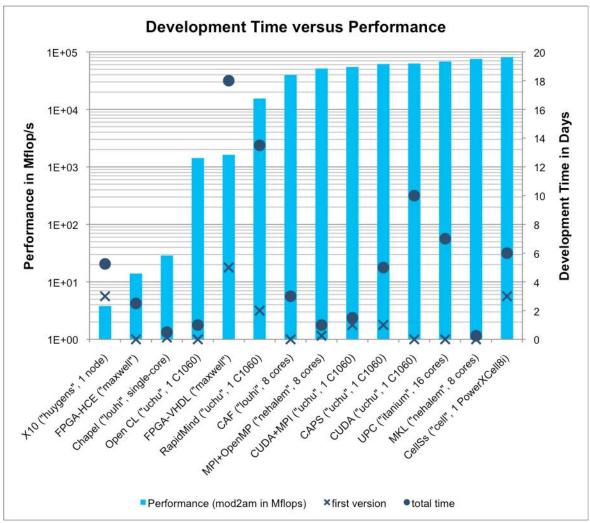

| Figure 11: An example of porting diagram (perfomance vs. time-of-development)                   | 48  |

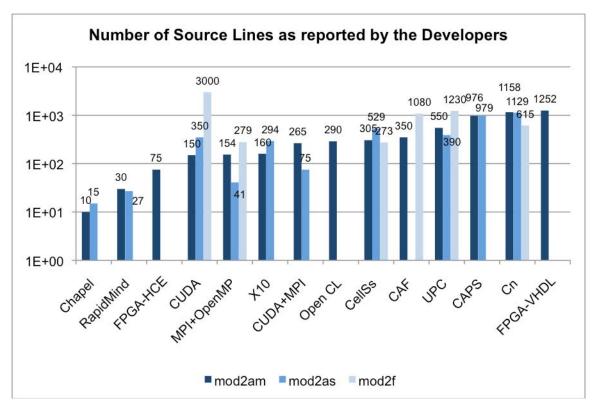

| Figure 12: Overview of the number of source lines for all kernels as reported by the developers | 52  |

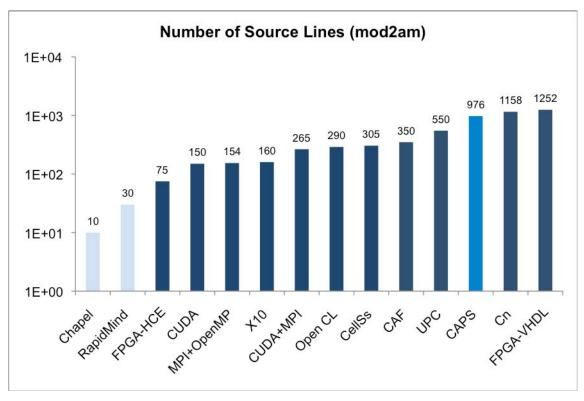

| Figure 13: Number of source lines for mod2am as reported by the developers                      | 52  |

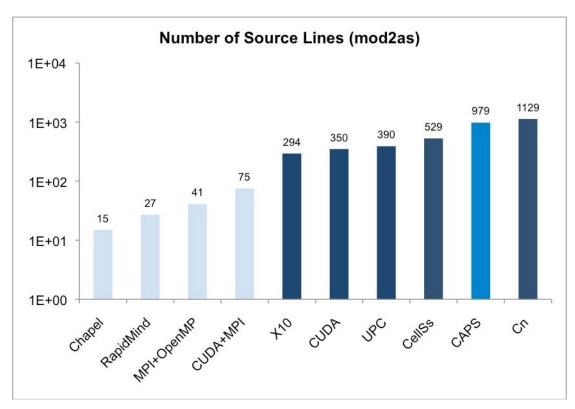

| Figure 14: Number of source lines for mod2as as reported by the developers                      | 53  |

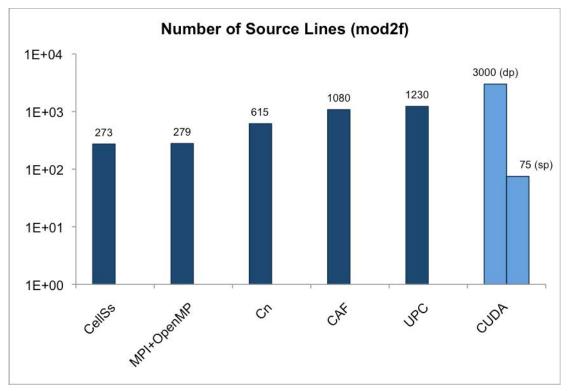

| Figure 15: Number of source lines for mod2f as reported by the developers                       | 53  |

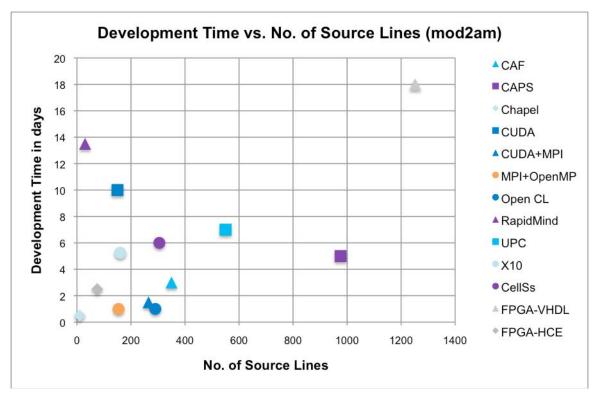

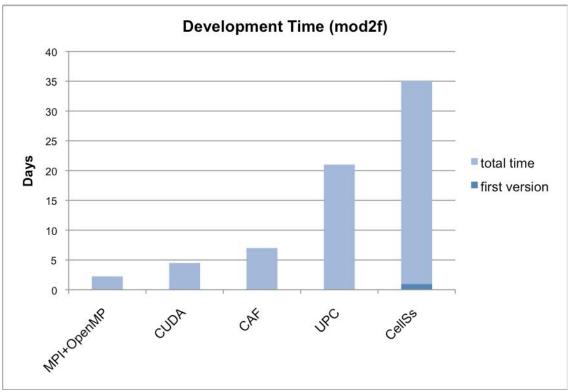

| Figure 16: Development Time vs. Number of Source Lines for mod2am kernel                        |     |

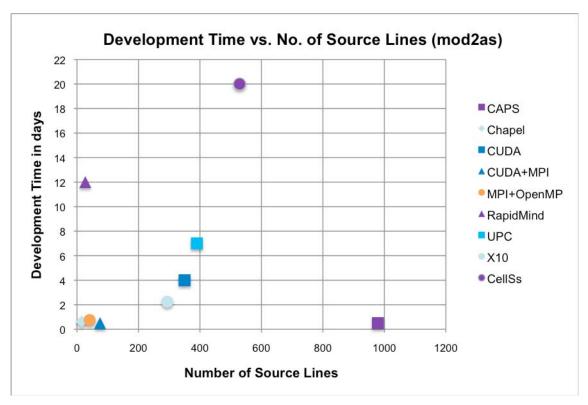

| Figure 17: Development Time vs. Number of Source Lines for mod2as kernel                        |     |

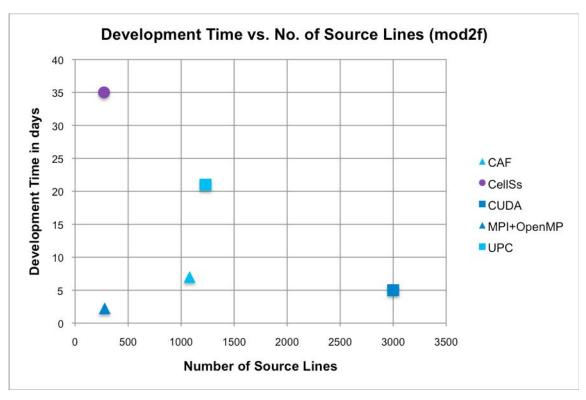

| Figure 18: Development Time vs. Number of Source Lines for mod2f kernel                         |     |

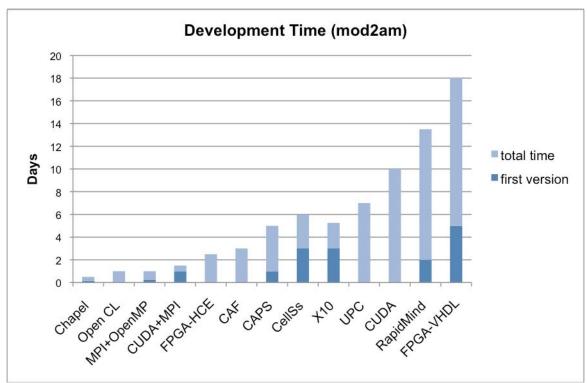

| Figure 19: Comparing Development Time of first and last version of mod2am kernel                |     |

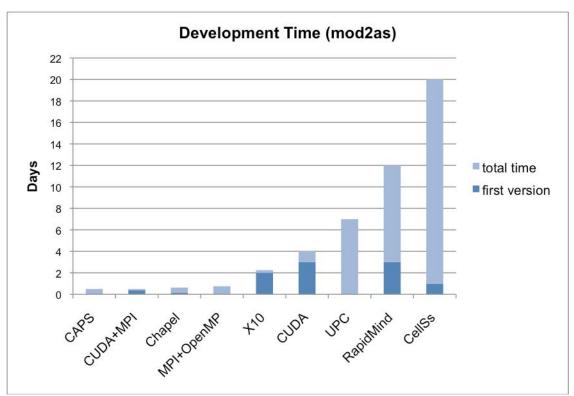

| Figure 20: Comparing Development Time of first and last version of mod2as kernel                |     |

| Figure 21: Comparing Development Time of first and last version of mod2f kernel                 |     |

| Figure 22: Development Time vs. max Performance for mod2am kernel                               |     |

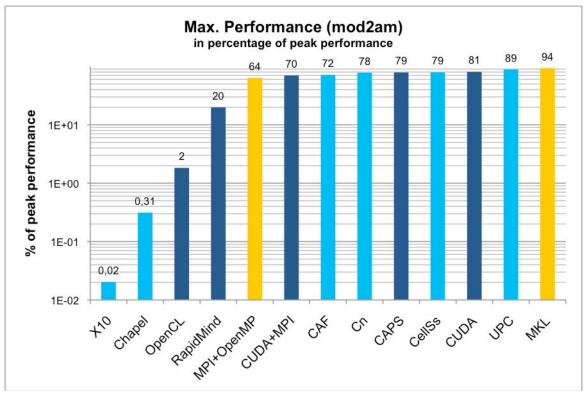

| Figure 23: Maximum performance for mod2am in % of peak performance                              |     |

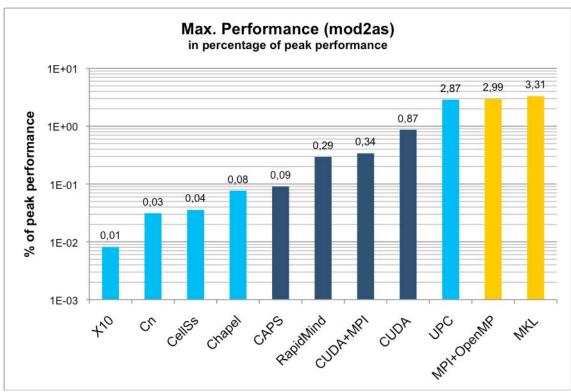

| Figure 24: Maximum Performance for mod2as in % of peak performance                              |     |

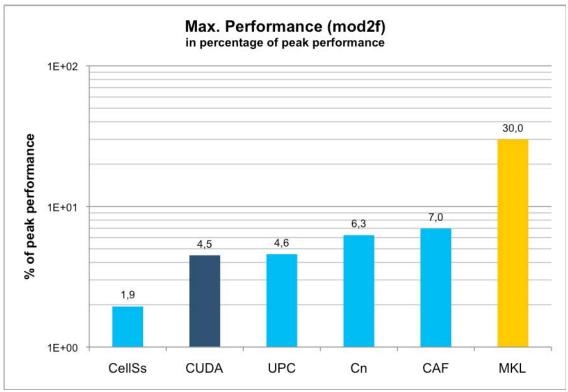

| Figure 25: Maximum Performance for mod2f in % of peak performance                               |     |

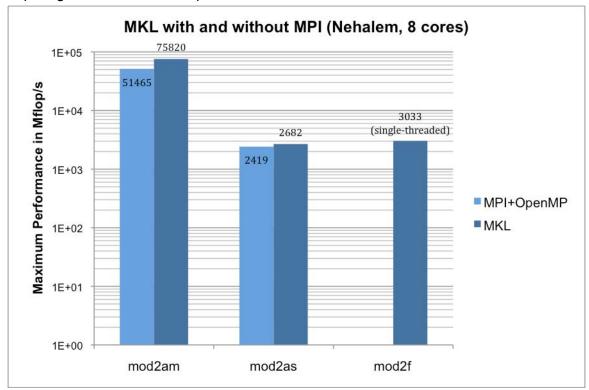

| Figure 26: Performance comparison of MKL with and without MPI (MKL vs. MPI+OpenMP)              |     |

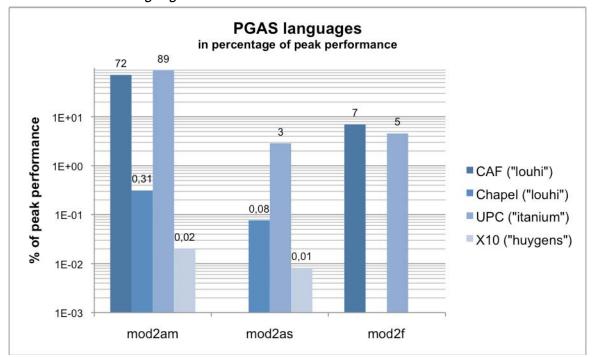

| Figure 27: Performance comparison between PGAS languages                                        |     |

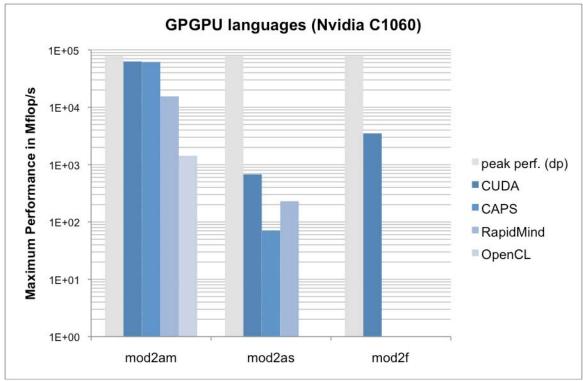

| Figure 28: Performance comparison between GPGPU languages                                       |     |

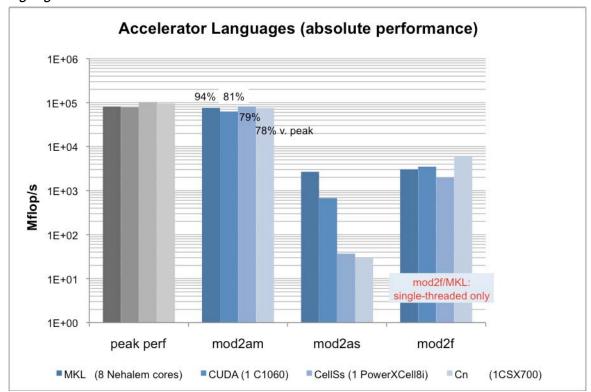

| Figure 29: Performance comparison of languages for different accelerators (in absolute values)  |     |

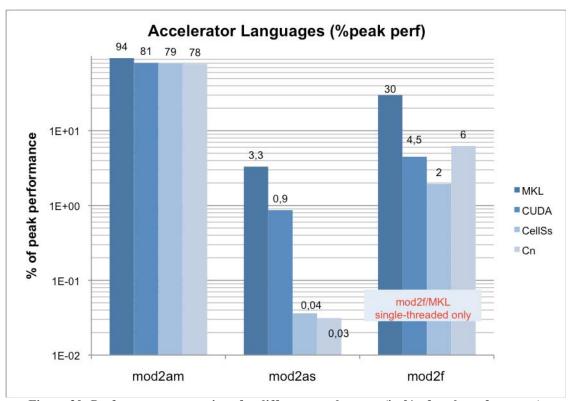

| Figure 30: Performance comparison for different accelerators (in % of peak performance)         |     |

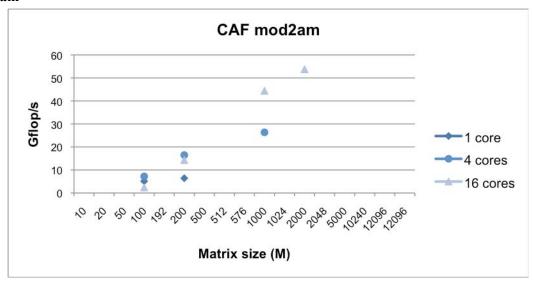

| Figure 31: CAF mod2am performances (tests performed on <i>louhi</i> )                           |     |

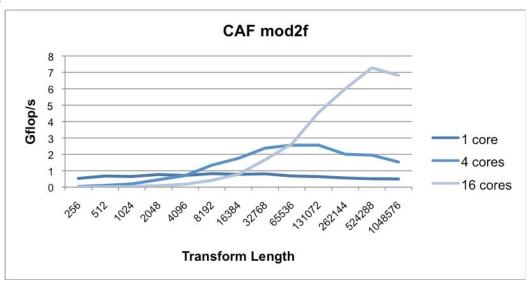

| Figure 32: CAF mod2f performances (tests performed on <i>louhi</i> )                            |     |

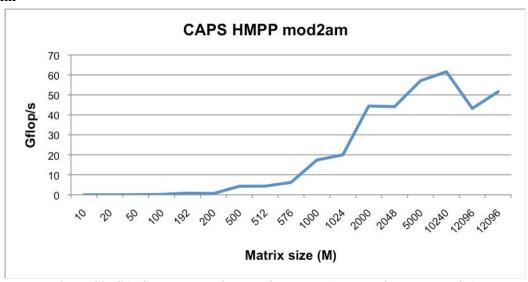

| Figure 33: CAPS HMPP mod2am performances (tests performed on <i>uchu</i> )                      |     |

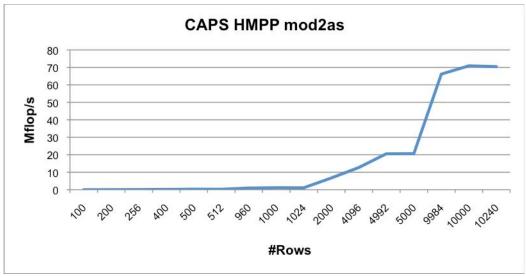

| Figure 34: CAPS HMPP mod2as performances (test performed on <i>uchu</i> )                       |     |

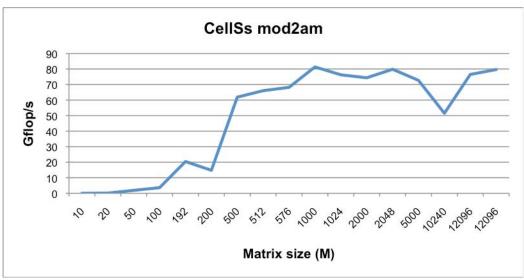

| Figure 35: CellSs mod2am performances (tests performed on <i>maricell</i> )                     |     |

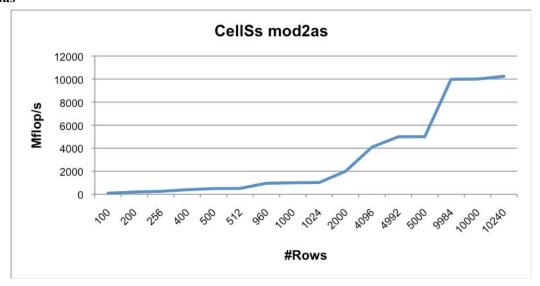

| Figure 36: CellSs mod2as performances (tests performed on maricell)                             |     |

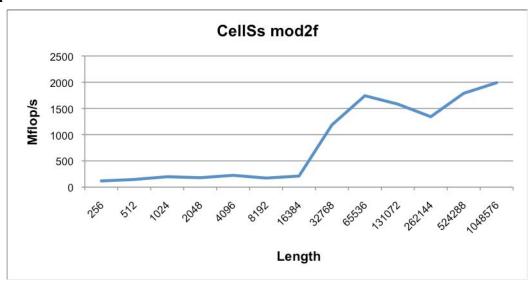

| Figure 37: CellSs mod2f performances (tests performed on <i>cell-cluster</i> )                  |     |

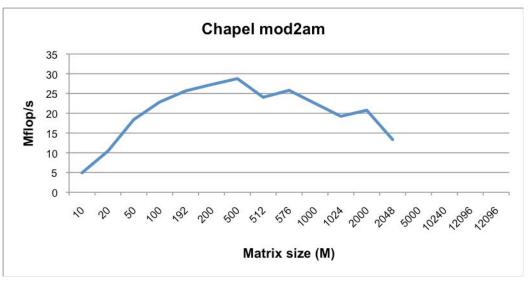

| Figure 38: Chapel mod2am performances (test performed on <i>nehalem/baku</i> )                  |     |

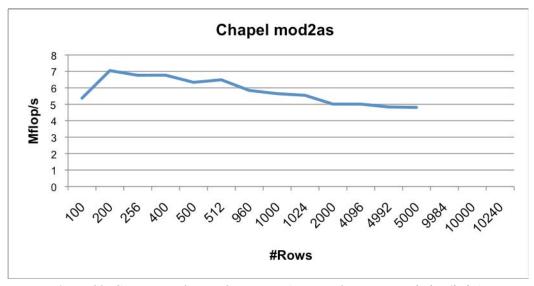

| Figure 39: Chapel mod2as performances (tests performed on <i>nehalem/baku</i> )                 |     |

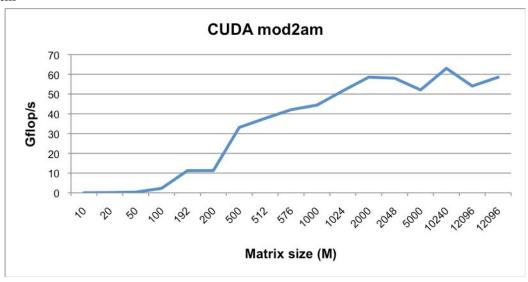

| Figure 40: CUDA mod2am performances (tests performed on <i>uchu</i> )                           |     |

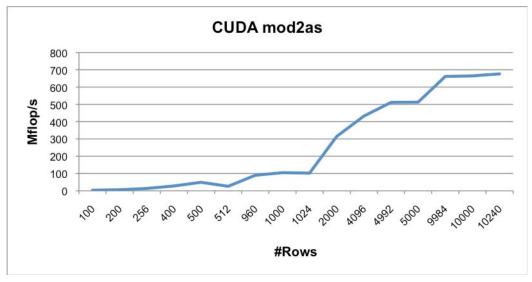

| Figure 41: CUDA mod2as performances (tests performed on <i>uchu</i> )                           |     |

| Figure 42: CUDA mod2f performances (tests performed on <i>uchu</i> )                            |     |

| Figure 43: CUDA+MPI mod2am performances (tests performed on <i>uchu</i> )                       |     |

| Figure 44: CUDA+MPI mod2as performances (test performed on <i>uchu</i> )                        |     |

| Figure 45: MPI+OpenMP mod2am performances (tests performed on <i>inti</i> )                     |     |

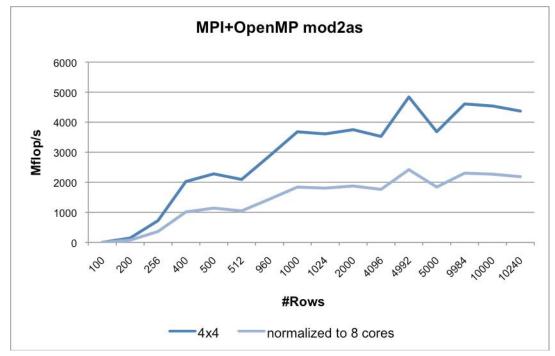

| Figure 46: MPI+OpenMP mod2as performances (tests performed on <i>inti</i> )                     |     |

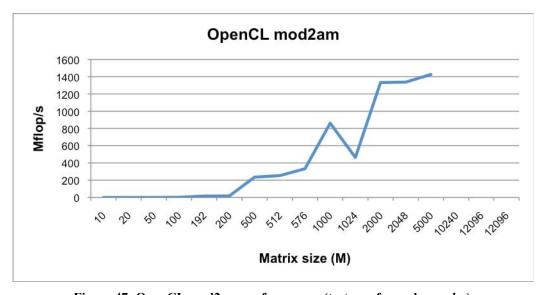

| Figure 47: OpenCL mod2am performances (tests performed on <i>uchu</i> )                         |     |

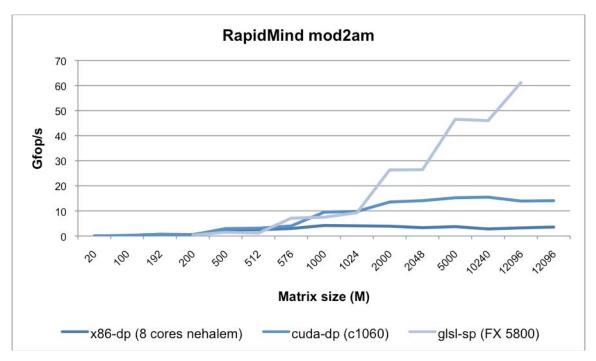

| Figure 48: RapidMind mod2am performances (tests performed on <i>uchu</i> )                      |     |

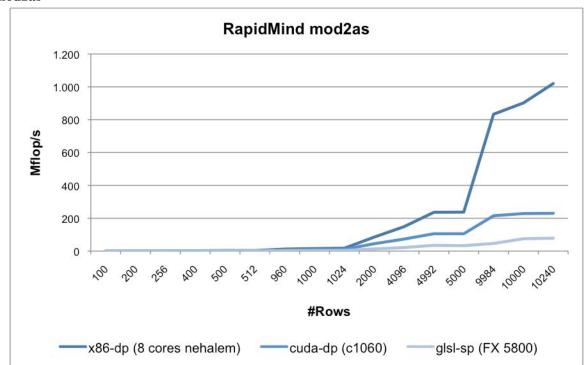

| Figure 49: RapidMind mod2as performances (test performed on <i>uchu</i> )                       |     |

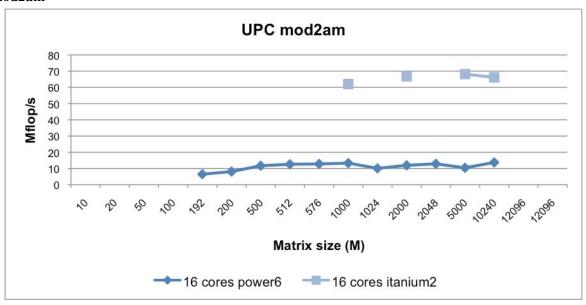

| Figure 50: UPC mod2am performances (tests performed on <i>itanium</i> and <i>huygens</i> )      |     |

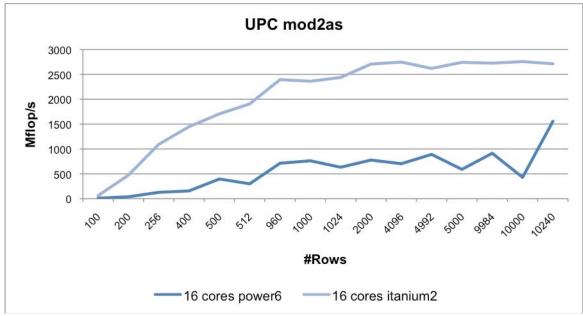

| Figure 51: UPC mod2as performances (tests performed on <i>itanium</i> and <i>huygens</i> )      |     |

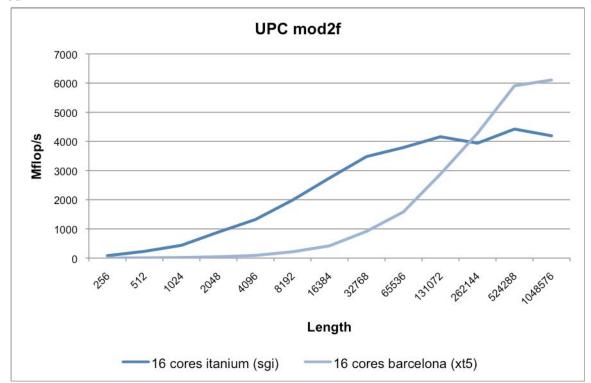

| Figure 52: UPC mod2f performances (tests performed on <i>itanium</i> and <i>louhi</i> )         |     |

| Figure 53: X10 mod2am performances (tests performed on huygens)                                 |     |

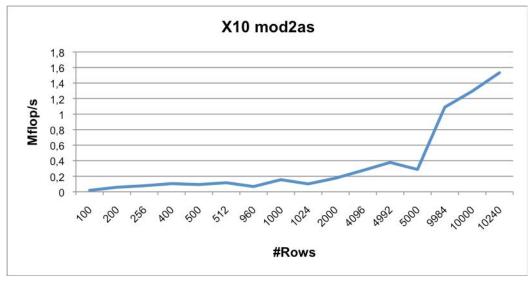

| Figure 54: X10 mod2as performances (tests performed on huygens)                                 |     |

| C                                                                                               | • / |

## **List of Tables**

| Table 1: Classification of PRACE Applications                                               | 6  |

|---------------------------------------------------------------------------------------------|----|

| Table 2: Library categories                                                                 |    |

| Table 3: Classification of most common libraries in PRACE codes                             |    |

| Table 4: Advantages/Disadvantages exhibited by MPI and OpenMP models                        | 13 |

| Table 5: Availability of programming languages for x86 multi-core and hardware accelerators |    |

| Table 6: Vendor implementations of mathematical libraries for hardware accelerators         | 29 |

| Table 7: Mapping of Scientific applications on basic numerical kernels                      | 46 |

| Table 8: Porting status for all kernels                                                     | 49 |

| Table 9: Maximum performance achieved by the kernels                                        | 50 |

| Table 10: Mapping of hardware systems and kernels                                           | 50 |

| Table 11: Reported number of source lines for all kernels                                   | 51 |

| Table 12: Development time for all kernels as reported                                      | 56 |

| Table 13: Performance comparison of languages in percentage of peak performance             | 60 |

| Table 14: Hardware details (peak performance per core or accelerator)                       | 61 |

| Table 15: Pros and Cons of POSIX I/O                                                        | 74 |

| Table 16: Pros and Cons of MPI I/O                                                          | 75 |

| Table 17: Pros and Cons of HDF5 library                                                     | 76 |

| Table 18: Pros and Cons of parallel NetCDF library                                          | 77 |

| Table 19: Parallel IO benchmark using IOR                                                   | 78 |

| Table 20: Parallel IO benchmarking using RAMSES                                             | 79 |

| Table 21: The 4 chosen EUROBEN synthetic kernels                                            | 87 |

| Table 22: RIDS for mod2am                                                                   | 88 |

| Table 23: RIDS for mod2as                                                                   | 89 |

| Table 24: RIDS for mod2f                                                                    | 89 |

| Table 25: RIDS for mod2h                                                                    | 90 |

## **References and Applicable Documents**

- [1] PRACE Deliverable D 6.1, *Identification and categorization of applications and initial benchmark suite* (June 2008)

- [2] PRACE Deliverable D 6.2.2, *Final report of Application requirements* (September 2008)

- [3] Asanovic et. al., *The Landscape of Parallel Computing Research: A View from Berkeley*, Technical Report No. UCB/EECS-2006-183 (2006)

- [4] Top 500 Supercomputer Sites, http://www.top500.org

- [5] The Message Passing Interface standard, http://www.mcs.anl.gov/research/projects/mpi/

- [6] MPI 2.2, https://svn.mpi-forum.org/trac/mpi-forum-web/wiki/MpiTwoTwoWikiPage

- [7] MPI 3.0, http://meetings.mpi-forum.org/MPI 3.0 main page.php

- [8] D. Bonachea, GASNet Specification, U.C. Berkeley Tech Report CSD-02-1207 (2002)

- [9] D. Bonachea and J. Jeong, *GASNet: A Portable High-Performance Communication Layer for Global Address-Space Languages*, CS258 Parallel Computer Architecture Project (2002)

- [10] W. Carlson et. al., *UPC: Distributed Shared Memory Programming*, Book of Wiley Inter-Science (2005)

- [11] IBM UPC Compiler, http://www.alphaworks.ibm.com/tech/upccompiler

- [12] GCC UPC, http://www.intrepid.com/upc.html

- [13] Berkeley UPC, http://upc.lbl.gov

- [14] Michigan Tech MuPC, http://www.upc.mtu.edu

- [15] R. W. Numrich, *F--, A parallel extension to Cray Fortran*, Scientific Programming 6 (1997)

- [16] R. W. Numrich and J. Reid, *Co-Array Fortran for Parallel Programming*, ACM SIGPLAN Fortran Forum 17 (1998)

- [17] G95, http://www.g95.org

- [18] J. Mellor-Crumney et. al., *A critique of Co-Array Features in Fortran 2008* (http://www.j3-Fortran.org/doc/meeting/183/08-126.pdf)

- [19] K. Yelick et. al., Titanium: A High-Performance Java Dialect, In ACM (1998)

- [20] P. N. Hilfinger, *Titanium Language Reference Manual*, technical report of University of California at Berkeley (2001)

- [21] HPJava, http://www.hpjava.org

- [22] Titanium, http://titanium.cs.berkelev.edu

- [23] Chapel Language Specification v0.78, http://chapel.cray.com/spec-0.750.pdf (2008)

- [24] B.L. Chamberlain et. al., *Parallel Programmability and the Chapel Language*, International Journal of High Performance Computing Applications 21 (2007)

- [25] J. Dongarra et. al., *DARPA's HPCS Program: History, Models, Tools, Languages*, Advances in Computers (2008)

- [26] P. Charles et. al., *X10: an object-oriented approach to non-uniform cluster computing*, OOPSLA '05: Proceedings of the 20th annual ACM SIGPLAN conference on Object-oriented programming, systems, languages, and applications (2005)

- [27] X10 language, http://x10-lang.org

- [28] Fortress project, http://research.sun.com/projects/plrg/

- [29] Fortress project, http://projectfortress.sun.com/Projects/Community/

- [30] Intel STM compiler, http://software.intel.com/en-us/articles/intel-c-stm-compiler-prototype-edition-20/

- [31] TL2, http://stamp.stanford.edu/

- [32] RSTM, http://www.cs.rochester.edu/research/synchronization/rstm/

- [33] OpenTM Transactional API, http://opentm.stanford.edu/

- [34] M. Wagner, *Grafikprozessoren als Hardwarebeschleuniger*, Master Thesis @ TU-Dresden (2008)

- [35] CELL, http://www.ibm.com/developerworks/power/cell

- [36] NVIDIA CUDA, http://www.NVIDIA.com/object/cuda\_home.htm

- [37] T. Halfhill, *Parallel Processing with CUDA*, Microprocessor Journal (2008)

- [38] Portland Group, http://www.pgroup.com/resources/accel.htm

- [39] Khronos Group, http://www.khronos.org/opencl

- [40] OpenCL 1.0 Specification, http://www.khronos.org/registry/cl/specs/opencl-1.0.43.pdf (updated May 16, 2009).

- [41] R. Dolbeau et. al., *HMPP: A Hybrid Multi-core Parallel Programming Environment*, In the proceedings of the Workshop on General Purpose Processing on Graphics Processing Units (2007).

- [42] CAPS enterprise, http://www.caps-entreprise.com

- [43] RapidMind, http://www.rapidmind.com

- [44] Sh project, http://libsh.org

- [45] M. McCool et. al., Performance Evaluation of GPUs Using the RapidMind Development Platform, SC06

- [46] P. Bellens et. al., *CellSs: a Programming Model for the Cell BE Architecture*, ACM/IEEE Conference on Supercomputing (2006)

- [47] J. P. Perez, *CellSs: making it easier to program the cell broadband engine processor*, IBM Journal of Research and Development 51 (2007)

- [48] ClearSpeed, http://www.clearspeed.com

- [49] ClearSpeed CSX700, http://www.clearspeed.com/products/documents/CSX700\_Product\_Brief.pdf

- [50] S. Squires et. al., *Software Productivity Research in High Performance Computing*, in "CTWatch Quaterly High Productivity Computing Systems and the Path Towards Usable Petascale Computing Part A: User Productivity Challenges"

- [51] IDRIS *babel* and *vargas* hardware, http://www.idris.fr/eng/Resources/index-babel.html and http://www.idris.fr/eng/Resources/index-vargas.html

- [52] DEISA benchmark, http://www.deisa.eu/science/benchmarking

- [53] IOR benchmark, http://sourceforge.net/projects/ior-sio/

- [54] PRACE Deliverable D 6.3.1, Report on available Performance Analysis and Benchmark Tools, Representative Benchmark.

- [55] K. Kennedy et. al., *Defining and Measuring the Productivity of Programming Languages*, International Journal of High Performance Computing Applications 18 (2004)

- [56] CLOC, http://cloc.sourceforge.net

- [57] S. H. Kan, *Metrics and Models in Software Quality Engineering*, Addison-Wesley Professional (2005)

- [58] S. P. VanderWiel, *Complexity and Performance in Parallel Programming Languages*, International Workshop on High-Level Programming Models and Supportive Environments (1997)

### **List of Acronyms and Abbreviations**

ACML AMD Core Math Library

ALF Accelerated Library Framework

AHTP Advanced HPC Technology Platform. To be created in this project as

permanent groups to identify and work on future technologies for

multi-Petaflop/s systems

AMPI Adaptive MPI

ANSI American National Standards Institute

APGAS Asynchronous Partitioned Global Address Space

API Application Programming Interface

BLACS Basic Linear Algebra Communication Subprograms

BLAS Basic Linear Algebra Subprograms

BSCW Basic Support for Cooperative Work, a collaborative workspace

software package

CAF Coarray Fortran

CFD Computational Fluid Dynamics

CUDA Compute Unified Device Architecture

DARPA Defense Advanced Research Projects Agency, an agency of the U.S.

Department of Defence responsible for the development of new

technology for use by the military.

DEISA Distributed European Infrastructure for Supercomputing

Applications, a EU project by leading national HPC centres

DMA Direct Memory Access

DP Double Precision

ECC Error Correcting Code

EIB Element Interconnect Bus

ESSL Engineering and Scientific Subroutine Library Flop Floating-point operation (1 Mflop/s =  $10^6$  Flop/s)

FFT Fast Fourier Transform

FPGA Field-Programmable Gate Array

General Partner All PRACE partners, excluding the Principal Partners

GPFS General Parallel File System (IBM)

GPGPU General-Purpose Graphic Processing Unit

GPU Graphics Processing Unit

HCE Harwest Compiling Environment

HLL High Level Library

HPC High Performance Computing

HPCS High Productivity Computing Systems, a DARPA project

HTM Hardware Transactional Memory

HWA Hardware Accelerator

D6.6 Report on petascale software libraries and programming models

IEEE Institute of Electrical and Electronics Engineers

IEEE754 IEEE Standard for Floating-Point Arithmetic

ISC International Supercomputing Conference; European equivalent to

the US based Supercomputing conference. Held annually in Germany

LAPACK Linear Algebra PACKage

LEF LINPACK equivalent flops. This is a measure of how many "cycles"

are used for an application, scientific area or other usage measurement where it is spread across different systems. It is essentially utilisation percentage multiplied by the  $R_{\text{max}}$  of a system

and allows summation across systems

LCQD Lattice Quantum Chromo-Dynamics

MASSV Mathematics Acceleration Subsystem for Vectors

MD Molecular Dynamics

MIMD Multiple Instruction Multiple Data

MKL Math Kernel Library

MoU Memorandum of Understanding

MPI Message Passing Interface

MPMD Multiple Program Multiple Data

MTAP Multi-Threaded Array Processors; computing element on ClearSpeed

accelerator cards

NDA Non-Disclosure Agreement

NetCDF Network Common Data Form

OpenMP Open Multi-Processing. An API for shared-memory parallel

programming

PDE Partial Differential Equation

PPE Power Processing Element

PRACE Partnership for Advanced Computing in Europe; project acronym

Principal Partner. The five PRACE partners that have expressed

interest in hosting a future Petaflop/s system

PVM Parallel Virtual Machine

QCD Quantum Chromo-Dynamics

RIDS Reference Input Data Set

SDK Software Development Kit

SIMD Single Instruction Multiple Data

SP Single Precision

SPE Synergistic Processing Element

SPMD Single Process Multiple Data or Single Program Multiple Data

SSE Streaming SIMD Extensions

SSE2 Streaming SIMD Extensions 2

STM Software Transactional Memory

TCC Transactional Coherence and Consistency

D6.6 Report on petascale software libraries and programming models

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the

tier-0 systems; national or topical HPC centres would constitute tier-1

TM Transactional Memory

**UPC** Unified Parallel C

**VHDL** VHSIC Hardware Description Language **VHSIC** Very High Speed Integrated Circuits

Vector Multimedia eXtension **VMX**

WP Work Package

WP5 PRACE Work Package 5, Deployment of prototype systems

WP6 PRACE Work Package 6, Software enabling for Petaflop/s systems

WP7 PRACE Work Package 7, Petaflop/s Systems for 2009/2010

WP8 PRACE Work Package 8, Future Petaflop/s computer technologies

beyond 2010

#### **Executive Summary**

The objective of WP6 Task 6 "Software libraries and programming models" is to understand and evaluate soundness, suitability and efficiency of new programming models, languages and libraries for petascaling applications in the PRACE implementation phase.

The work starts with an analysis of the applications mainly selected in D6.1 and D6.2.2, to better identify the state of the art in the field of programming languages, parallelization schema, programming models and software libraries, adopted by applications on present architectures. From this basis, an accurate survey and analysis of the new upcoming programming models and languages suitable for petascale applications is presented, trying to identify gaps and opportunities provided in terms of performance and efficiency and benefits for parallelism. The survey analyses the current standards for parallel programming and their evolution, the PGAS languages (UPC, CAF, Titanium), the next generation programming languages and models (mainly the languages introduced as a consequence of the DARPA HPCS project: Chapel, X10, Fortress) and then the languages, paradigms and environments for hardware accelerators (Cell programming, CUDA, OpenCL, CAPS HMPP, RapidMind, CellSs and Cn). The assessment of libraries for the petascale systems is presented, ranging from the basic libraries (for basic numerical computations) to I/O libraries, to communication libraries, to special purpose libraries (in charge for tasks not directly related to numerical kernels). Furthermore, to allow a comparative evaluation of new programming paradigms and languages and their soundness for petascaling, a specific experimental activity has been carried out: Three main numerical kernels, have been selected, and ported to twelve of the main programming languages and paradigms under investigation. This work, although qualitative, allowed to assess (for the first time, in a so ample manner) the maturity, the effectiveness, the soundness, and the programming effort of the different new languages and paradigms analyzed. The main findings of the present work are briefly summarised below:

MPI is still the *de facto* standard for HPC, but fundamental limitations are critical for hyper scalability. A more promising approach, to effectively scale up the applications, seems the hybrid programming model, based on coupling message-passing and multi-threading.

Different players are proposing new parallel languages, but none of them appears to be able to reach a production level maturity in the short term, and have a strong impact on the computational community. The DARPA languages still provide very poor performance and the work on them should be better focalised and unified, to be appealing for the HPC community. The PGAS languages could be more promising mainly if a standardisation process will be effective soon.

Hardware accelerators appear to have a big potentiality. Specific languages and programming environments have been defined and experimented in different applicative contexts. At present time it is difficult to identify common directions and guidelines for languages to efficiently exploit accelerators. The general impression is that all these languages are still "hardware driven" and not stable in their evolution. It is highly desirable that some standard will emerge soon in this context; the language on which most people pins their hopes is probably OpenCL. Another important issue in the direction of portability, productivity and performance seems to be represented by tools like RapidMind and the CAPS HMPP, but it is still too early to see what will be the real impact of this kind of tools. Probably a good direction to enhance the programming models for accelerators could be the availability of compilers with specific APIs to allow a semi-automatic code generation.

In summary, the Deliverable presents an analysis of the maturity, suitability, applicability of novel programming models, languages and libraries for Petascaling. The information is valuable also for other WPs, such as WP5, WP7 and WP8.

#### 1 Introduction

The Partnership for Advanced Computing in Europe (PRACE) has the overall objective to prepare for the creation of a persistent pan-European HPC service. PRACE is divided into a number of inter-linked work packages, and WP6 focuses on the software for petascale systems.

The primary goal of PRACE WP6 "Software enabling for Petaflop/s systems" is to identify and understand the software libraries, programming paradigms and languages, tools, benchmarks and skills required by users to ensure that their applications can use a petaflop/s system productively and efficiently. WP6 is the largest of the technical PRACE work packages and involves all of the PRACE partners.

Task 6.6 is responsible for identifying the software libraries and programming models to implement petascaling applications. This is based on the analysis performed in D6.1 ([1]) and D6.2.2 ([2]) on a list of applications, covering a broad range of scientific areas and representative of the workload of today's European HPC systems. The outcome of these two deliverables is used to identify parallelization schemes, software libraries and programming models of these applications on present architectures. Key aspects of this work are the analysis of the current software libraries, their evolution to cope with petascale systems, new programming models and new tools to let current applications scale on petascale machines.

To better evaluate new programming paradigms and languages and their soundness for petascaling, three numerical kernels, typical of the most important computational applications, will be coded, using the main programming languages and paradigms investigated. This coding experience and the consequent porting and assessment on the prototypes selected by WP8, will greatly contribute to better complete the analysis, and evaluate the maturity, the effectiveness, the soundness, but also the programming effort of the different new languages and paradigms analysed. Furthermore, this experience will be useful to better evaluate if applications may find a smooth path toward petascaling, taking advantage of the evolution of the current paradigms, or if a significant re-coding and use of new libraries and new paradigms, or even new language extensions, or new frameworks to exploit the functionality of new accelerators, may represent a more promising approach.

#### 1.1 Objectives

The objective of this work is to analyze in detail the role of new programming languages, programming models, frameworks for accelerators, as well as software libraries, in order to enhance applications to greatly benefit of petascaling systems.

In particular, the main objectives of the deliverable are:

- Identifying the programming models and the software libraries used today in PRACE applications;

- Analyze the evolution of the present programming models and new programming models and languages, and discuss their impact for petascale systems;

- Evaluate the potential of new languages and frameworks on prototype systems (based on hardware accelerators) to speed up applications, presenting some experiments on relevant numerical kernels:

- Evaluate the importance of the software libraries and the potential for optimizations on petascale systems.

#### 1.2 Methodology

First the applications and software libraries already identified and analyzed in previous deliverables are reviewed to extract information about the programming models and software libraries currently used in PRACE applications. Then, the evolution of the main programming models, new languages and frameworks is analyzed to evaluate their pros and cons for applications in the context of petascale systems.

The evaluation of each programming model and language was assigned to the personal of the PRACE project with most experience or with a direct interest on that particular model, but more contributions from other partners are also taken into account. At the end of this phase, three numerical kernels have been selected and implemented using the main programming languages and models investigated, allowing a direct evaluation of these languages on the WP8 prototypes.

Finally software libraries have been analyzed. We have selected the main libraries used in PRACE applications and grouped by category and tagged. After this initial classification, each group has been analyzed by itself, underlying the strengths and weaknesses in a petascale context.

#### 1.3 Structure of the Report

In Chapter 2 the applications identified by PRACE as representatives of the system load in PRACE centres are classified on the base of their parallel programming paradigms. Moreover, the most common software libraries used by the computational applications are classified on the basis of the characteristics relevant for petascale systems.

Chapter 3 analyses the current standards for parallel programming and their evolution (MPI, OpenMP, hybrid programming).

Chapter 4 presents the main features of the PGAS programming model, focusing on the specific implementation in the languages UPC, CAF and Titanium. The next generation programming languages and models, mainly the languages introduced as a consequence of the DARPA HPCS project (Chapel, X10, Fortress) are analysed in Chapter 5.

Chapter 6 introduces the languages, paradigms and environments for hardware accelerators: Cell programming, CUDA, OpenCL, CAPS HMPP, RapidMind, CellSs and Cn.

Chapter 7 focuses on a comparative analysis of the main programming languages and environments introduced in the previous chapters. This activity is accomplished by gathering information during the porting of three numerical kernels to selected languages and benchmarking them on WP8 prototypes.

Finally, Chapter 8 presents an analysis of the scientific libraries and their evolution for the petascale systems, ranging from the basic libraries to I/O libraries, from communication libraries to special purpose libraries.

Some conclusions and final remarks are drawn in Chapter 9. Five specific annexes complete the work.

### 2 Analysis of current HPC applications

The evolution of programming languages, models and software libraries for petascale applications has been addressed starting with the analysis of the programming models and libraries adopted by the current state of the art HPC applications. Deliverable D6.1 and its successor Deliverable D6.2.2 have identified and analysed a list of major applications used by the European scientific community involved in key areas of computational sciences.

In this chapter data previously collected and presented in D6.1 and D6.2.2 about codes is further analyzed to extract information about the programming models and software libraries currently used in PRACE sites and PRACE applications. In particular, applications are classified based on their parallelization paradigm and other characteristics of interest to understand how to scale the applications in petascale systems.

Furthermore, from these deliverables, a list of the scientific libraries used in the main PRACE applications analysed, has been obtained. These libraries are reviewed and classified, to evaluate the real impact of these libraries when used in applications scaling to petascale systems.

There are a huge number of parallel programming languages and models available in literature, many of them have never reached practical relevance for HPC or have the potential to achieve it. Therefore, the analysis covered in this chapter will be also useful to better identify the subset of programming languages and models whose evaluation should be regularly evaluated in light of future petascale systems.

#### 2.1 Current programming models in PRACE application list

In deliverable D6.1 and then in D6.2.2 PRACE partners have compiled a list of applications covering all basic numerical algorithms and representatives of the system load in present HPC systems at PRACE partner sites. The applications in the list are used by all WP6 tasks to analyze application requirements for petascale system, to build a benchmark suite, to evaluate optimization strategies and in general to understand the challenges related to making applications suitable for a petascale system.

The selected applications address almost all fields of computational sciences, covering ten scientific areas and adopting the main algorithmic "dwarves".

The scientific areas are:

- Astronomy and cosmology

- Computational chemistry

- Computational engineering

- Computational fluid dynamics

- Condensed matter physics

- Earth and climate science

- Life science

- Particle physics

- Plasma physics

- Other

The dwarves are those algorithm types which constitute classes where membership in a class is defined by similarity in computation and data movement and was first described from Lawrence Berkeley National Laboratory [3]. A dwarf represents a category of kernels that

share both computational and data structures. The dwarves adopted by the selected applications are:

- Dense linear algebra data is stored in dense matrices or vectors and access is often via unit-level strides. Typical algorithm would be Cholesky decomposition for symmetric systems or Gaussian elimination for non-symmetric systems.

- Sparse linear algebra data is stored in compressed format as it largely consists of zeros and is therefore accessed via an index-based load. Typical algorithm would be Conjugate Gradient or any of the Krylov methods.

- Spectral methods data is in frequency domain and requires a transform to convert to spatial/temporal domain. They are typified by, but not restricted to, FFT.

- Particle methods data consists of discrete particle bodies that interact with each other and/or the "environment".

- Structured grids Represented by a regular grid. Points on the grid are conceptually updated together via equations linking them to other grids. There is high spatial locality. Updates may be in place or between 2 versions of the grid.

- Unstructured grid data is stored in terms of the locality and connectivity to other data. Points on grid are conceptually updated together, but updates require multiple levels of redirection.

- *Map-reduce methods* embarrassingly parallel problems, such as Monte Carlo methods, where calculations are independent of each other.

Identifying the dwarves used in each application is important when analysing the programming model and the parallel paradigm used by the application itself. In facts, the analysis done for an application can be easily extended to a set of different applications characterized by the same dwarves in terms of algorithmic kernels.

In the following we focus on the analysis of the programming model of the applications introduced, with particular attention to the parallelisation paradigm and the analysis of the software libraries adopted by these applications. Table 1 reports the PRACE applications initially selected in D6.2.2 plus some others that were selected later for the PRACE Application Benchmark Suite and for which we already had information. We underline that the final list of applications from the benchmark list has been updated over the time and, actually, some of the applications reported in Table 1 have been discarded while some new applications have been added.

For each application included in Table 1, the main programming model used and the different paradigms introduced are reported. Moreover, for each application it is indicated if the application itself has been benefiting from accelerators or not.

| Application     | Paradigm           | MPI | OpenMP | Other       | Accelerator         |

|-----------------|--------------------|-----|--------|-------------|---------------------|

| NAMD            | Message driven     | yes |        | charm++     | CUDA                |

| CPMD            | Message<br>Passing | yes | yes    |             | CUDA (experimental) |

| VASP            | Message<br>Passing | yes |        |             |                     |

| QCD             | Message<br>Passing | yes |        |             |                     |

| GADGET          | Message<br>Passing | yes |        |             | Experimental (CUDA) |

| Code_Saturne    | Message<br>Passing | yes |        |             |                     |

| TORB            | Message<br>Passing | yes |        |             |                     |

| NEMO            | Message<br>Passing | yes | yes    | autotasking |                     |

| ECHAM5          | Message<br>Passing | yes | yes    |             |                     |

| CP2K            | Message<br>Passing | yes |        |             | CUDA                |

| GROMACS         | Message<br>Passing | yes |        |             | CUDA                |

| NS3D            | Message<br>Passing | yes |        | autotasking |                     |

| QuantumESPRESSO | Message<br>Passing | yes | yes    |             |                     |

| AVBP            | Message<br>Passing | yes |        |             |                     |

| HELIUM          | Message<br>Passing | yes |        |             |                     |

| GPAW            | Message<br>Passing | yes |        |             |                     |

| ALYA            | Message<br>Passing | yes | yes    |             | Cell                |

| BSIT            | Message<br>Passing | yes | yes    |             | Cell                |

| SIESTA          | Message<br>Passing | yes |        |             |                     |

| PEPC            | Message<br>Passing | yes |        |             |                     |

**Table 1: Classification of PRACE Applications**

It can be seen from Table 1 that all the PRACE applications, except one, have been developed using the message-passing parallelization paradigm and the MPI communication library. Only NAMD is written using a message-driven paradigm. Some applications mix the message-passing paradigm with a multi-thread paradigm for the parallelization inside shared memory node. Multi-threading is implemented using OpenMP and in two cases the *autotasking*

implementation is adopted. On the current versions of PRACE codes the support for accelerators is not so common. For CPMD there is an experimental porting on Cell, but this is not jet included in a stable version. For GROMACS exists a special plug-in to use accelerators. NAMD includes the support for GPU in the stable version with a rich set of functionality. For CP2K there is some ongoing activity to exploit accelerators, but so far no production version is available.

From this analysis it turns out that the applications in the list, which represent the load of European Tier-1 systems, are quite similar from the point of view of the parallelization paradigm adopted. This does not necessarily mean that they will arouse similar problems/challenges to enable them for petascale system. This will depend mostly on the communication schema implemented by each application. There could be applications that may already scale well on petascale systems others that will require significant reengineering, or even to change the parallelization paradigm, in fact it is well understood that in many cases applications implemented using the message-passing paradigm fail to scale to high numbers of processors, due to communications overheads and task synchronization. In the next chapters possible alternative parallelization paradigms, useful to remove these bottlenecks, are analyzed in details. Moreover, large room for performance improvement could come from speeding applications with hardware accelerators.

#### 2.2 Current libraries in PRACE application list

Most HPC applications rely on the use of external software libraries that implement standard operations in an efficient and robust way. This is true also for PRACE codes, in fact almost all codes require an external library and in most cases the library is a key component for the code performance, communication, data distribution and scalability. Then it is of fundamental importance to understand how these libraries will behave on petascale systems in order to enable the application itself.

Table 3 summarizes the most common software library either used in PRACE applications list or widely used at PRACE sites. With this table we try to identify the main characteristics of the libraries, relevant to port applications to petascale systems. To improve the analysis, the libraries are tagged and categorized. The set of library categories identified here will then be analyzed in detail in the next chapters. Table 2 contains the list of tags associated to each library category. Since many libraries do not fit in a single category, one or more tags are assigned to each library, which means that the library can fit in all the categories associated to the tags.

| Category              | Tag |

|-----------------------|-----|

| numeric basic library | В   |

| numeric high level    | HL  |

| communication         | С   |

| I/O                   | IO  |

| special purpose       | SP  |

| architecture specific | AS  |

| Low level             | LL  |

| non numeric           | NN  |

**Table 2: Library categories**

Apart from the category, the libraries have been further analyzed to check if they adopt a parallel approach or not. In case a parallel version exists, a further analysis investigates if a multi-threaded version has been implemented and if the library has been ported to hardware accelerators or if a replacement version exists for accelerators. The result of this analysis is reported in Table 3 below.

| Library          | Classification | Version        | Is Parallel?  | Native Multi-<br>threading | Source available |

|------------------|----------------|----------------|---------------|----------------------------|------------------|

| libm             | LL             | -              |               |                            | Y                |

| szlib            | LL             | -              |               |                            | Y                |

| FFTW2            | В              | 2.1.5          | Y             | Y                          | Y                |

| FFTW3            | В              | 3.2.2          |               | Y                          | Y                |

| BLAS             | В              | -              | PBLAS         | Y                          | Y                |

| ESSL             | AS, B + HL     | 4.4            | PESSL         | Y                          |                  |

| ACML             | AS, B          | 4.3.0          |               | Y                          |                  |

| MKL              | AS, B + HL     | 10.2           | Y             | Y                          |                  |

| NAG              | B + HL         | -              | Y             | Y                          |                  |

| LAPACK           | HL             | 3.2.1          | ScaLAPACK     |                            | Y                |

| ScaLAPACK        | HL             | 1.8.0          | Y             |                            | Y                |

| ATLAS            | В              | 3.9.16         |               | Y                          | Y                |

| GOTO             | В              | -              |               | Y                          | Y                |

| METIS            | HL             | 4.0.1          | parMETIS      |                            | Y                |

| GSL              | HL             | 1.13           |               |                            | Y                |

| WSMP             | HL             | 9.9.10         | Y             | Y                          |                  |

| NUMPY            | HL             | 1.3.0          |               |                            | Y                |

| PETSc            | HL             | 3.0.0          | Y             |                            | Y                |

| ARPACK           | HL             | -              | PARPACK       |                            | Y                |

| SPRNG            | HL             | 4.0            | Y             |                            | Y                |

| BLACS            | С              | 1.1            | Y             |                            | Y                |

| CHARM++          | C              | 6.1.2          | Y             |                            | Y                |

| MPI <sup>1</sup> | С              | 2.1            | Y             |                            | Y                |

| CGNS             | IO             | 2.5            | Y             |                            | Y                |

| HDF5             | IO             | 1.8.3 or 1.6.9 | Parallel HDF5 |                            | Y                |

| NetCDF           | IO             | 4.0.1          | pNETCDF       |                            | Y                |

| LibXML           | NN, SP         | -              |               |                            | Y                |

| Tk/Tix           | NN, SP         | -              |               |                            | Y                |

| TCL              | NN, SP         | -              |               |                            | Y                |

Table 3: Classification of most common libraries in PRACE codes

As appears from the Table above, a consistent portion of the scientific libraries analysed offer a parallel version and some others have implemented native multi-threading, but further testing activity should be addressed to check the suitability of the parallel versions to scale up for petascale applications.

<sup>&</sup>lt;sup>1</sup> We refer to the MPI standard specification

## 3 MPI, OpenMP, mixed MPI-OpenMP: current standards and their evolution.

This chapter covers the current *de-facto* standards of parallel programming for applications able to run over the largest HPC systems in Europe. For each section, a short description of their main features is given. Also, where possible, we give a look to their proximal future evolution.

#### 3.1 MPI

Message Passing Interface (MPI, [5]) is the current *de-facto* standard for programming distributed memory architectures, and is used in the vast majority of current HPC applications. Deliverable D6.1 surveyed 69 of the most heavily used applications running on PRACE centre machines. Of these, 67 were designed for distributed memory systems, and all of them were programmed using MPI. MPI consists of a subroutine library with interfaces in Fortran, C and C++.

#### 3.1.1 Current standard (MPI 2.2)

The first version of the MPI standard (version 1.0) was published in 1994. A significant set of extensions to the library (version 2.0) followed in 1997, published as a separate document. Version 2.2, published in September 2009, essentially combines versions 1.0 and 2.0, with corrections, into a single document. Version 2.2 contains also minor updates and corrections to Version 2.1. These minor changes may include a few additional routines, and the addition of functionality to existing routines. The status of the discussions about Version 2.2 is public, and can be viewed at [6]. The full history of document versions is rather convoluted: a good summary is given in the introduction to Version 2.2.

#### 3.1.2 Overview of support in current implementations

The majority of MPI implementations support MPI 2.x, with the exception of the dynamic process creation routines (Chapter 10 of Version 2.2), which may not be supported on HPC systems with very minimal operating systems running on the compute nodes.

#### 3.1.3 Future: MPI 3.0

The MPI Forum is now focusing its efforts on the new version of the standard. MPI Version 3.0 will contain significant extensions to Version 2.x. This is at an early stage in the standardisation process, but some of the major areas being considered are as follows:

- 1. definition of an ABI (Application Binary Interface) to support linkage compatibility between different MPI implementations on a platform;

- 2. enhancements to collective operations, including

- a. persistent collective operations to allow optimisation where the same collective operations are repeated many times;

- b. new collective operations, including MPI\_Reduce\_scatter\_block;

- c. sparse collectives, where the participating tasks form a subset of the tasks in a communicator;

- d. non-blocking versions of collective operations;

- 3. fault tolerance;

- 4. improved Fortran bindings;

- 5. extensions to generalised requests;

- 6. improved support for tools (especially debuggers);

- 7. improved support for hybrid programming, including the possibility of treating threads as MPI processes.

Again, the status of the discussions about Version 3.0 is public, and can be viewed by following the links from [7].

Of the topics under discussion, it seems likely that items 2c, 2d and 7 above are the most likely to have immediate applicability for mainstream HPC applications.

#### 3.2 OpenMP

OpenMP is the current *de-facto* standard for programming shared memory architectures. The OpenMP API consists of compiler directives, runtime library routines and environment variables. Since no large-scale HPC systems have pure shared memory architecture, pure OpenMP programs cannot be run at large scale on the current generation of supercomputers. However, with the advent of SMP clusters, and more recently, of multi-core processors, OpenMP is of increasing interest in mixed-mode (or hybrid) MPI+OpenMP implementations of applications: see Section 3.3.

#### 3.2.1 Current standard (OpenMP 3.0)

The current version of OpenMP is Version 3.0, released in 2008. The major changes from Version 2.5 are as follows:

- The addition of support for task parallelism via the *task* and *taskwait* constructs. A task construct identifies a block of computation that can be executed by any thread in the current team at some point in the future. Tasks can be arbitrarily nested: i.e. one task may contain child tasks, grandchild tasks, etc. When a barrier is encountered, all generated tasks must complete before the threads exit the barrier. The taskwait directive is used to ensure that all immediate child tasks of the current task have completed. OpenMP tasks are a very convenient mechanism for exploiting parallelism in loops with an unknown iteration count (e.g. while loops), and recursive parallelism.

- Better support for nested parallelism including per-thread internal control variables (allowing, for example "omp\_set\_num\_threads()" to be called inside parallel regions), and new runtime library routines to determine depth of nesting, IDs of parent/grandparent etc. threads, and team sizes of parent/grandparent etc. teams.

- Additional support for loop parallelism, including the ability for OpenMP loop directives to parallelise perfect loop nests, a new schedule kind (auto) which allows the runtime to choose the best schedule for the loop, and library routines to get and set the schedule kind at runtime.