# E-Infrastructures H2020-EINFRA-2016-2017

# EINFRA-11-2016: Support to the next implementation phase of Pan-European High Performance Computing Infrastructure and Services (PRACE)

### PRACE-5IP

## **PRACE Fifth Implementation Phase Project**

**Grant Agreement Number: EINFRA-730913**

**D5.6**

Extended best practice guide for prototypes and demonstrators Final

Version: 1.0

Author(s): Hayk Shoukourian (BADW-LRZ)

Date: 08.04.2019

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: EINFRA-730913                                                                                      |                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|               | <b>Project Title: Extended </b> l                                                                                  | best practice guide for prototypes and |

|               | demonstrators                                                                                                      |                                        |

|               |                                                                                                                    |                                        |

|               | <b>Project Web Site:</b> <a href="https://doi.org/10.2016/j.jps.100.000">https://doi.org/10.2016/j.jps.100.000</a> | o://www.prace-project.eu               |

|               | <b>Deliverable ID:</b> D5.                                                                                         | 6                                      |

|               | Deliverable Nature: Rep                                                                                            | oort                                   |

|               | <b>Dissemination Level:</b>                                                                                        | Contractual Date of Delivery:          |

|               | PU*                                                                                                                | 30 / April / 2019                      |

|               |                                                                                                                    | Actual Date of Delivery:               |

|               |                                                                                                                    | 30 / April / 2019                      |

|               | EC Project Officer: Leon                                                                                           | nardo Flores Añover                    |

<sup>\*</sup> **PU** – Public

### **Document Control Sheet**

|            | Title: Extended best practice guide for prototypes and |                               |  |

|------------|--------------------------------------------------------|-------------------------------|--|

| Document   | demonstrators                                          |                               |  |

|            | ID: D5.6                                               |                               |  |

|            | Version: 1.1                                           | Status: Final                 |  |

|            | <b>Available at:</b> <a href="http://w">http://w</a>   | ww.prace-project.eu           |  |

|            | <b>Software Tool:</b> Micros                           | oft Word 2013                 |  |

|            | <b>File(s):</b> PRACE                                  | E-5IP-D5.6_v1.0-1_JL          |  |

|            | Written by:                                            | Hayk Shoukourian (BADW-LRZ)   |  |

| Authorship |                                                        |                               |  |

|            | <b>Contributors:</b>                                   | Carlo Cavazzoni (CINECA)      |  |

|            |                                                        | Giannis Koutsou (CaSToRC)     |  |

|            |                                                        | Radosław Januszewski (PSNC)   |  |

|            |                                                        | Walter Lioen (SURFsara)       |  |

|            |                                                        | Philippe Segers (GENCI)       |  |

|            |                                                        | Volker Weinberg (BADW-LRZ)    |  |

|            | Reviewed by:                                           | Massimiliano Guarrasi, CINECA |  |

|            |                                                        | Thomas Eickermann, JUELICH    |  |

|            | Approved by:                                           | MB/TB                         |  |

## **Document Status Sheet**

| Version | Date           | Status | Comments                          |

|---------|----------------|--------|-----------------------------------|

| 0.1     | 14/May/2018    | Draft  | Skeleton, the very first draft.   |

| 0.2     | 01/August/2018 | Draft  | Assembly of some information from |

|       |                  | _          |                                                 |

|-------|------------------|------------|-------------------------------------------------|

|       |                  |            | ISC'18. First complete draft for Sections 5 and |

|       |                  |            | 6. Skeleton for Section 4                       |

|       |                  |            | including the data from                         |

|       |                  |            | survey. Finalizing the                          |

|       |                  |            | document for                                    |

|       |                  |            | distribution to WP5 T3                          |

|       |                  |            | partners with an input                          |

|       |                  |            | request.                                        |

| 0.3   | 07/October/2018  | Draft      | Additional input for                            |

|       |                  |            | sections 5 and 6 obtained                       |

|       |                  |            | from Giannis Koutsou                            |

|       |                  |            | (CaSToRC).                                      |

| 0.4   | 03/December/2018 | Draft      | Input from Walter Lioen                         |

|       |                  |            | (PRACE 5IP WP7                                  |

|       |                  |            | representative) regarding                       |

|       |                  |            | sections 5 and 6.                               |

| 0.5   | 16/January/2019  | Draft      | Input from Carlo                                |

|       |                  |            | Cavazzoni (CINECA)                              |

|       |                  |            | for section 3.                                  |

| 0.6   | 12/February/2019 | Draft      | Input from Radosław                             |

|       |                  |            | Januszewski (PSNC) for                          |

|       |                  |            | section 4. First complete                       |

|       |                  |            | draft of introduction and                       |

|       |                  |            | conclusion sections.                            |

| 0.7   | 28/February/2019 | Draft      | Includes comments and                           |

|       |                  |            | fixes from Giannis                              |

|       |                  |            | Koutsou (CaSToRC) and                           |

|       |                  |            | Hayk Shoukourian                                |

|       |                  |            | (LRZ).                                          |

| 0.7.1 | 11/March/2019    | Draft      | Additional input on PCP                         |

|       |                  |            | and EuroHPC from                                |

|       |                  |            | Philippe Segers                                 |

|       |                  |            | (GENCI).                                        |

| 0.8   | 12/March/2019    | Draft      | Version submitted for                           |

|       |                  |            | WP5-internal review.                            |

| 0.8.1 | 27/March/2019    | Semi-final | Version submitted for                           |

|       |                  |            | PRACE internal review.                          |

| 1.0   | 08/April/2019    | Final      | Addressing                                      |

|       |                  |            | comments/suggestions                            |

|       |                  |            | from reviewers                                  |

|       |                  |            |                                                 |

### **Document Keywords**

#### Disclaimer

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° EINFRA-730913. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2019 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract EINFRA-730913 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

## **Table of Contents**

| D  | ocum     | ent Control Sheet                                     | i    |

|----|----------|-------------------------------------------------------|------|

| D  | ocum     | ent Status Sheet                                      | i    |

| D  | ocum     | ent Keywords                                          | iii  |

| Li | ist of l | Figures                                               | v    |

| Li | ist of ' | Гables                                                | v    |

| R  | eferen   | ces and Applicable Documents                          | v    |

| Li | ist of A | Acronyms and Abbreviations                            | viii |

| Li | ist of l | Project Partner Acronyms                              | ix   |

| E  | xecuti   | ve Summary                                            | 1    |

| 1  | Int      | roduction                                             | 2    |

| 2  | Sur      | vey                                                   | 3    |

| 3  | Co-      | design opportunities                                  | 3    |

|    | 3.1      | Co-design at the chip level                           | 4    |

|    | 3.2      | Co-design at the integration level                    | 4    |

|    | 3.3      | Co-design for networking                              | 4    |

|    | 3.4      | Co-design for energy management                       | 5    |

|    | 3.5      | Co-design for libraries                               | 5    |

|    | 3.6      | Co-design for compiler/programming standards          | 6    |

|    | 3.7      | Co-design for data management/processing              | 6    |

|    | 3.8      | Co-design for specific HPC workloads                  | 6    |

| 4  | Che      | ecklist of system and development tools               | 6    |

|    | 4.1      | Resource management and scheduling system             | 8    |

|    | 4.2      | Parallel filesystem                                   | 9    |

|    | 4.3      | Application libraries                                 | 10   |

|    | 4.4      | Development tools                                     | 11   |

|    | 4.5      | Performance monitoring tools                          | 12   |

| 5  | Des      | scription of benchmarks used for prototype evaluation | 14   |

| 6  | Ma       | in KPIs used for prototype evaluation                 | 24   |

| 7  | Cor      | nclusions                                             | 25   |

# **List of Figures**

| _     | re 1 The minimum requirements of PRACE Tier-0/Tier-1 sites in terms of libraries, tools,                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | that should be installed on a system before it gets accessed by general HPC users8                                                                                     |

|       | re 2 Resource management and scheduling systems currently used at PRACE Tier-0/Tier-1                                                                                  |

|       | 9 2 Devellal file contains around to DDA CE Time 0/Time 1 cites                                                                                                        |

| _     | re 3 Parallel file system currently used at PRACE Tier-0/Tier-1 sites                                                                                                  |

| _     | re 4 The minimum requirements of PRACE Tier-0/Tier-1 sites in terms of application                                                                                     |

|       | ries (e.g. MPI, Math libraries, etc.) that should be installed on a system before it gets                                                                              |

|       | ssed by general HPC users 11                                                                                                                                           |

| _     | are 5 The minimum requirements of PRACE Tier-0/Tier-1 sites in terms of development tools                                                                              |

| _     | compilers, debugging tools, etc.) that should be installed on a system before it gets accessed                                                                         |

|       | eneral HPC users                                                                                                                                                       |

| _     | itoring tools that should be installed on a system before it gets accessed by general HPC                                                                              |

|       | s13                                                                                                                                                                    |

|       | re 7 Relaxation policy of system software stack requirements at PRACE Tier-0/Tier-1 sites                                                                              |

| _     |                                                                                                                                                                        |

|       | re 8 Usage of different benchmarks for prototype evaluation at PRACE Tier-0/Tier-1 HPC                                                                                 |

| _     | 15                                                                                                                                                                     |

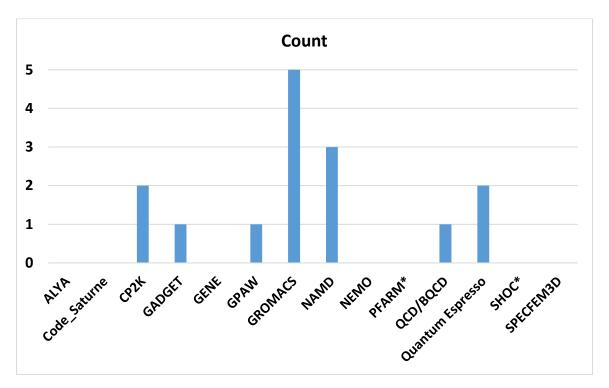

|       | re 9 Usage of different benchmarks within UEABS for prototype evaluation at PRACE Tier-                                                                                |

| _     | er-1 HPC sites                                                                                                                                                         |

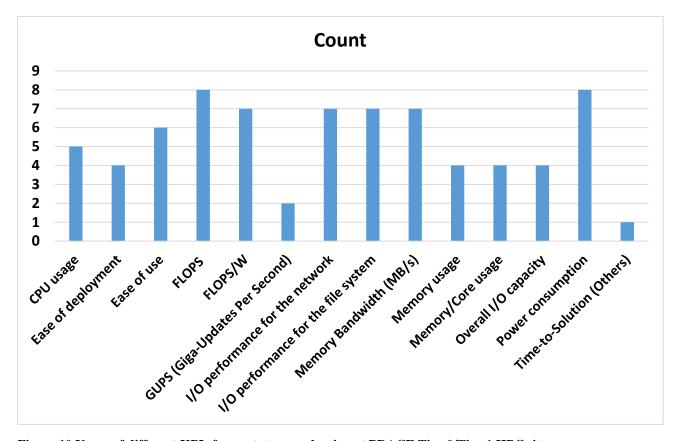

|       | re 10 Usage of different KPIs for prototype evaluation at PRACE Tier-0/Tier-1 HPC sites .24                                                                            |

|       |                                                                                                                                                                        |

|       |                                                                                                                                                                        |

|       | List of Tables                                                                                                                                                         |

|       | e 1: List of PRACE Tier-0/Tier-1 sites that participated in the survey                                                                                                 |

|       | e 2 Description of benchmarks used for prototype evaluation by PRACE TIer-0/Tier-1 HPC                                                                                 |

|       | 17                                                                                                                                                                     |

|       | e 3 Short description of benchmarks within UEABS [38]                                                                                                                  |

| 1 abi | e 4 Short description of some emerging Big Data and AI/ML specific benchmarks24                                                                                        |

|       |                                                                                                                                                                        |

|       | References and Applicable Documents                                                                                                                                    |

| 543   |                                                                                                                                                                        |

| [1]   | PRACE-5IP Deliverable D5.5 "Requirements of new user communities for the use of next                                                                                   |

|       | generation computing systems evolving towards Exascale", 2018                                                                                                          |

| [2]   | http://www.prace-ri.eu/                                                                                                                                                |

| [3]   |                                                                                                                                                                        |

|       | PRACE-4IP Deliverable D5.6 "Best Practices for Prototype Planning and Evaluation",                                                                                     |

|       | 2017                                                                                                                                                                   |

| [4]   | 2017 <a href="http://www.prace-ri.eu/prace-4ip/">http://www.prace-ri.eu/prace-4ip/</a>                                                                                 |

| [5]   | 2017 <a href="http://www.prace-ri.eu/prace-4ip/">http://www.prace-ri.eu/prace-4ip/</a> <a href="http://www.prace-ri.eu/prace-pp/">http://www.prace-ri.eu/prace-pp/</a> |

|       | 2017 <a href="http://www.prace-ri.eu/prace-4ip/">http://www.prace-ri.eu/prace-4ip/</a>                                                                                 |

- [8] <a href="http://www.prace-ri.eu/prace-3ip/">http://www.prace-ri.eu/prace-3ip/</a>

- [9] <a href="http://montblanc-project.eu/">http://montblanc-project.eu/</a>

- [10] http://www.deep-project.eu/deep-project/EN/Home/home\_node.html

- [11] http://hpc.desy.de/qpace/

- [12] <a href="https://www.cineca.it/">https://www.cineca.it/</a>

- [13] https://www.cyi.ac.cy/index.php/castorc/about-the-center/castorc-center-overview.html

- [14] https://www.csc.fi/

- [15] https://www.lrz.de/english/

- [16] <a href="https://grnet.gr/en/">https://grnet.gr/en/</a>

- [17] https://www.edu.unideb.hu/

- [18] <a href="http://www.man.poznan.pl/online/en/">http://www.man.poznan.pl/online/en/</a>

- [19] <a href="https://pg.edu.pl/welcome?p\_1\_id=52858455&p\_1\_id=2601414&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_id=0&p\_v\_1\_s\_g\_

- [20] <a href="https://www.hartree.stfc.ac.uk/Pages/home.aspx">https://www.hartree.stfc.ac.uk/Pages/home.aspx</a>

- [21] PRACE-4IP Deliverable D5.5 "Application and HPC Centre Requirements for Prototyping"; 2016

- [22] <a href="https://ec.europa.eu/digital-single-market/en/news/european-processor-initiative-consortium-develop-europes-microprocessors-future-supercomputers">https://ec.europa.eu/digital-single-market/en/news/european-processor-initiative-consortium-develop-europes-microprocessors-future-supercomputers</a>

- [23] <a href="https://www.scd.stfc.ac.uk/Pages/DL\_POLY.aspx">https://www.scd.stfc.ac.uk/Pages/DL\_POLY.aspx</a>

- [24] www.ucolick.org/~zingale/flash\_benchmark\_io/

- [25] https://computing.llnl.gov/?set=code&page=sio\_downloads

- [26] <a href="https://software.intel.com/en-us/articles/intel-mpi-benchmarks">https://software.intel.com/en-us/articles/intel-mpi-benchmarks</a>

- [27] http://www.hpcg-benchmark.org/

- [28] https://www.top500.org/

- [29] http://www.netlib.org/benchmark/hpl/

- [30] https://github.com/luizbafilho/hydra

- [31] Carrington, Laura C., Michael Laurenzano, Allan Snavely, Roy L. Campbell, and Larry P. Davis. "How well can simple metrics represent the performance of HPC applications?." In Supercomputing, 2005. Proceedings of the ACM/IEEE SC 2005 Conference, pp. 48-48. IEEE, 2005

- [32] https://www.nas.nasa.gov/publications/npb.html

- [33] <a href="https://www.intel.com.tw/content/www/tw/zh/design/test-and-validate/platform-testing-services/power-supply-testing.html">https://www.intel.com.tw/content/www/tw/zh/design/test-and-validate/platform-testing-services/power-supply-testing.html</a>

- [34] Stone, H. L. (1968). "Iterative Solution of Implicit Approximations of Multidimensional Partial Differential Equations". SIAM Journal of Numerical Analysis. 5 (3): 530–538. DOI:10.1137/0705044

- [35] Hager G., Deserno F., Wellein G.: Pseudo-Vectorization and RISC Optimization Techniques for the Hitachi SR8000 Architecture. In: Wagner S., Bode A., Hanke W., Durst F. (eds) High Performance Computing in Science and Engineering, Munich 2002. Springer, Berlin, Heidelberg. DOI:10.1007/978-3-642-55526-8\_34

- [36] Que, Xinyu, Lars Schneidenbach, Fabio Checconi, Carlos HÃ Costa, and Daniele Buono. "Performance Analysis of Spark/GraphX on POWER8 Cluster." In International Conference on High Performance Computing, pp. 268-285. Springer, Cham, 2016

- [37] https://www.cs.virginia.edu/stream/

- [38] https://repository.prace-ri.eu/git/UEABS/ueabs

- [39] http://www.prace-ri.eu/IMG/pdf/D7.7\_v1.2\_4ip.pdf

- [40] S. Matsuoka, "From TSUBAME to ABCI onto Post-K: Convergence of HPC and AI in Exascale", HPC w/ARM workshop, Shanghai, July 2018, <a href="https://hpc.sjtu.edu.cn/HPCARMChina20180721matsuoka.pdf">https://hpc.sjtu.edu.cn/HPCARMChina20180721matsuoka.pdf</a>

- [41] https://abci.ai/jp/about\_abci/

- [42] http://www.tpc.org

- [43] Fox, G., Jha, S., Qiu, J., Ekanazake, S. and Luckow, A., 2015. Towards a comprehensive set of big data benchmarks. Big Data and High Performance Computing, 26, p.47.

- [44] <a href="https://github.com/intel-hadoop/Big-Data-Benchmark-for-Big-Bench">https://github.com/intel-hadoop/Big-Data-Benchmark-for-Big-Bench</a>

- [45] Wang, L., Zhan, J., Luo, C., Zhu, Y., Yang, Q., He, Y., Gao, W., Jia, Z., Shi, Y., Zhang, S. and Zheng, C., 2014, February. Bigdatabench: A big data benchmark suite from internet services. In High Performance Computer Architecture (HPCA), 2014 IEEE 20th International Symposium on (pp. 488-499). IEEE.

- [46] <a href="http://prof.ict.ac.cn/">http://prof.ict.ac.cn/</a>

- [47] <a href="https://github.com/bigframeteam/BigFrame">https://github.com/bigframeteam/BigFrame</a>

- [48] https://graph500.org/

- [49] https://amplab.cs.berkeley.edu/benchmark/

- [50] <a href="https://github.com/intel-hadoop/HiBench">https://github.com/intel-hadoop/HiBench</a>

- [51] <a href="http://cloudsuite.ch/">http://cloudsuite.ch/</a>

- [52] <a href="https://github.com/brianfrankcooper/YCSB/wiki">https://github.com/brianfrankcooper/YCSB/wiki</a>

- [53] https://www.spec.org/

- [54] <a href="https://www.spec.org/events/beijing2016/slides/005-SPEC-RG%20Big%20Data%20Overview%20-%20Xiao%20Wei%20Zhang.pdf">https://www.spec.org/events/beijing2016/slides/005-SPEC-RG%20Big%20Data%20Overview%20-%20Xiao%20Wei%20Zhang.pdf</a>

- [55] https://github.com/google/gemmlowp

- [56] https://svail.github.io/DeepBench/

- [57] https://mlperf.org/

- [58] https://github.com/mlperf/reference

- [59] http://deep500.org/

- [60] <a href="https://www.hpcwire.com/2019/01/07/the-deep500-researchers-tackle-an-hpc-benchmark-for-deep-learning/">https://www.hpcwire.com/2019/01/07/the-deep500-researchers-tackle-an-hpc-benchmark-for-deep-learning/</a>

- [61] https://github.com/deep500/deep500

- [62] <a href="https://www.hpcwire.com/2019/02/05/deep500-eth-researchers-introduce-new-deep-learning-benchmark-for-hpc/">https://www.hpcwire.com/2019/02/05/deep500-eth-researchers-introduce-new-deep-learning-benchmark-for-hpc/</a>

## **List of Acronyms and Abbreviations**

AI Artificial Intelligence

CoE Center of Excellence

CPU Central Processing Unit

DDR Double Data Rate

DEISA Distributed European Infrastructure for Supercomputing Applications

FLOPS Floating Point Operations Per Second

FPGA Field-programmable gate array

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also Gbyte Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also Gbyte/s

GDDR Graphics DDR

GEMM General Matrix Multiplication

GHz Giga (=  $10^9$ ) Hertz, frequency =  $10^9$  periods or clock cycles per second

GPU Graphic Processing Unit HBM High Bandwidth Memory HDF Hierarchical Data Format

HPC High Performance Computing; Computing at a high performance level at any

given time; often used synonym with Supercomputing

HPCG High Performance Conjugate Gradients

HPL High Performance LINPACK

HW Hardware

IMB Intel MPI Benchmarks

IOR Interleaved Or Random

I/O Input/Output

KPI Key Performance Indicator

ML Machine Learning

MPI Message Passing Interface

NASA National Aeronautics and Space Administration

NVM Non Volatile Memory

PCP Pre-Commercial Procurement

PRACE Partnership for Advanced Computing in Europe; Project Acronym

PTU Power Thermal Utility

SIP Strongly-Implicit Procedure

SPEC Standard Performance Evaluation Corporation

SW Software

TDP Thermal Design Power

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this context the

Supercomputing Research Infrastructure would host the Tier-0 systems; national

or topical HPC centres would constitute Tier-1

TPC Transaction Processing Performance Council

TRL Technology Readiness Levels

UDF User Defined Function

UEABS Unified European Applications Benchmark Suite

YCSB Yahoo! Cloud Serving Benchmark

## **List of Project Partner Acronyms**

BADW-LRZ Leibniz-Rechenzentrum der Bayerischen Akademie der Wissenschaften,

Germany (3<sup>rd</sup> Party to GCS)

BILKENT Bilkent University, Turkey (3<sup>rd</sup> Party to UYBHM)

BSC Barcelona Supercomputing Center - Centro Nacional de

Supercomputacion, Spain

CaSToRC Computation-based Science and Technology Research Center, Cyprus CCSAS Computing Centre of the Slovak Academy of Sciences, Slovakia

CEA Commissariat à l'Energie Atomique et aux Energies Alternatives, France

(3 <sup>rd</sup> Party to GENCI)

CESGA Fundación Publica Gallega Centro Tecnológico de Supercomputación de

Galicia, Spain, (3<sup>rd</sup> Party to BSC)

CINECA CINECA Consorzio Interuniversitario, Italy

CINES Centre Informatique National de l'Enseignement Supérieur, France (3 rd

Party to GENCI)

CNRS Centre National de la Recherche Scientifique, France (3 rd Party to

GENCI)

CSIC Spanish Council for Scientific Research (3<sup>rd</sup> Party to BSC)

CYFRONET Academic Computing Centre CYFRONET AGH, Poland (3rd party to

PNSC)

EPCC at The University of Edinburgh, UK

ETHZurich (CSCS) Eidgenössische Technische Hochschule Zürich – CSCS, Switzerland FIS FACULTY OF INFORMATION STUDIES, Slovenia (3<sup>rd</sup> Party to

ULFME)

GCS Gauss Centre for Supercomputing e.V.

GENCI Grand Equipment National de Calcul Intensiv, France GRNET Greek Research and Technology Network, Greece

INRIA Institut National de Recherche en Informatique et Automatique, France

(3<sup>rd</sup> Party to GENCI)

IST Instituto Superior Técnico, Portugal (3<sup>rd</sup> Party to UC-LCA) IUCC INTER UNIVERSITY COMPUTATION CENTRE, Israel

JKU Institut fuer Graphische und Parallele Datenverarbeitung der Johannes

Kepler Universitaet Linz, Austria

JUELICH Forschungszentrum Juelich GmbH, Germany

KTH Royal Institute of Technology, Sweden (3<sup>rd</sup> Party to SNIC)

LiU Linkoping University, Sweden (3<sup>rd</sup> Party to SNIC)

NCSA NATIONAL CENTRE FOR SUPERCOMPUTING APPLICATIONS.

Bulgaria

NIIF National Information Infrastructure Development Institute, Hungary NTNU The Norwegian University of Science and Technology, Norway (3<sup>rd</sup> Party

to SIGMA)

NUI-Galway National University of Ireland Galway, Ireland

PRACE Partnership for Advanced Computing in Europe aisbl, Belgium PSNC Poznan Supercomputing and Networking Center, Poland

RISCSW RISC Software GmbH

#### D5.6 Extended best practice guide for prototypes and demonstrators

RZG Max Planck Gesellschaft zur Förderung der Wissenschaften e.V.,

Germany (3<sup>rd</sup> Party to GCS)

SIGMA2 UNINETT Sigma2 AS, Norway

SNIC Swedish National Infrastructure for Computing (within the Swedish

Science Council), Sweden

STFC Science and Technology Facilities Council, UK (3<sup>rd</sup> Party to EPSRC)

SURFsara Dutch national high-performance computing and e-Science support

center, part of the SURF cooperative, Netherlands

UC-LCA Universidade de Coimbra, Labotatório de Computação Avançada, Portugal

UCPH Københavns Universitet, Denmark

UHEM Istanbul Technical University, Ayazaga Campus, Turkey

UiO University of Oslo, Norway (3<sup>rd</sup> Party to SIGMA)

ULFME UNIVERZA V LJUBLJANI, Slovenia

UmU Umea University, Sweden (3<sup>rd</sup> Party to SNIC)

Universidade de Évora, Portugal (3rd Party to UC-LCA)

UPC

Universitat Politècnica de Catalunya, Spain (3<sup>rd</sup> Party to BSC)

UPM/CeSViMa Madrid Supercomputing and Visualization Center, Spain (3<sup>rd</sup> Party to

BSC)

USTUTT-HLRS Universitaet Stuttgart – HLRS, Germany (3rd Party to GCS)

VSB-TUO VYSOKA SKOLA BANSKA - TECHNICKA UNIVERZITA

OSTRAVA. Czech Republic

WCNS Politechnika Wrocławska, Poland (3rd party to PNSC)

# **Executive Summary**

Prototyping is an integral part of the HPC design process that assists in detecting and resolving any issues related to the use of new concepts and technologies. In general, the prototyping of HPC systems has the following objectives:

- to test and refine the functionality of a given HPC design and enable a better understanding of its purpose;

- to save time and costs by empowering the possibility of early influencing design changes;

- to assess the usefulness and applicability of new technologies and design approaches; and last but foremost

- to address the requirements of current user communities of HPC centres in an efficient way by gaining inputs and insights regarding the usage of the production system.

This best practice guide aims to deliver information and guidance useful for the evaluation of prototype HPC systems with regard to their usability and fit for purpose. For achieving this goal, this document extends the previously developed (by PRACE-4IP WP5) best practice guide to include guidelines on: (i) a set of benchmarks most suitable for HPC prototyping; and (ii) a set of system and development tools that are currently used by PRACE Tier-0/Tier-1 sites for HPC prototype evaluation, while reflecting on existing co-design opportunities.

The guide's intended audience is prototype and/or demonstrator owners for testing on actual HPC prototypes and demonstrators stemming from EU-funded projects such as MontBlanc, DEEP/DEEP-ER/DEEP-EST, or future Pre-Commercial Procurements (PCP) on HPC. It could also prove useful for FET-HPC technological projects, and also for communities represented within Centers of Excellence (CoEs), providing both groups with some best practice for the assessment of prototypes and demonstrators, useful for the system design as well as for early and customized tests of system usability by thematic communities.

This best practice guide has been designed taking into account the current race to Exascale, with the goal of providing valuable input for the activity of the EuroHPC Joint Undertaking<sup>1</sup>.

-

<sup>&</sup>lt;sup>1</sup> EuroHPC Joint Undertaking: <a href="https://eurohpc-ju.europa.eu/">https://eurohpc-ju.europa.eu/</a>

#### 1 Introduction

The design of a High Performance Computing (HPC) system is a complex task that needs to meet various contrasting demands ranging from: (i) the divergent requirements of user communities and system performance targets; over (ii) data centre's power delivery, cooling, and floor-space constraints; to (iii) capital and operational expenses. Additionally, as these high-end systems scale to support the ever-increasing performance demand, the underlying components become more complex and diverse, making the performance of target HPC systems strongly dependent on the choice of certain hardware (HW) and software (SW) technology and their corresponding configuration. All these demands further increase the importance of HW/SW co-design activities and make the efficient procedures for HPC planning, commissioning, and evaluation even more complex.

This document aims to provide a guide for HPC prototype/demonstrator owners that assists with the evaluation of these systems with regard to their usability and fit for purpose by building on:

- a) previously identified requirements of new user communities for the use of next generation HPC systems [1]; and

- b) experiences of PRACE [2] Tier-0/Tier-1 sites gathered during various EU-funded projects related to HPC prototyping [3].

More specifically, the document extends the previous PRACE-4IP [4] WP5 efforts that provided an overview on: (*i*) the individual phases of HPC prototyping projects; and (*ii*) prototyping experiences of PRACE Tier-0/Tier-1 sites that stemmed from previous PRACE and other FP7 and H2020 projects [3]<sup>2</sup> to include tools encompassing:

- a) a checklist for system and development tools that should be installed on a system before it is made available to general HPC users;

- b) sets of benchmarks; and

- c) Key Performance Indicators (KPIs)

for the productive evaluation of HPC prototyping activities.

The rest of this document is organised as follows. Section 2 lists the PRACE Tier-0 and Tier-1 HPC sites that completed the survey, developed by PRACE-5IP WP5 [1], on which some of the analysis of this deliverable is based on and Section 3 describes the co-design opportunities. Section 4 outlines the minimal requirements (as identified from PRACE Tier-0/Tier-1 sites) in terms of libraries, tools, etc. that should be installed on a system before it is accessed by general HPC users. Section 5 presents a set of benchmarks, including a representative set of synthetic open source kernel benchmarks, with a different set of properties that is used by PRACE Tier-0 and Tier-1 sites to evaluate newly deployed prototype systems. This set of benchmarks was prepared in cooperation with PRACE-5IP WP7, the application-focused work package, which is among other activities in charge of code enabling activities, publication of Best Practice Guides, and the development of the Unified European Applications Benchmark Suite (UEABS). Section 6 describes the main Key Performance Indicators (KPIs) that are most commonly used by PRACE HPC sites for prototype

<sup>&</sup>lt;sup>2</sup> For example PRACE-PP [5], PRACE-1IP [6], PRACE-2IP [7], PRACE-3IP [8], Mont-Blanc [9], DEEP/DEEP-ER [10], and QPACE [11] projects.

evaluation. Finally, Section 7 provides an outlook, delineates future work, and concludes this report.

The survey as well as the raw data from which the results presented here were obtained have been uploaded to the PRACE repository and can be accessed via <a href="https://repository.prace-ri.eu/git/hayk.shoukourian/5IPT3.git">https://repository.prace-ri.eu/git/hayk.shoukourian/5IPT3.git</a> (access restricted to PRACE-IP partners).

## 2 Survey

Some of the analysis presented in this document is based on the results of an online survey that was prepared during PRACE-5IP by WP5 contributors and distributed among PRACE Tier-0 and Tier-1 supercomputing sites [1]. The survey was conducted during the timeframe of October to December 2017.

The following PRACE Tier-0/Tier-1 sites participated in the survey:

| PRACE Tier-0/Tier-1 site                                                                             | Name of the flagship system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Country |  |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| CINECA [12]                                                                                          | MARCONI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Italy   |  |

| Computation-based Science and Technology Research Center CaSToRC), The Cyprus Institute [13]  Cyprus |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cyprus  |  |

| CSC - IT Center for Science Ltd. [14] Sisu Finla                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Finland |  |

| Leibniz Supercomputing Centre of the Bavarian Academy of Sciences (BAdW-LRZ) [15]                    | To the second se |         |  |

| Greek Research and Technology Network (GRNET) [16]                                                   | rch and Technology Network (GRNET) [16] ARIS Greece                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |  |

| University of Debrecen [17]                                                                          | VGGD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Hungary |  |

| Poznan Supercomputing and Networking Center (PSNC) [18]                                              | 18] Eagle / Hetman Poland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |  |

| Gdansk University of Technology [19] Tryton                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Poland  |  |

| The Hartree Centre [20]                                                                              | Scafell Pike                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UK      |  |

Table 1: List of PRACE Tier-0/Tier-1 sites that participated in the survey.

Most of these HPC sites were involved in the previously mentioned PRACE prototyping projects, deploy prototype systems on a regular basis, and thus bring in significant expertise in terms of HPC prototyping [1, 3, 21].

# 3 Co-design opportunities

With the ever-increasing demand for performance, power consumption continues to remain an important design constraint for future HPC systems. Currently vendors are including all the more vertical or special purpose components (e.g. accelerators, tensor cores, neuromorphic chips, FPGAs, etc.), each designed to maximize the performance of a specific set of workloads. This leads to a richer design space to explore, with multiple opportunities for co-design activities in the near future. A notable addition most relevant to this deliverable is the European Processor Initiative (EPI) [22], with the stated goal to co-design and bring to market a processor to power future

Exascale systems based on European technologies. It is noteworthy that the EPI intends to solicit feedback from EU HPC applications and ecosystems as part of its co-design process.

In what follows, the document briefly reflects on co-design opportunities identified during PRACE-5IP, grouped according to the architectural component the co-design opportunity is most relevant to.

#### 3.1 Co-design at the chip level

Traditionally, there have not been many opportunities for co-design at CPU chip level, with the HPC market and related use cases having limited influence in the design choices of these components. The aforementioned EU initiative for the design and production of European CPUs and Accelerators, suitable for next generation Exascale systems, should provide for more opportunities, as it explicitly states that these technologies will be developed within a co-design process. Examples of features that would be open for co-design within this initiative include: (i) the optimal vector unit size, namely in terms of the optimal length, in bits, suitable for the range of targeted EU scientific applications; (ii) a heterogeneous design that will include different cores, each dedicated for a given kind of workload (e.g. AI, Big Data, etc.), as well as (iii) communication methods and technologies for CPU and accelerator, with options being PCIe, NVlink, OpenCAPI, GenZ, etc. One particular design choice with implications on power consumption is the numerical precision of floating point and integer operations. It will therefore be important to provide feedback on the level of support of numerical precision required on such chips, which depends on whether applications can tolerate accuracies different from double precision floating point, i.e. 64bit IEEE.

#### 3.2 Co-design at the integration level

At the integration level, there are much more opportunities for co-design compared to chip design, and this is exemplified by the eagerness of vendors to solicit feedback which helps them plan future products. European Exascale projects such as DEEP and Mont Blanc are also examples of co-designed HPC systems, with the co-design starting at the integration level. At the time of writing of this report, we can identify the two most characteristic elements of the architecture that are relevant for co-design at the integration level, namely High Bandwidth Memory (HBM) and Non Volatile Memory (NVM). The design choices available are the amount of HBM to be added to the CPU, on one side, and the available system bandwidth for NVM on the other side. These are both design choices that must be defined during the HPC node design stage. Besides HW, together with the node populated with different kinds of memory, an important co-design activity could be the evaluation of different memory models dealing with memory hierarchies (e.g. transparent or explicit memory usage).

#### 3.3 Co-design for networking

Networking of an HPC system has traditionally been a component amenable to optimization and therefore co-design. This is largely thanks to the multiple protocols, vendors, and topologies available to integrators to choose from when designing an HPC system. Beyond these design choices, we have identified two emerging trends that could broaden the design space available for

this component. Namely, there are lately important movements towards better support for low latency network protocols that in turn allow for more efficient implementations of partitioned global address space (PGAS) programming models. Complementary to these developments is the inclusion of active network components, for example FPGA co-processors which implement the network interface, that allow for performing basic computations while the messages are being communicated. In terms of PGAS and future MPI standards, there are opportunities in co-designing functionalities that will facilitate applications to scale on multi-core heterogeneous system, where communication could take place e.g. between two accelerators or other similar devices. For active networks, co-design and feedback from application scientists are necessary for defining which functionalities to implement during message passing.

#### 3.4 Co-design for energy management

Energy management, combined with energy monitoring and profiling, is becoming all the more an important topic in the design and running of HPC infrastructures. Co-design initiatives during the past decades, mostly through the PRACE prototype projects and PRACE PCP projects, have given Europe a competitive advantage in this regard when compared to international efforts. As new CPU and GPU architectures are being introduced, and with the forthcoming European processor being planned, there is an opportunity to leverage the work that has been done in the past years to codesign architectures compliant with the tools and middleware developed within Europe, such that leadership on energy management tools is maintained. One important issue would be to develop a standard for collecting and storing raw data, so that the access to the data will be kept open irrespective of the specific tools for monitoring and managing energy consumption.

#### 3.5 Co-design for libraries

We see opportunities for co-design of libraries at two levels: (i) at the level of the interface of the library with the scientific application code; and (ii) at the level of the underlying hardware for which the library is optimized for. The former is important as the performance of application codes becomes more sensitive to the underlying math, I/O, and domain specific libraries. With this respect, engaging the developers of the libraries would be beneficial in designing their API to better support European applications. Actions within PRACE activities and European Centers of Excellence (CoEs) are already along these lines, which can be leveraged to start specific co-design actions, targeting the exploitation of new chips and system architectures. As regards co-designing the libraries for the underlying hardware, it will be important to have libraries able to exploit new instruction sets, such as for reduced precision arithmetic used in AI applications. Furthermore, HDF5 is gaining considerable attention from applications developers due to its performance and reliability characteristics for parallel I/O. It can be an additional opportunity for co-designing new I/O subsystems to better support HDF5, something which is already being included in co-design actions for Exascale in the US.

#### 3.6 Co-design for compiler/programming standards

Among the wide range of programing models that target parallel processing and HPC, OpenMP appears to be the one which on one hand maintains broad support from both users and vendors and on the other hand continues to evolve introducing new features, such as support for accelerators. In particular, it is expected that the version 5.0 of the OpenMP standard and beyond will play an important role in exploiting future exascale architectures, providing many opportunities to engage with the community working in defining the OpenMP standard to better support the needs of the European applications and architectures. This is especially true regarding co-design actions related to new memory management and off-loading features already defined in the standard but which remain poorly supported by systems software, drivers, and compilers.

#### 3.7 Co-design for data management/processing

As the availability of data increases, the need to manage and process it also grows, leading to the so-called convergence of HPC and HPDA (High Performance Data Analysis), both in terms of applications and infrastructure. At the European level, applications dealing with the convergence of large data analysis and HPC are being targeted by Centers of Excellence. At the infrastructure level, there are a large number of co-design initiatives, including the use of accelerators to speed-up data processing, the use of object store technologies as an alternative to POSIX filesystems, and different organization of storage tiers to reduce latency in accessing large datasets (e.g. usage of flash based devices with burst buffer like software technology).

#### 3.8 Co-design for specific HPC workloads

Finally, at the HPC system level, co-design opportunities arise in tuning for a specific scientific workload (e.g. for AI applications), while at the same time similar opportunities arise in refactoring or adapting applications to best match the possibilities offered by new hardware. Examples include new algorithms that exploit mixed precision arithmetic, thus maximizing the performance and energy efficiency on certain types of HPC architectures. Indeed, many iterative algorithms may be refactored to perform most iterations at low precision, with just a few iterations required at full double precision, without an overall loss of accuracy. In this example, a co-designed HPC system would employ components that more optimally perform reduced-precision arithmetic, such as GPUs. Other examples include workloads that may require a preprocessing of data, such as a convolution or Fourier transform of data, before proceeding to the main calculations. Such workloads could benefit from a co-designed system that would include FPGAs to carry out the preprocessing step.

# 4 Checklist of system and development tools

In this section, we present the results of a survey in which we asked PRACE Tier-0 and Tier-1 sites to identify which system and development tools they consider most crucial to deploy on their prototypes. This provides us with a minimum list of system and development tools, the functionality of which should be somehow enabled on the prototype to allow for easier introduction

in a production environment and maintain aspects of compatibility with more familiar production systems. It should be noted that building a prototype may serve different purposes, therefore the list should be treated as a list of aspects that should be considered rather than a strict list of requirements.

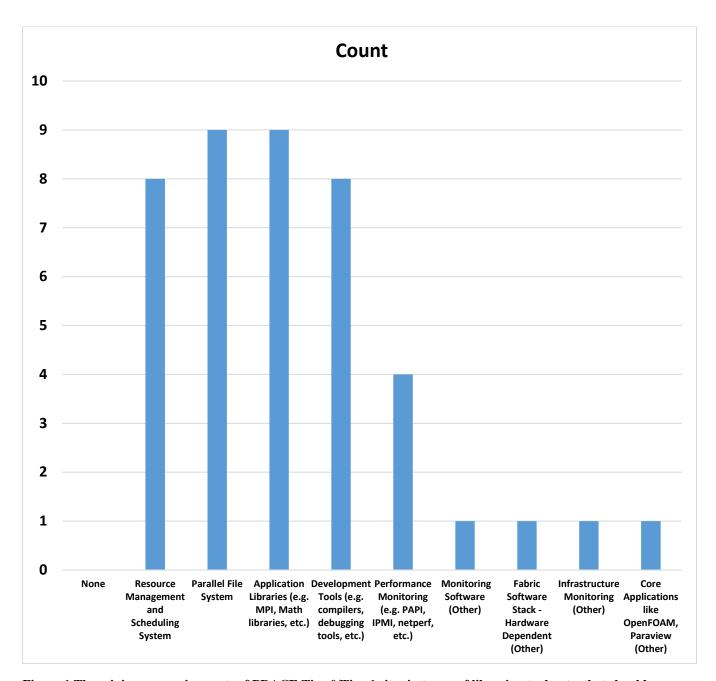

In Figure 1, we show the survey responses for each category of system and development tools. As mentioned earlier in Section 2, the survey results are based on nine responses obtained from PRACE Tier-0 and Tier-1 HPC sites. The general conclusion that can be drawn is that development tools, parallel libraries, and job schedulers are considered by PRACE Tier-0 and Tier-1 sites as the most necessary tools to deploy on a prototype, while production application codes and special-purpose monitoring tools are not considered as crucial.

Figure 1 The minimum requirements of PRACE Tier-0/Tier-1 sites in terms of libraries, tools, etc. that should be installed on a system before it gets accessed by general HPC users

#### 4.1 Resource management and scheduling system

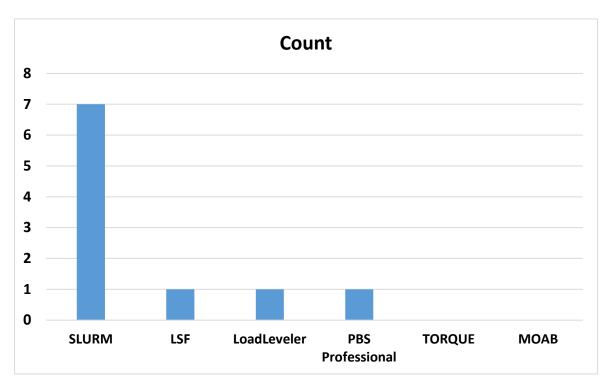

The queuing system is a necessary tool whenever several users intent to access the same prototype. Amongst queuing systems, most respondents deploy SLURM on their prototypes, as shown in Figure 2. It is noteworthy that even in prototyping scenarios, co-design opportunities are tested with multiple teams having access to the same experimental environment, which indicates a certain level of maturity in the users as well as the tools that are able to accommodate novel technologies. It should also be noted that the basic functionality of all queuing systems is similar and that the required effort to migrate submission scripts from production systems seems to be less of an issue.

This would suggest that ease of deployment and use should be more significant criteria when deploying a queuing system on a prototype.

Figure 2 Resource management and scheduling systems currently used at PRACE Tier-0/Tier-1 sites

#### 4.2 Parallel filesystem

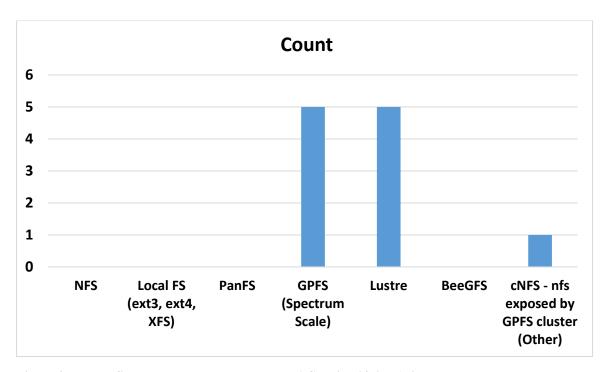

As indicated in Figure 1, the vast majority of centres surveyed identified the availability of a parallel filesystem on their prototypes as a necessary component of the prototyping activity. This is despite recent developments and more common usage of object storage. As seen in Figure 3, all solutions used in prototyping by the Tier-0 and Tier-1 PRACE sites surveyed currently deliver POSIX compliant file systems, with the majority split between GPFS and Lustre.

Figure 3 Parallel file system currently used at PRACE Tier-0/Tier-1 sites

#### 4.3 Application libraries

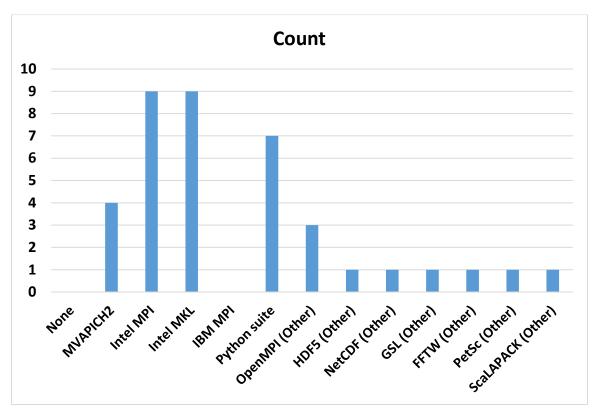

The performance of an HPC system eventually depends on how efficiently it executes applications, and these, in turn, rely heavily on the availability of a certain set of identifiable HPC libraries. All surveyed centres identified the availability of such software as a determining factor in the usability of the prototype (see Figure 1). Before designing a prototype, it is, therefore necessary to check which libraries are needed and which are available for the system being designed. As the survey results shown in Figure 4 suggest, the most important aspect is the availability of an efficient MPI implementation, since this library is employed by all non-trivially parallelized HPC applications. Naturally, some currently identified software may not be directly available on a prototype system; for example Intel MPI or MKL identified in Figure 4 will not be available on an ARM prototype. But the survey result indicates that the availability of an efficient alternative will be crucial in the evaluation of the prototype. An additional, rather non-expected response, was the popularity of the requirement of a Python stack, which exceeds the responses for an OpenMP implementation.

Figure 4 The minimum requirements of PRACE Tier-0/Tier-1 sites in terms of application libraries (e.g. MPI, Math libraries, etc.) that should be installed on a system before it gets accessed by general HPC users

#### 4.4 Development tools

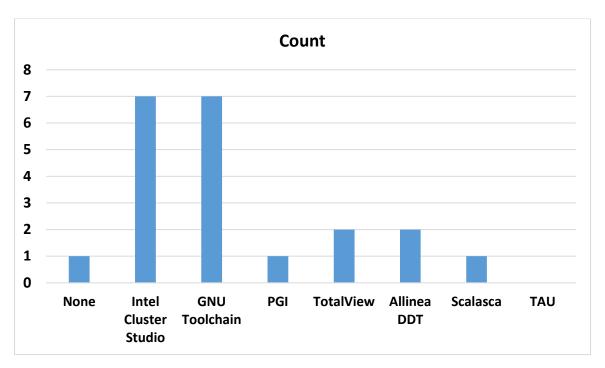

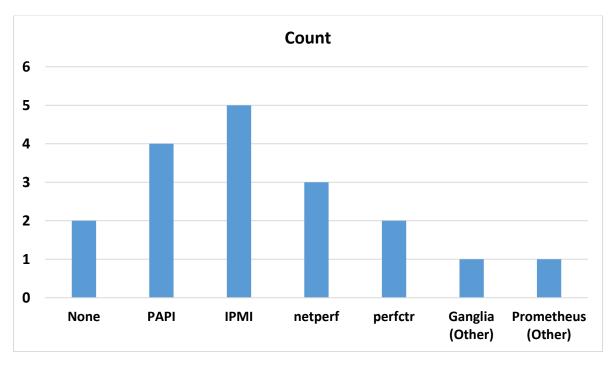

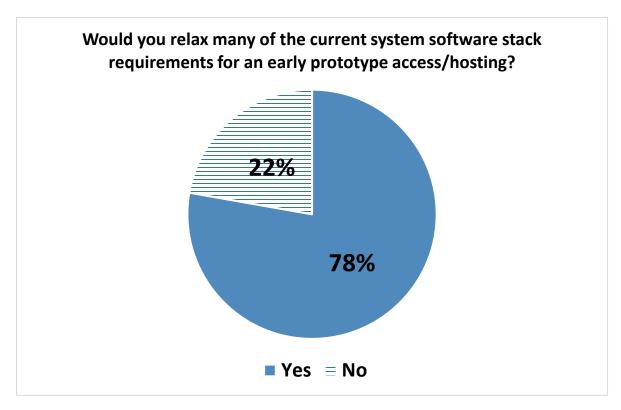

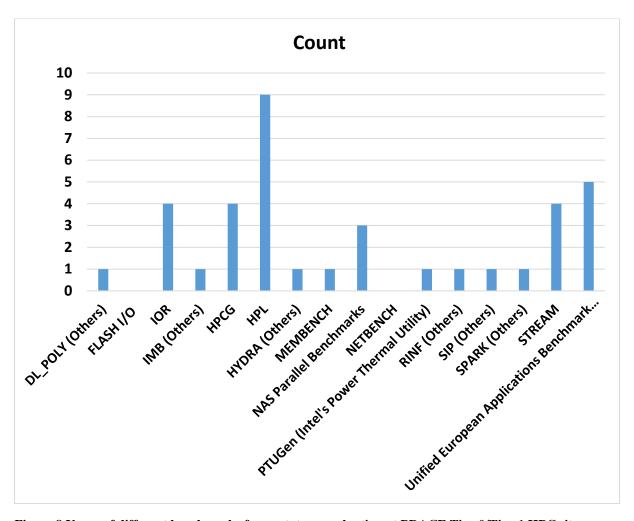

Many HPC software packages come either in the form of source code or are directly developed by local user communities. In either case, the availability of optimized compilers and debugging tools are crucial for a prototype since these determine the possibility of performing comparative checks with existing solutions. The dominant position of x86 platforms in HPC is exemplified by the strong requirement on the availability of Intel Cluster Studio, shown in Figure 5. In many cases, such as other CPU architectures or accelerator solutions, this response should be interpreted as a requirement for an optimized and mature compiler stack for the prototype. This conclusion is supported by the responses to the requirement of a GNU toolchain, also shown in Figure 5.