# E-Infrastructures H2020-EINFRA-2016-2017

# EINFRA-11-2016: Support to the next implementation phase of Pan-European High Performance Computing Infrastructure and Services (PRACE)

### PRACE-5IP

# **PRACE Fifth Implementation Phase Project**

**Grant Agreement Number: EINFRA-730913**

**D5.2**

Market and Technology Watch Report Year 2

Final

Version: 1.01

Author(s): Aris SOTIROPOULOS (GRNET)

Date: 21.03.2019

## **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №:           | EINFRA-730913                            |

|---------------|---------------------------|------------------------------------------|

|               | <b>Project Title:</b>     | PRACE Fifth Implementation Phase Project |

|               | <b>Project Web Site:</b>  | http://www.prace-ri.eu                   |

|               | Deliverable ID:           | D5.2                                     |

|               | <b>Deliverable Nature</b> | e: Report                                |

|               | <b>Dissemination Leve</b> | el: Contractual Date of Delivery:        |

|               | PU*                       | 31 / March / 2019                        |

|               |                           | Actual Date of Delivery:                 |

|               |                           | 29 / March / 2019                        |

|               | <b>EC Project Officer</b> | : Leonardo Flores Añover                 |

<sup>\* -</sup> The dissemination levels are indicated as follows: **PU** – Public, **CO** – Confidential, only for members of the consortium (including the Commission Services) **CL** – Classified, as referred to in Commission Decision 2005/444/EC.

## **Document Control Sheet**

|            | Title:                | Market an | nd Technology Watch Report Year 2 |

|------------|-----------------------|-----------|-----------------------------------|

| Document   | ID:                   | D5.2      |                                   |

|            | Version:              | 1.01      | Status: Final                     |

|            | Available at:         | http://ww | w.prace-ri.eu                     |

|            | <b>Software Tool:</b> | Microsof  | t Word (Windows and Mac)          |

|            | File(s):              | D5.2.doc  | x                                 |

|            | Written by:           |           | Aris SOTIROPOULOS (GRNET)         |

| Authorship | <b>Contributors:</b>  |           | Adem Tekin (UHEM)                 |

|            |                       |           | Ahmet Tuncer Durak (UHEM)         |

|            |                       |           | Andreas Johansson (LiU)           |

|            |                       |           | Aris Sotiropoulos (GRNET)         |

|            |                       |           | Dirk Pleiter (FZJ)                |

|            |                       |           | Eric Boyer (CINES)                |

|            |                       |           | Filip Stanek (IT4I)               |

|            |                       |           | François Robin (CEA)              |

|            |                       |           | Gert Svensson (KTH)               |

|            |                       |           | Guillaume Colin de Verdière (CEA) |

|            |                       |           | Jean-Philippe Nomine (CEA)        |

|            |                       |           | K.Wadówka (PSNC)                  |

|            |                       |           | Kalle Happonen (CSC)              |

|            |                       |           | Marcel Bruckner (BSC)             |

|            |                       |           | Mateusz Tykierko (WCSS)           |

|            |                       |           | Michael Stephan (FZJ)             |

|            |                       |           | Mirko Cestari (CINECA)            |

|            |                       |           | Norbert Meyer (PSNC)              |

|            |                       |           | Panayiotis Tsanakas (GRNET)       |

|            |                       |           | Pawel Woszuk (PSNC)               |

|            |                       |           | Philippe Segers (GENCI)           |

|            |                       |           | Samuli Saarinen (CSC)             |

|            |                       |           | Stephane Requena (GENCI)          |

|            |                       |           | Susanna Salminen (CSC)            |

|            | Reviewed by:          |           | Walter Lioen (SURFsara)           |

|            |                       |           | Thomas Eickermann (FZJ)           |

|            | Approved by:          |           | MB/TB                             |

## **Document Status Sheet**

| Version | Date             | Status    | Comments                                                            |

|---------|------------------|-----------|---------------------------------------------------------------------|

| 0.01    | 09/January/2019  | Draft     | Aris Sotiropoulos (GRNET) – Initial version, TOC, Chapter Leaders,  |

|         |                  |           | Contributors                                                        |

| 0.02    | 10/January/2019  | Draft     | Adem Tekin (UHEM), Ahmet Tuncer Durak (UHEM) – Chapter 2.1          |

| 0.03    | 15/January/2019  | Draft     | Guillaume Colin de Verdière (CEA) – Chapters 7.1 and 7.2            |

| 0.04    | 16/January/2019  | Draft     | Mirko Cestari (CINECA) – Ch 3.9 PPI4HPC                             |

| 0.05    | 17/January/2019  | Draft     | Aris Sotiropoulos (GRNET), Panayiotis Tsanakas (GRNET) – Ch.        |

|         |                  |           | 2.3 Business analysis                                               |

| 0.06    | 18/January/2019  | Draft     | Andreas Johansson (LiU) – Ch 5.2 Off-line storage                   |

| 0.07    | 20/January/2019  | Draft     | Mateusz Tykierko (WCSS) – Ch 2.5 Consolidation in HPC market        |

| 0.08    | 21/January/2019  | Draft     | Dirk Pleiter (FZJ) – Ch 4.1 Processors, Ch 6.2 IBM, Fujitsu         |

| 0.09    | 21/January/2019  | Draft     | Susanna Salminen (CSC) – Ch 6.3 Cray                                |

| 0.10    | 22/January/2019  | Draft     | Eric Boyer (CINES) – Chapter 2.2 Exascale Initiatives               |

| 0.11    | 22/January/2019  | Draft     | Dirk Pleiter (FZJ) – Ch 7.3 Neuromorphic computing                  |

| 0.12    | 22/January/2019  | Draft     | Jean-Philippe NOMINE (CEA), Mirko CESTARI (CINECA),                 |

|         |                  |           | François ROBIN (CEA), Dirk PLEITER (FZJ), Philippe SEGERS           |

|         |                  |           | (GENCI) – Ch 3 EU HPC Landscape and Technology Update               |

| 0.13    | 23/January/2019  | Draft     | Marcel Bruckner (BSC) – Ch 4.2.1 GPU                                |

| 0.14    | 24/January/2019  | Draft     | Michael Stephan (FZJ) – Ch 6.6 Lenovo                               |

| 0.15    | 24/January/2019  | Draft     | Mateusz Tykierko (WCSS) – References for Ch 2.5                     |

| 0.16    | 24/January/2019  | Draft     | Marcel Bruckner (BSC) – Ch 4.4 Interconnect                         |

| 0.17    | 25/January/2019  | Draft     | Filip Stanek (IT4I) – Ch. 4.3 Memory Technologies, Ch. 4.4          |

|         |                  |           | Interconnects                                                       |

| 0.18    | 25/January/2019  | Draft     | Andreas Johansson (LiU) – Ch 5.1 Storage Solutions                  |

| 0.19    | 28/January/2019  | Draft     | Mirko Cestari (CINECA) – Ch 4.1.1 x86_64 processors                 |

| 0.20    | 29/January/2019  | Draft     | Andreas Johansson (LiU) – Ch 5.1 Storage Solutions++                |

| 0.21    | 13/February/2019 | Draft     | François Robin (CEA) – Various changes                              |

| 0.22    | 17/February/2019 | Draft     | Filip Stanek (IT4I) – Ch. 4.4 Interconnects, Ch. 6.1 HPE            |

| 0.23    | 18/February/2019 | Draft     | Mirko Cestari (CINECA) – Ch 1 Introduction                          |

| 0.24    | 18/February/2019 | Draft     | Samuli Saarinen (CSC) – Ch 6.5 Atos                                 |

| 0.25    | 18/February/2019 | Draft     | Norbert Meyer, K.Wadówka, Pawel Woszuk (PSNC), Marcel               |

|         |                  |           | Bruckner (BSC) – Ch 5 Data Storage and Data Management              |

| 0.26    | 19/February/2019 | Draft     | Samuli Saarinen (CSC) – Ch 2.4 Cloud computing in HPC               |

| 0.27    | 27/February/2019 | Draft     | Aris Sotiropoulos (GRNET) – Ch 6.4 NEC, Acronyms and                |

|         |                  |           | Abbreviations                                                       |

| 0.28    | 28/February/2019 | Intra-WP5 | François Robin (CEA) – Executive Summary and Conclusion             |

| 0.00    |                  | review    |                                                                     |

| 0.29    | 28/February/2019 | WP5 rev   | François Robin (CEA) – Corrections/comments                         |

| 0.30    | 1/March/2019     | WP5 rev   | Philippe Segers (GENCI) – Contribution to Executive Summary and     |

| 0.01    | 1.2.5 1.4.2.1.2  |           | Conclusion, populating keywords section                             |

| 0.31    | 1/March/2019     | WP5 rev   | Gert Svensson (KTH) – Multiple corrections                          |

| 0.32    | 4/March/2019     | WP5 rev   | Dirk Pleiter (FZJ) – Ch 4.1.2 ARM processors additions/corrections  |

| 0.33    | 5/March/2019     | WP5 rev   | Adem Tekin (UHEM), Ahmet Tuncer Durak (UHEM) – Ch 2.1               |

| 0.24    | 5/M 1 /2010      | WDC       | corrections                                                         |

| 0.34    | 5/March/2019     | WP5 rev   | Gert Svensson (KTH) – Multiple corrections, Susanna Salminen        |

| 0.25    | C/M1./2010       | WDs       | (CSC) – Corrections                                                 |

| 0.35    | 6/March/2019     | WP5 rev   | Gert Svensson (KTH) – Corrections, Dirk Pleiter (FZJ) – Corrections |

| 0.36    | 6/March/2019     | WP5 rev   | Eric Boyer (CINES) – Chapter 2.2 review and add-ons                 |

| 0.37    | 7/March/2019     | PRACE r   | Aris Sotiropoulos (GRNET) – prepare for PRACE internal review       |

| 0.40 | 15/March/2019 | PRACE r | Aris Sotiropoulos (GRNET) – initial corrections after comments from PRACE reviewers (Walter Lioen (SURFsara), Thomas Eickermann (FZJ))                                                                                   |

|------|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.41 | 19/March/2019 | PRACE r | Mateusz Tykierko (WCSS), Filip Stanek (IT4I), Susanna Salminen (CSC), Dirk Pleiter (FZJ), Mirko Cestari (CINECA), Adem Tekin (UHEM), Eric Boyer (CINES), Stephane Requena (GENCI) – addressing PRACE reviewers' comments |

| 0.42 | 21/March/2019 | PRACE r | Marcel Bruckner (BSC), Kalle Happonen (CSC) – addressing PRACE reviewers' comments                                                                                                                                       |

| 0.43 | 21/March/2019 | PRACE r | François Robin (CEA) – important amendments by WP Leader                                                                                                                                                                 |

| 1.00 | 21/March/2019 | Final   | Aris Sotiropoulos (GRNET) – finalize for TB/MB approval                                                                                                                                                                  |

# **Document Keywords**

| Keywords: | HPC, Top500, Exascale, Strategy, Market watch, Technology watch     |

|-----------|---------------------------------------------------------------------|

|           | Business analysis, Cloud computing in HPC, EuroHPC, PRACE,          |

|           | ETP4HPC, BDVA, FETHPC, EPI, PPI4HPC, HBP, FENIX, ICEI,              |

|           | Intel, AMD, ARM, POWER processors, FPGA, GPU, NVIDIA,               |

|           | Memory technologies, Interconnect, Data Storage, Data Management,   |

|           | IBM, Spectra Logic, Oracle StorageTek, Quantum tape, Data services, |

|           | DDN, Seagate, HPE, Fujitsu, Huawei, Cray, NEC, ATOS-BULL,           |

|           | Lenovo, AI, Heterogeneous technologies, Neuromorphic computing      |

#### **Disclaimer**

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° EINFRA-730913. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2019 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract EINFRA-730913 for reviewing and dissemination purposes. All trademarks and other rights on third party products mentioned in this document are acknowledged as owned by the respective holders.

## **Table of Contents**

| Do  | cument C    | ontrol Sheet                          | 11   |

|-----|-------------|---------------------------------------|------|

| Do  | cument St   | tatus Sheet                           | iii  |

| Do  | cument K    | eywords                               | v    |

| Lis | st of Figur | es                                    | xii  |

| Lis | st of Table | S                                     | xiii |

| Re  | ferences a  | nd Applicable Documents               | xiv  |

| Lis | st of Acroi | nyms and Abbreviations                | xxi  |

| Lis | st of Proje | ct Partner Acronyms                   | xxiv |

| Ex  | ecutive Su  | ımmary                                | 1    |

| 1   |             | ction                                 |      |

| 2   | Worldw      | ide HPC landscape and Market overview | 5    |

| 2   | 2.1 Qui     | ck update of HPC worldwide            | 5    |

|     | 2.1.1       | Countries                             | 5    |

|     | 2.1.2       | Accelerators                          | 13   |

|     | 2.1.3       | Age                                   | 14   |

|     | 2.1.4       | Vendors                               | 15   |

|     | 2.1.5       | Computing efficiency                  | 18   |

|     |             | Energy efficiency                     |      |

|     |             | Architectures                         |      |

| 2   | 2.2 Upd     | ate on Exascale initiatives           | 24   |

|     | 2.2.1       | Exascale plans: China                 |      |

|     | 2.2.1.1     | SUGON                                 | 25   |

|     | 2.2.1.2     |                                       |      |

|     | 2.2.1.3     |                                       |      |

|     | 2.2.2       | Exascale plans: Japan                 |      |

|     |             | Exascale plans: USA                   |      |

|     |             | Exascale plans: Europe                |      |

| 2   |             | iness analysis                        |      |

| 2   |             | ad computing in HPC                   |      |

|     | 2.4.1       | Trends                                |      |

|     | 2.4.1.1     |                                       |      |

|     | 2.4.1.2     | GPUs and FPGAs                        | 33   |

|   | 2.4.1.3    | Quantum computing                                      | 34 |

|---|------------|--------------------------------------------------------|----|

|   | 2.4.1.4    | Custom and heterogeneous hardware                      | 34 |

|   | 2.4.2 Et   | ıropean Open Science Cloud                             | 34 |

|   | 2.5 Conso  | lidation in the HPC market                             | 35 |

| 3 | EU HPC L   | andscape and Technology Update                         | 36 |

|   | 3.1 EU lai | ndscape overview                                       | 36 |

|   | 3.1.1 Et   | roHPC                                                  | 36 |

|   | 3.1.2 Pi   | RACE                                                   | 36 |

|   | 3.1.3 E    | TP4HPC, the HPC cPPP, and BDVA                         | 37 |

|   | 3.1.4 Co   | oordination and Support Actions                        | 38 |

|   | 3.2 Applie | cations: Centres of Excellence                         | 38 |

|   | 3.3.1 FI   | ETHPC                                                  | 39 |

|   | 3.3.2 E    | PI                                                     | 41 |

|   | 3.4 Infras | tructures: PPI4HPC, HBP                                | 42 |

|   | 3.4.1 PI   | P14HPC                                                 | 42 |

|   | 3.4.2 H    | BP: FENIX and ICEI project                             | 42 |

| 4 | Core Tech  | nologies and Components                                | 44 |

|   | 4.1 Proces | ssors                                                  | 44 |

|   | 4.1.1 x8   | 86_64 processors                                       | 44 |

|   | 4.1.1.1    | Intel x86_64 processors                                | 44 |

|   | 4.1.1.1    | .1 Intel Cascade Lake Scalable Processor               | 44 |

|   | 4.1.1.1    | .2 Intel Cascade Lake Advanced Performance             | 45 |

|   | 4.1.1.1    | .3 Intel Future (Cooper Lake and Ice Lake)             | 45 |

|   | 4.1.1.2    | AMD x86_64 processors                                  | 45 |

|   | 4.1.1.2    | 1.1 AMD EPYC (based on Zen)                            | 45 |

|   | 4.1.1.2    | 2.2 AMD 2nd Gen Ryzen and Threadripper (based on Zen+) | 46 |

|   | 4.1.1.2    | 2.3 AMD EPYC - Rome (based on Zen 2)                   | 46 |

|   | 4.1.1.2    | 2.4 AMD Future (based on Zen 3, 4, 5)                  | 47 |

|   | 4.1.2 A    | RM processors                                          | 47 |

|   | 4.1.3 PC   | OWER processors                                        | 49 |

|   | 4.2 Highly | parallel components/compute engines                    | 50 |

|   | 4.2.1 $G$  | PUs                                                    | 50 |

|   | 4.2.1.1    | AMD                                                    | 50 |

| 4.2.     | 1.2 NVIDIA                                                | 50 |

|----------|-----------------------------------------------------------|----|

| 4.2.     | 1.3 Comparison - NVIDIA vs AMD                            | 51 |

| 4.2.2    | Others                                                    | 51 |

| 4.3 N    | Iemory technologies (volatile non-volatile)               | 51 |

| 4.3.1    | Volatile memory technologies                              | 51 |

| 4.3.2    | Non-Volatile memory technologies                          | 52 |

| 4.4 In   | nterconnect                                               | 52 |

| 4.4.1    | Omni-Path, InfiniBand, BXI                                | 52 |

| 4.4.2    | Spectrum Ethernet, Slingshot                              | 53 |

| 4.4.3    | Gen-Z, EXTOLL, Dolphin                                    | 54 |

| 5 Data S | Storage and Data Management – Technologies and Components | 55 |

|          | Offline Storage (tapes)                                   |    |

| 5.1.1    | IBM tape storage                                          | 55 |

| 5.1.2    | Spectra Logic tape storage                                | 55 |

| 5.1.3    | Oracle StorageTek tape storage                            | 56 |

| 5.1.4    | Quantum tape storage                                      | 56 |

| 5.1.5    | Performance optimizations for tapes                       | 56 |

| 5.1.6    | LTO media patent dispute                                  | 57 |

| 5.2 O    | Online storage (disk and flash)                           | 58 |

| 5.2.1    | DDN                                                       | 58 |

| 5.2.2    | Seagate                                                   | 59 |

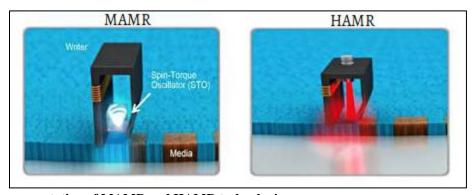

| 5.2.3    | HAMR and MAMR drives                                      | 59 |

| 6 Overv  | view of Vendor solutions/roadmaps                         | 62 |

| 6.1 A    | TOS-BULL                                                  | 62 |

| 6.1.1    | BullSequana XH2000                                        | 62 |

| 6.1.2    | BullSequana X1000                                         | 63 |

| 6.1.3    | BullSequana X400                                          | 63 |

| 6.1.4    | BullSequana X800                                          | 63 |

| 6.1.5    | BullSequana X550                                          | 63 |

| 6.2 C    | 'ray                                                      | 64 |

| 6.2.1    | Cray computing product line                               | 64 |

| 6.2.     | 1.1 Cray Shasta supercomputer                             | 64 |

| 6.2.     | 1.2 Cray XC series supercomputer                          | 65 |

|            | 6.2.1.3 Cray CS series cluster supercomputers | 65 |

|------------|-----------------------------------------------|----|

| 6.2        | 2.2 Cray analytics and AI                     | 66 |

| 6.3        | Fujitsu                                       | 66 |

| 6.4        | HPE                                           | 67 |

| 6.5        | Huawei                                        | 68 |

| 6.6        | IBM                                           | 68 |

| <b>6.7</b> | Lenovo                                        | 69 |

| 6.8        | NEC                                           | 69 |

| 7 Pa       | aradigm shifts in HPC technologies            | 70 |

| 7.1        | AI                                            | 70 |

| 7.2        | Heterogeneous architectures                   | 70 |

| 7.3        | Neuromorphic computing                        | 71 |

| 8 Co       | onclusion                                     | 73 |

# **List of Figures**

| Figure 1: System share in Top500 and Green500.                                                 | 7       |

|------------------------------------------------------------------------------------------------|---------|

| Figure 2: Performance share in Top500.                                                         | 8       |

| Figure 3: Countries system share over time (Top500).                                           | 9       |

| Figure 4: Percentage of cumulative $R_{max}$ values (in GFlop/s) for countries (Top500).       | Y-axis  |

| represents the percentage of R <sub>max</sub> values                                           | 10      |

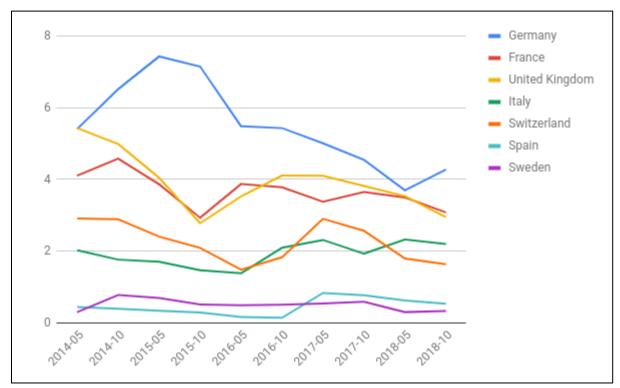

| Figure 5: Percentage of cumulative R <sub>max</sub> values (in GFlop/s) for European countries | 11      |

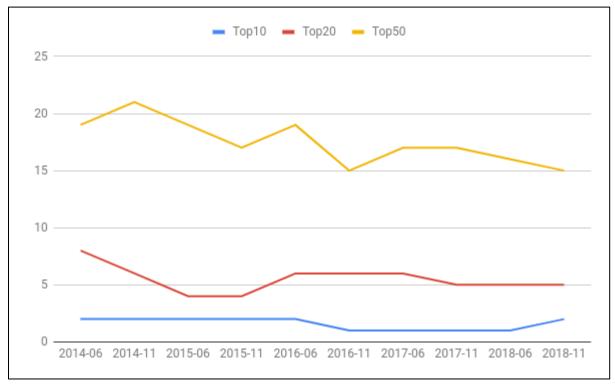

| Figure 6: Systems share in Top10/20/50 for Europe                                              | 12      |

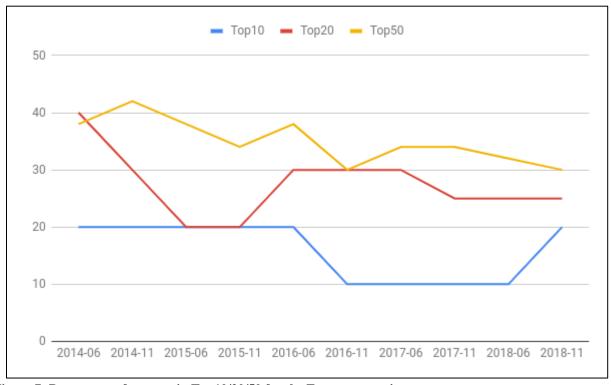

| Figure 7: Percentage of systems in Top10/20/50 for the Europe countries                        | 12      |

| Figure 8: Fraction of systems equipped with accelerators (Top 50).                             | 13      |

| Figure 9: Fraction of systems equipped with accelerators (November 2018)                       | 14      |

| Figure 10: Average age of the systems in years.                                                | 15      |

| Figure 11: Top50 vendors (world).                                                              | 16      |

| Figure 12: Top50 vendors (Europe).                                                             | 16      |

| Figure 13: The number of Bull systems.                                                         | 17      |

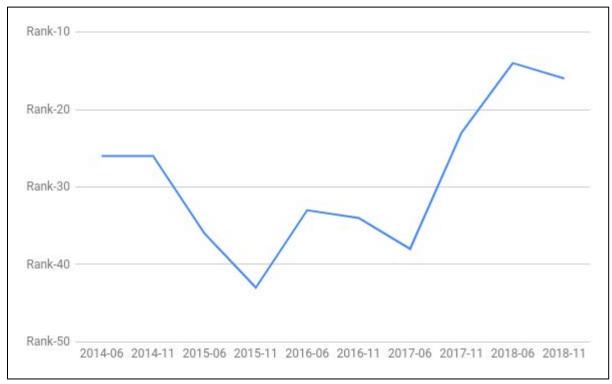

| Figure 14: The best rank achieved by a system from Bull in Top500.                             | 18      |

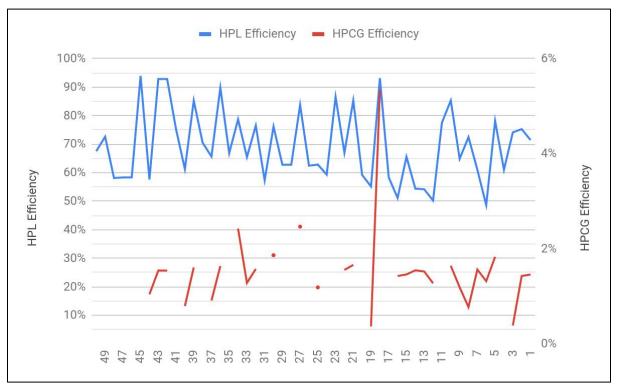

| Figure 15: HPL vs. HPCG efficiency in the top50 comparison (% of R <sub>peak</sub> )           | 19      |

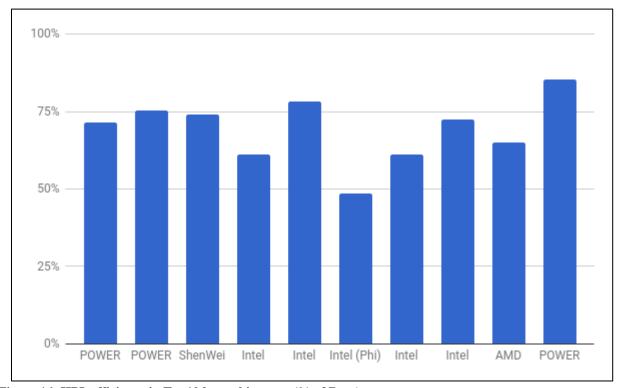

| Figure 16: HPL efficiency in Top10 by architecture (% of R <sub>peak</sub> ).                  | 20      |

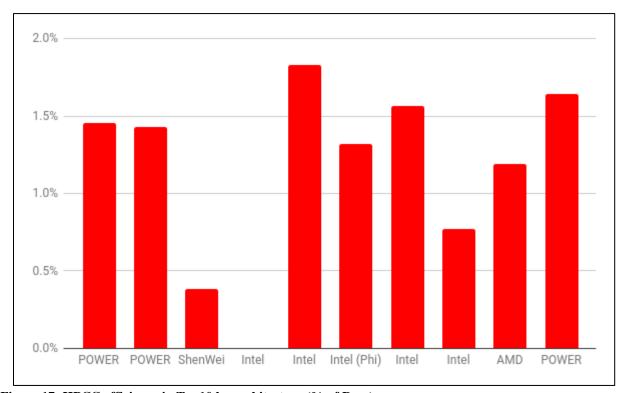

| Figure 17: HPCG efficiency in Top10 by architecture (% of R <sub>peak</sub> ).                 | 20      |

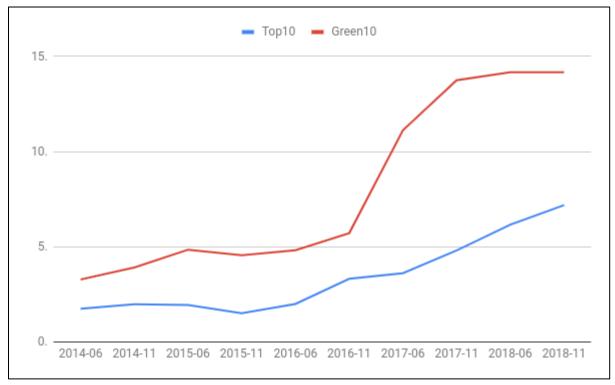

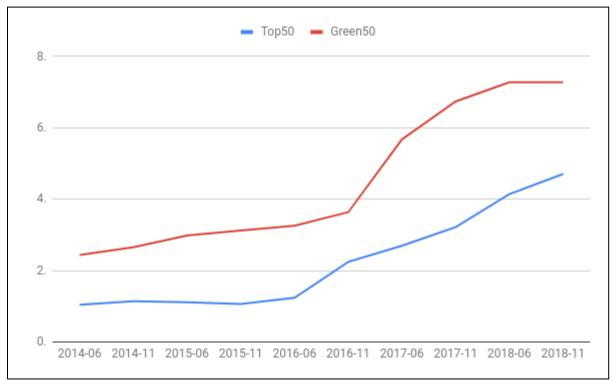

| Figure 18: Average energy efficiency [GFlop/s/W] in Top10 and Green10                          | 21      |

| Figure 19: Average energy efficiency [GFlop/s/W] in Top50 and Green50                          | 22      |

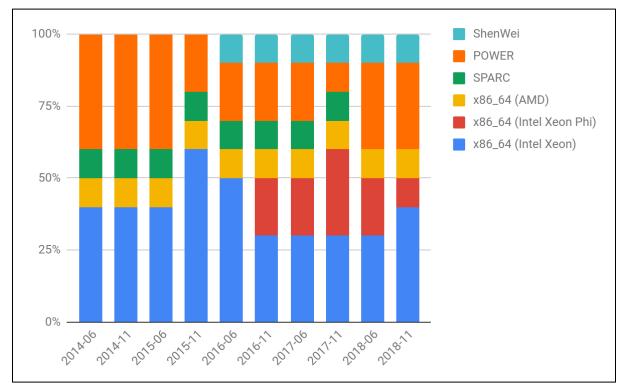

| Figure 20: Architectures in the top10                                                          | 23      |

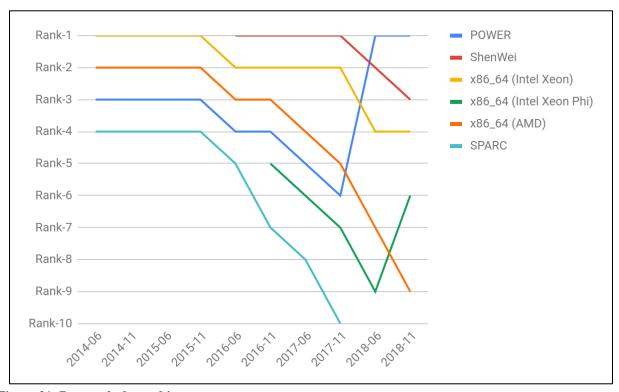

| Figure 21: Best ranks by architecture.                                                         | 23      |

| Figure 22: Exascale initiatives schedule and efforts from US, EU, China and Japan              | (source |

| Hyperion)                                                                                      | 24      |

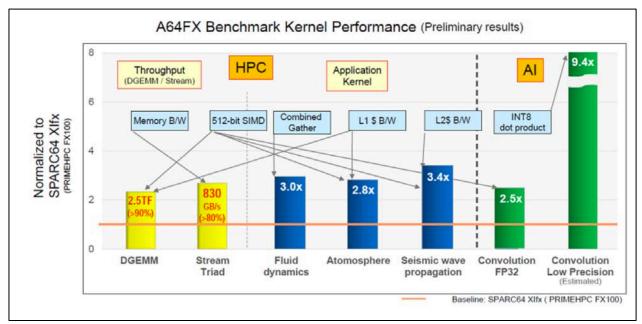

| Figure 23: A64FX Benchmark Kernel Performance preliminary results                              | 27      |

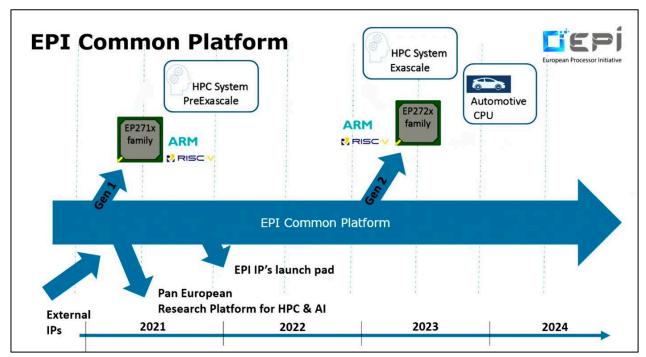

| Figure 24: European Processor Initiative roadmap                                               | 29      |

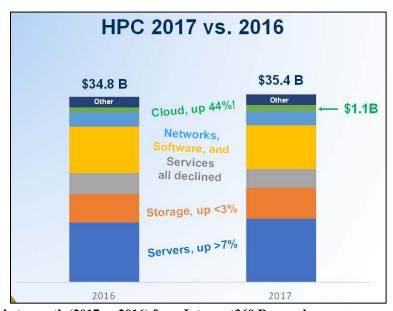

| Figure 25: HPC Market growth (2017 vs 2016) from Intersect360 Research                         | 30      |

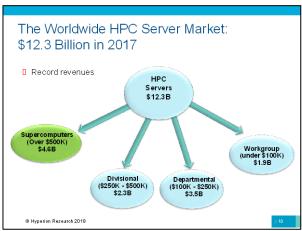

| Figure 26: Worldwide HPC Server Market from Hyperion Research                                  | 31      |

| Figure 27: The 4U appliance of DDN SFA18k                                                      | 58      |

| Figure 28: The presentation of MAMR and HAMR technologies                                      |         |

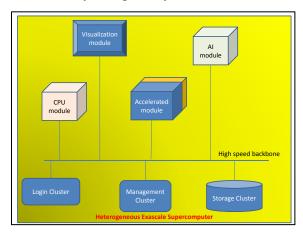

| Figure 29: A Potential Exascale system relying on a heterogeneous architecture                 | 71      |

| Figure 30: BrainScale system at University Heidelberg [157]                                    | 72      |

## **List of Tables**

| Table 1: Top10 systems in benchmark results for Top500/Green500/HPCG/IO500         | 5        |

|------------------------------------------------------------------------------------|----------|

| Table 2: Leading countries systems shares in the Top500                            | 10       |

| Table 3: HPC 2017 Revenue by Vertical (Intersect360)                               | 30       |

| Table 4: HPC Server Marker by vendor from Hyperion Research                        | 31       |

| Table 5: Worldwide HPC Server Market Forecasts by Hyperion Research                |          |

| Table 6: Broader HPC Market Forecasts by Hyperion Research                         | 32       |

| Table 7: Comparison of different server-class ARM-based processors                 | 48       |

| Table 8: IBM POWER9 processor as available for the 8335-GTW model of the IBM AC922 | 2 server |

| as used for Summit [80][81]                                                        | 49       |

| Table 9: LTO and Enterprise tape capacity and bandwidth                            | 57       |

| Table 10: MAMR and HAMR comparison of technologies                                 |          |

### References and Applicable Documents

- [1] <a href="https://www.top500.org/">https://www.top500.org/</a>

- [2] https://www.top500.org/green500/

- [3] <a href="http://www.hpcg-benchmark.org/">http://www.hpcg-benchmark.org/</a>

- [4] https://www.vi4io.org/io500/start

- [5] PRACE-5IP D5.1 Deliverable "Market and Technology Watch Report Year 1", 2018

- [6] PRACE-4IP D5.2 Deliverable "Market and Technology Watch Report Year 2. Final summary of results gathered", 2017

- [7] PRACE-4IP D5.1 Deliverable "Market and Technology Watch Report Year 1", 2016

- [8] Tsubame 3, Japan's 'AI' supercomputer became operational 1st August 2017 https://www.nextplatform.com/2017/08/22/inside-view-tokyo-techs-massive-tsubame-3-supercomputer/

- [9] <a href="https://www.olcf.ornl.gov/olcf-resources/compute-systems/summit/">https://www.olcf.ornl.gov/olcf-resources/compute-systems/summit/</a>

- [10] <a href="https://computation.llnl.gov/computers/sierra">https://computation.llnl.gov/computers/sierra</a>

- [11] https://www.nitrd.gov/nsci/

- [12] https://www.exascaleproject.org/

- [13] https://eurohpc-ju.europa.eu/

- [14] https://www.intersect360.com/

- [15] https://hyperionresearch.com/

- [16] https://kubernetes.io/

- [17] https://www.sylabs.io/singularity/

- [18] https://github.com/NERSC/shifter

- [19] https://www.slideshare.net/AmazonWebServices/the-nitro-project-nextgeneration-ec2-infrastructure-aws-online-tech-talks

- [20] https://www.prnewswire.com/news-releases/marvell-technology-completes-acquisition-of-cavium-300676912.html

- [21] https://www.broadcom.com/company/news/financial-releases/2357930

- [22] https://www.arista.com/en/company/news/press-release/6070-pr-20180912

- [23] https://news.hpe.com/hpe-to-acquire-plexxi/

- [24] https://news.arubanetworks.com/press-release/hpe-acquire-cape-networks

- [25] https://www.anandtech.com/show/12989/mips-acquired-by-wave-computing

- [26] https://www.onestopsystems.com/article/oss-acquires-bressner-technology-expands-european-presence

- [27] https://www.hpcwire.com/off-the-wire/ibm-to-acquire-red-hat/

- [28] https://www.hpcwire.com/off-the-wire/ddn-completes-60-million-tintri-acquisition-and-enters-enterprise-virtualization-market/

- [29] https://www.hpcwire.com/off-the-wire/xilinx-announces-the-acquisition-of-deephi-tech/

- [30] https://www.hpcwire.com/off-the-wire/storage-leader-ddn-acquires-lustre-file-system-capability-from-intel/ https://www.hpcwire.com/off-the-wire/storage-leader-ddn-acquires-lustre-file-system-capability-from-intel/

- [31] https://www.oracle.com/corporate/acquisitions/talari/

- [32] https://www.oracle.com/corporate/acquisitions/datafox/

- [33] https://www.oracle.com/corporate/pressrelease/oracle-buys-datascience-051618.html

- [34] https://news.microsoft.com/2018/06/04/microsoft-to-acquire-github-for-7-5-billion/

- [35] PRACE 5IP Deliverable D2.2 "Report on stakeholder management"

- [36] https://ec.europa.eu/programmes/horizon2020/en/news/21-new-h2020-high-performance-computing-projects

- [37] https://www.etp4hpc.eu/cppp-monitoring.html

- [38] https://ec.europa.eu/digital-single-market/en/eurohpc-joint-undertaking

- [39] Council Regulation (EU) 2018/1488 of 28 September 2018 establishing the European High Performance Computing Joint Undertaking ST/10594/2018/INIT

- [40] https://eur-lex.europa.eu/legal-content/EN/TXT/PDF/?uri=CELEX:32018R1488&from=EN

- [41] http://www.prace-ri.eu/postitionpaper-eurohpc-prace-2019/

- [42] http://www.etp4hpc.eu/

- [43] http://www.etp4hpc.eu/membership.html

- [44] http://www.bdva.eu/

- [45] https://ec.europa.eu/digital-agenda/en/high-performance-computing-contractual-public-private-partnership-hpc-cppp

- [46] http://www.bdva.eu/PPP

- [47] https://exdci.eu/

- [48] https://exdci.eu/about-exdci

- [49] https://www.eurolab4hpc.eu/

- [50] www.focus-coe.eu/

- [51] https://ec.europa.eu/programmes/horizon2020/en/news/overview-eu-funded-centres-excellence-computing-applications

- [52] https://exdci.eu/collaboration/coe

- [53] http://www.deep-project.eu/deep-project

- [54] http://montblanc-project.eu/

- [55] https://euroexa.eu/

- [56] https://ec.europa.eu/digital-single-market/en/news/european-processor-initiative-consortium-develop-europes-microprocessors-future-supercomputers

- [57] https://www.ppi4hpc.eu/

- [58] https://ec.europa.eu/digital-single-market/en/public-procurement-innovative-solutions

- [59] https://ted.europa.eu/TED/notice/udl?uri=TED:NOTICE:202138-2018:TEXT:EN:HTML

- [60] https://www.humanbrainproject.eu/en/

- [61] https://fenix-ri.eu/

- [62] AnandTech, "Intel shows Xeon scalable gold 6138p with integrated FPGA shipping to vendors" (https://www.anandtech.com/show/12773/intel-shows-xeon-scalable-gold-6138p-with-integrated-fpga-shipping-to-vendors)

- [63] HPCwire, "Requiem for a Phi: Knights Landing Discontinued", (https://www.hpcwire.com/2018/07/25/end-of-the-road-for-knights-landing-phi/)

- [64] ALCF, "ALCF Aurora 2021 Early Science Program: Data and Learning Call For Proposals", (https://www.alcf.anl.gov/alcf-aurora-2021-early-science-program-data-and-learning-call-proposals)

- [65] Wikichip, "Intel Cascade Lake Brings Hardware Mitigations, AI Acceleration, SCM Support" https://fuse.wikichip.org/news/1773/intel-cascade-lake-brings-hardware-mitigations-ai-acceleration-scm-support/

- [66] R. Hazra "Intel Keynote at SC2018"

- [67] Wikichip, "Cascade Lake AP Cores Intel" (https://en.wikichip.org/wiki/intel/cores/cascade\_lake\_ap)

- [68] STH, "Intel Cooper Lake Xeon For Training Details from Architecture Day 2018" (https://www.servethehome.com/intel-cooper-lake-xeon-for-training-details-from-architecture-day-2018/)

- [69] AnandTech, "Intel Server Roadmap: 14nm Cooper Lake in 2019, 10nm Ice Lake in 2020", (https://www.anandtech.com/show/13194/intel-shows-xeon-2018-2019-roadmap-cooper-lakesp-and-ice-lakesp-confirmed)

- [70] wccftech, "AMD Zen 2 Based 7nm Rome Server Processors Were Designed To Compete Favorably With Intel Ice Lake-SP Xeon CPUs, Aiming For Multi-Digit Server Market Share Gains" (https://wccftech.com/amd-epyc-rome-zen-2-7nm-cpus-compete-favorably-against-intel-ice-lake-xeons/)

- [71] AnadTech, "AMD's future in servers: New 7000 series CPUs launched and EPYC analysis" (https://www.anandtech.com/show/11551/amds-future-in-servers-new-7000-series-cpus-launched-and-epyc-analysis)

- [72] top500, "AMD Notches EPYC Supercomputer Win with Next-Generation Zen Processor" (https://www.top500.org/news/amd-notches-epyc-supercomputer-win-with-next-generation-zen-processor/)

- [73] Feldmann M. Feldmann, "China Reveals Third Exascale Prototype", top500.org, 22 October 2018.

- [74] Ampere Computing, "Ampere 64-bit ARM Processor", product brief (https://amperecomputing.com/wp-content/uploads/2018/02/ampere-product-brief.pdf).

- [75] Cavium, "ThunderX2 CN99XX Product Brief", product brief (https://www.marvell.com/documents/cmvd78bk8mesogdusz6t/).

- [76] Huawei, "Huawei Unveils Industry's Highest-Performance ARM-based CPU", press release (https://www.huawei.com/en/press-events/news/2019/1/huawei-unveils-highest-performance-arm-based-cpu).

- [77] Wikichip, "Kunpeng 920 (Hi1620) HiSilicon", https://en.wikichip.org/wiki/hisilicon/hi16xx/hi1620.

- [78] Toshio Yoshida, "Fujitsu High Performance CPU for the Post-K Computer", presentation at Hot Chips 2018.

- [79] DDN, "DDN Unveils Professional Support for Lustre Clients on ARM-based Platforms", press release, 12 November 2018.

- [80] IBM, "POWER9 Processor User's Manual", April 2018.

- [81] IBM, "IBM Power System AC922: Introduction and Technical Overview", IBM Redbook, March 2018.

- [82] June 11, 2018, https://www.amd.com/en/press-releases/2018-11-06-next-era-artificial-intelligence-and-high-performance-computing-hpc

- [83] November 8, 2018, https://www.top500.org/news/amd-introduces-first-7nm-datacenter-gpus/

- [84] September 12, 2018, https://nvidianews.nvidia.com/news/new-nvidia-data-center-inference-platform-to-fuel-next-wave-of-ai-powered-services

- [85] September 13, 2018, https://www.top500.org/news/nvidia-unveils-new-inferencing-gpu-for-datacenter/

- [86] January 16, 2019, https://insidehpc.com/2019/01/nvidia-t4-gpus-come-to-google-cloud-for-high-speed-machine-learning/

- [87] November 7, 2018, https://www.nextplatform.com/2018/11/07/competition-finally-comesto-datacenter-gpu-compute/

- [88] M. Feldman "CPU wars and exascale clarity: HPC in 2019" https://www.nextplatform.com/2019/01/11/cpu-wars-and-exascale-clarity-hpc-in-2019/

- [89] Brett Williams, Micron, Meeting at SC18, Dallas, TX, US, 2018

- [90] SK Hynix, https://www.techquila.co.in/sk-hynix-develops-first-16-gb-ddr5-5200-memory-chip/

- [91] JEDEC, https://www.jedec.org/news/pressreleases/jedec-updates-groundbreaking-high-bandwidth-memory-hbm-standard-0

- [92] Micron, http://investors.micron.com/static-files/36fd1838-b055-4e8c-97a4-972d4a1ad0cf

- [93] Micron, https://www.micron.com/-/media/client/global/documents/products/product-flyer/nvdimm\_flyer.pdf?la=en

- [94] July 19, 2018, https://www.hpcwire.com/2018/07/19/infiniband-still-tops-supercomputing/

- [95] November 15, 2018, http://www.mellanox.com/solutions/hpc/top500.php

- [96] November 12, 2018, https://www.businesswire.com/news/home/20181112005379/en/Mellanox-InfiniBand-Ethernet-Solutions-Accelerate-Majority-TOP500

- [97] October 24, 2018, https://insidehpc.com/2018/10/interconnect-future-paving-road-exascale/

- [98] Mellanox, http://www.mellanox.com/related-docs/whitepapers/WP\_Mellanox\_Socket\_Direct.pdf

- [99] Top500.org, https://www.top500.org/news/leaked-intel-roadmap-reveals-some-surprises-for-hpc-customers/

- [100] October 30, 2018, https://globenewswire.com/news-release/2018/10/30/1639203/0/en/Supercomputing-Leader-Cray-Introduces-First-Exascale-class-Supercomputer.html

- [101] October 30, 2018, http://investors.cray.com/phoenix.zhtml?c=98390&p=irol-newsArticle&ID=2374181

- [102] November 12, 2018, https://globenewswire.com/news-release/2018/11/12/1649853/0/en/Atos-launches-new-BullSequana-Hybrid-supercomputer-for-AI-augmented-simulation.html

- [103] November 29, 2018, <a href="https://www.nextplatform.com/2018/11/29/atos-rejiggers-sequana-supercomputers-adds-amd-rome-cpus/">https://www.nextplatform.com/2018/11/29/atos-rejiggers-sequana-supercomputers-adds-amd-rome-cpus/</a>

- [104] HPE, https://h20195.www2.hpe.com/v2/GetDocument.aspx?docname=a00016640enw&doctype=quickspecs&doclang=EN\_US&searchquery=&cc=us&lc=en

- [105] Ethernet Alliance, https://insidehpc.com/2018/03/new-2018-ethernet-roadmap-looks-future-speeds-1-6-terabits-s/

- [106] Mellanox, http://www.mellanox.com/page/press\_release\_item?id=1899

- [107] The Next Platform, https://www.nextplatform.com/2018/01/21/mellanox-trims-reach-profitable-1-billion/

- [108] December 19, 2018, http://www.mellanox.com/page/products\_dyn?product\_family=280&mtag=sn3000\_label

- [109] Mellanox, http://www.mellanox.com/related-docs/prod\_eth\_switches/BR\_SN3000\_Series.pdf

- [110] October 30, 2018, https://www.nextplatform.com/2018/10/30/cray-slingshots-back-into-hpc-interconnects-with-shasta-systems/

- [111] October 30, 2018, https://www.cray.com/blog/meet-slingshot-an-innovative-interconnect-for-the-next-generation-of-supercomputers/

- [112] Jeff Squyres, Atri Indiresay, Cisco, Meeting at SC18, Dallas, TX, US, 2018

- [113] Matt Mohr, ARISTA, Meeting at SC18, Dallas, TX, US, 2018

- [114] Dr. Niels Burkhardt, Extoll, Meeting at SC18, Dallas, TX, US, 2018

- [115] Kurtis Bowman, Gen-Z booth, Meeting at SC18, Dallas, TX, US, 2018

- [116] Paul Wade, Dolphin ICS, Meeting at SC18, Dallas, TX, US, 2018

- [117] https://www.dolphinics.com/download/WHITEPAPERS/Dolphin\_Express\_reflective\_mem ory.pdf

- $[118] \ https://spectralogic.com/2018/08/06/the-new-enterprise-drive-a-deeper-look-into-spectras-taos-feature-for-lto-tape-libraries/$

- [119] https://cds.cern.ch/record/2282014?ln=en

- [120] https://indico.cern.ch/event/730908/contributions/3153156/attachments/1732268/2800425/LTO-CERN-HEPiX-Oct-2018-germancancio.pdf

- [121] http://www.bdva.eu/sites/default/files/AI-Position-Statement-BDVA-Final-12112018.pdf

- [122] https://www.prophetstor.com/federator-ai/

- [123] November 6, 2018, https://insidehpc.com/2018/11/ddn-showcase-worlds-fastest-storage-sc18/

- [124] November 13, 2018, https://www.ddn.com/press-releases/ddn-hpc-storage-innovation-leadership-recognized-hpcwire/

- [125] January 22, 2019, <a href="https://www.ddn.com/press-releases/ddn-turnaround-tintri-wins-information-technology-deal-of-the-year-award/">https://www.ddn.com/press-releases/ddn-turnaround-tintri-wins-information-technology-deal-of-the-year-award/</a>

- [126] June 25, 2018, https://www.hpcwire.com/off-the-wire/storage-leader-ddn-acquires-lustre-file-system-capability-from-intel/

- [127] January 30, 2019, https://www.ddn.com/blog/storage-industry-crystal-ball-2019-predictions/

- [128] June 21, 2018, https://blog.seagate.com/enterprises/seagate-demonstrate-advanced-technology-ocp-summit-2018-support-accelerated-hyperscale-demand-data-growth/

- [129] September 10, 2018, https://www.hpcwire.com/off-the-wire/seagate-unveils-industrys-most-advanced-14tb-data-storage-portfolio/

- [130] September 11, 2018, https://insidehpc.com/2018/09/seagate-rolls-14-terabyte-hard-drives/

- [131] August 9, 2018, https://blog.seagate.com/intelligent/open-data-center-summit-seagate-showcases-latest-enterprise-ssds-hdds/

- [132] November 6, 2018, https://insidehpc.com/2018/11/predictions-sc18-change-climate-hpc/

- [133] Consumer Technology Association https://www.ces.tech/

- [134] June 27, 2018, http://www.advancedclustering.com/technologies/beegfs-parallel-file-storage/

- [135] October 26, 2018, https://www.hpcwire.com/off-the-wire/beegfs-based-burst-buffer-enables-world-record-hyperscale-data-distribution/

- [136] November 14, 2018, http://www.advancedclustering.com/advanced-clustering-receives-beegfs-rising-bee-award-sc18/

- [137] July 6, 2018, https://www.itnews.com.au/news/csiro-removes-hpc-bottleneck-with-storage-upgrade-496958

- [138] November 26, 2018, https://www.hpcwire.com/2018/11/26/move-over-lustre-spectrum-scale-here-comes-beegfs/

- [139] https://www.advancedhpc.com/solutions/parallel-file-systems/beegfs/

- [140] Lubos Kolar, HPE, Meeting at SC18, Dallas, TX, US, 2018

- [141] https://openpowerfoundation.org/

- [142] S. Oehme, "Spectrum Scale CORAL Enhancements", Spectrum Scale User Group @ SC Asia, Singapore, March 2018

(http://files.gpfsug.org/presentations/2018/Singapore/Sven\_Oehme\_ESS\_in\_CORAL\_proje ct\_update.pdf)

- [143] S. Oehme, "Spectrum Scale performance update", HEPIX 2016 (https://indico.cern.ch/event/531810/contributions/2306222/attachments/1357265/2053960/Spectrum\_Scale-HEPIX\_V1a.pdf).

- [144] https://github.com/openstack/swiftonfile

- [145] D. Hillebrand et al., "OpenStack SwiftOnFile: User Identity for Cross Protocol Access Demystified", SNIA Storage Developer Conference, Santa Clara, 2015 (https://researcher.watson.ibm.com/researcher/files/us-dhildeb/OpenStack%20SwiftOnFile%20-%20User%20Identity%20for%20Cross%20Protocol%20Access%20Demystified.pdf)

- [146] Fujitsu, "PRIMERGY CX400 M4", 2017 (http://www.fujitsu.com/global/Images/primergy-cx400-m4.pdf).

- [147] Fujitsu, "Fujitsu Completes Post-K Supercomputer CPU Prototype, Begins Functionality Trials", June 2018 (http://www.fujitsu.com/global/about/resources/news/press-releases/2018/0621-01.html).

- [148] Toshio Yoshida, "Fujitsu High Performance CPU for the Post-K Computer", presentation at Hot Chips 2018.

- [149] Yuichiro Ajima et al., "The Tofu Interconnect D", IEEE Cluster 2018 (http://www.fujitsu.com/jp/Images/the-tofu-interconnect-d.pdf).

- [150] Huawei, "Huawei Unveils Industry's Highest-Performance ARM-based CPU", press release, 2019 (https://www.huawei.com/en/press-events/news/2019/1/huawei-unveils-highest-performance-arm-based-cpu).

- [151] https://atos.net/en/products/high-performance-computing-hpc/bullsequana-x-supercomputers

- [152] https://www.hpcwire.com/2018/08/14/cern-incorporates-ai-into-physics-based-simulations/

- [153] https://www.nextplatform.com/2017/05/15/will-ai-replace-traditional-supercomputing-simulations/

- [154] https://ldrd-annual.llnl.gov/ldrd-annual-2016/computing/brain

- [155] http://www.teratec.eu/library/pdf/forum/2018/Presentations/A7\_05\_Alexis\_Joly\_Inria\_For um\_Teratec\_2018.pdf

- [156] https://www.top500.org/news/julich-supercomputing-center-turns-to-modular-approach-to-deal-with-hpc-hpda-divide/

- [157] S. Schmitt et al., "Neuromorphic Hardware In The Loop: Training a Deep Spiking Network on the BrainScaleS Wafer-Scale System", 2017 International Joint Conference on Neural Networks (doi: 10.1109/IJCNN.2017.7966125).

- [158] M. Davies et al., "Loihi: A Neuromorphic Manycore Processor with On-Chip Learning", IEEE Micro, January/February 2018 (doi:10.1109/MM.2018.112130359).

- [159] Intel, "Intel Creates Neuromorphic Research Community to Advance 'Loihi' Test Chip", press release (https://newsroom.intel.com/editorials/intel-creates-neuromorphic-research-community)

- [160] S. Furber et al., "The SpiNNaker Project". Proceedings of the IEEE, 2014 (doi:10.1109/JPROC.2014.2304638).

- [161] S. van Albada et al., "Performance Comparison of the Digital Neuromorphic Hardware SpiNNaker and the Neural Network Simulation Software NEST for a Full-Scale Cortical Microcircuit Model", Front. Neurosci., 23 May 2018 (doi:10.3389/fnins.2018.00291).

- [162] Jun Sawada et al., "TrueNorth Ecosystem for Brain-Inspired Computing: Scalable Systems, Software, and Applications," SC16 Proceedings, 2016.

- [163] PRACE-5IP D5.4 Deliverable "HPC Infrastructures Workshop #9", 2018

# **List of Acronyms and Abbreviations**

| aichl Association International Cons Dut I venetif (legal form of the DDACE DI)                          |

|----------------------------------------------------------------------------------------------------------|

| aisblAssociation International Sans But Lucratif (legal form of the PRACE-RI)                            |

| AIArtificial Intelligence                                                                                |

| ABCIAl Bridging Cloud Infrastructure                                                                     |

| ASICApplication Specific Integrated Circuit                                                              |

| BDVABig Data Value Association                                                                           |

| BXIBull eXascale Interconnect (product by ATOS)                                                          |

| CAGRCompound Annual Growth Rate                                                                          |

| CoECenter of Excellence                                                                                  |

| cPPPcontractual Public Private Partnership                                                               |

| CPUCentral Processing Unit                                                                               |

| CUDACompute Unified Device Architecture (NVIDIA)                                                         |

| DoE(US) Department of Energy                                                                             |

| DPDouble Precision (64 bits)                                                                             |

| ECEuropean Commission                                                                                    |

| ECPExascale Computing Project                                                                            |

| ECIExascale Computing Initiative                                                                         |

| EFlop/sExa (= 10 <sup>18</sup> ) Floating point operations per second, also EFlops                       |

| EOSCEuropean Open Science Cloud                                                                          |

| ETP4HPCEuropean Technology Platform for High Performance Computing                                       |

| FenixFederated Engine for Information eXchange                                                           |

| FETHPCGeneric term for HPC calls for projects and the series of related projects which have              |

| been selected, under H2020 FET programme (Future and Emerging Technologies),                             |

| between 2014 and 2017                                                                                    |

| FP7Framework Programme 7                                                                                 |

| FPAFramework Partnership Agreement                                                                       |

| FPGAField Programmable Gate Array                                                                        |

| GBGiga (= $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte                                              |

|                                                                                                          |

| Gb/sGiga (= 10 <sup>9</sup> ) bits per second, also Gbit/s                                               |

| GB/sGiga (= 10 <sup>9</sup> ) Bytes (= 8 bits) per second, also GByte/s                                  |

| GÉANTCollaboration between National Research and Education Networks to build a multi-                    |

| gigabit pan-European network. The current EC-funded project as of 2015 is GN4.                           |

| GFlop/sGiga (= 10 <sup>9</sup> ) Floating point operations (usually in 64-bit, i.e. DP) per second, also |

| GF/s                                                                                                     |

| GHzGiga (= $10^9$ ) Hertz, frequency = $10^9$ periods or clock cycles per second                         |

| GPUGraphic Processing Unit                                                                               |

| GT/sGiga (10 <sup>9</sup> ) transfers per second                                                         |

| HBMHigh Bandwidth Memory                                                                                 |

| HBPHuman Brain Project                                                                                   |

| HDRInfiniBand interconnect generation called High Data Rate with link speed 200Gb/s                      |

| HPCHigh-Performance Computing; Computing at a high- performance level at any given                       |

| time; often used synonym with Supercomputing                                                             |

| HPCGHigh-Performance Conjugate Gradients                                                                 |

| HPDAHigh-Performance Data Analytics                                                                      |

|                                                                                                          |

| HPLHigh-Performance LINPACK                                                                               |

|-----------------------------------------------------------------------------------------------------------|

| ICEIInteractive Computing E-Infrastructure for the Human Brain Project                                    |

| ISCInternational Supercomputing Conference; European equivalent to the US based                           |

| SCxx conference. Held annually in Germany.                                                                |

| JUJoint Undertaking                                                                                       |

| KBKilo (= $2^{10} \sim 10^3$ ) Bytes (= 8 bits), also Kbyte                                               |

| LINPACKSoftware library for Linear Algebra                                                                |

|                                                                                                           |

| LTOLinear Tape-Open  Management Record (bighest decision making heady of the PRACE project)               |

| MB                                                                                                        |

| MBMega (= $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte                                               |

| MB/sMega (= 10 <sup>6</sup> ) Bytes (= 8 bits) per second, also MByte/s                                   |

| MFlop/sMega (= 10 <sup>6</sup> ) Floating point operations (usually in 64-bit, i.e. DP) per second, also  |

| MF/s                                                                                                      |

| MLMachine Learning                                                                                        |

| MPIMessage Passing Interface                                                                              |

| NICNetwork Interface Controller                                                                           |

| NSCINational Strategic Computing Initiative (USA)                                                         |

| NUDTNational University of Defence Technology (China)                                                     |

| NUMANon-Uniform Memory Access                                                                             |

| NVMeNon-Volatile Memory Express                                                                           |

| OPAOmni-Path Architecture                                                                                 |

| PAM-4Pulse Amplitude Modulation signalling for high-speed serial links                                    |

| PCPPre-Commercial Procurement                                                                             |

| PFlop/sPeta (= 10 <sup>15</sup> ) Floating-point operations (usually in 64-bit, i.e. DP) per second, also |

| PF/s or PF                                                                                                |

| PPIPublic Procurement of Innovative solutions                                                             |

| PRACEPartnership for Advanced Computing in Europe; Project Acronym                                        |

| PRACE 2 The current phase of the PRACE Research Infrastructure following the initial five-                |

| year period.                                                                                              |

| QSFPQuad Small Form-factor Pluggable                                                                      |

| R&DResearch and Development                                                                               |

| •                                                                                                         |

| R&IResearch and Innovation                                                                                |

| RIResearch Infrastructure                                                                                 |

| RIAResearch and innovation action (type of H2020 project)                                                 |

| SGASpecific Grant Agreement                                                                               |

| SMTSimultaneous Multithreading                                                                            |

| SRIAStrategic Research and Innovation Agenda                                                              |

| SVEScalable Vector Extension                                                                              |

| TBTechnical Board (group of PRACE Work Package leaders)                                                   |

| TBTera (= $2^{40} \sim 10^{12}$ ) Bytes (= 8 bits), also TByte                                            |

| TCOTotal Cost of Ownership. Includes recurring costs (e.g. personnel, power, cooling,                     |

| maintenance) in addition to the purchase and set-up cost.                                                 |

| TFlop/sTera (= $10^{12}$ ) Floating-point operations (usually in 64-bit, i.e. DP) per second, also        |

| TF/s or TF                                                                                                |

|                                                                                                           |

| TOp/sTera operations per second, also TOps or Tops or Top/s                         |  |  |  |  |  |

|-------------------------------------------------------------------------------------|--|--|--|--|--|

| Tier-0Denotes the apex of a conceptual pyramid of HPC systems. In this context, the |  |  |  |  |  |

| Supercomputing Research Infrastructure would host the Tier-0 systems; national or   |  |  |  |  |  |

| topical HPC centers would constitute Tier-1                                         |  |  |  |  |  |

| UPIUltra Path Interconnect, Intel technology to link multiple CPUs in coherent way  |  |  |  |  |  |

# **List of Project Partner Acronyms**

| BADW-LRZ          | Leibniz-Rechenzentrum der Bayerischen Akademie der Wissenschaften,                          |

|-------------------|---------------------------------------------------------------------------------------------|

|                   | Germany (3rd Party to GCS)                                                                  |

| BILKENT           | Bilkent University, Turkey (3rd Party to UYBHM)                                             |

| BSC               | Barcelona Supercomputing Center - Centro Nacional de Supercomputacion,                      |

|                   | Spain                                                                                       |

| CaSToRC           | Computation-based Science and Technology Research Center, Cyprus                            |

| CCSAS             | Computing Centre of the Slovak Academy of Sciences, Slovakia                                |

| CEA               | Commissariat à l'Energie Atomique et aux Energies Alternatives, France (3rd Party to GENCI) |

| CESGA             | Fundacion Publica Gallega Centro Tecnológico de Supercomputación de                         |

|                   | Galicia, Spain, (3rd Party to BSC)                                                          |

| CINECA            | CINECA Consorzio Interuniversitario, Italy                                                  |

|                   | Centre Informatique National de l'Enseignement Supérieur, France (3rd                       |

|                   | Party to GENCI)                                                                             |

| CNRS              | Centre National de la Recherche Scientifique, France (3rd Party to GENCI)                   |

| CSC               | CSC Scientific Computing Ltd., Finland                                                      |

| CSIC              | Spanish Council for Scientific Research (3rd Party to BSC)                                  |

| CYFRONET          | Academic Computing Centre CYFRONET AGH, Poland (3rd party to                                |

|                   | PNSC)                                                                                       |

| EPCC              | EPCC at The University of Edinburgh, UK                                                     |

| ETHZurich (CSCS). | Eidgenössische Technische Hochschule Zürich – CSCS, Switzerland                             |

| FIS               | Faculty of Information Studies, Slovenia (3rd Party to ULFME)                               |

| GCS               | Gauss Centre for Supercomputing e.V., Germany                                               |

| GENCI             | Grand Equipement National de Calcul Intensif, France                                        |

| GRNET             | Greek Research and Technology Network, Greece                                               |

| INRIA             | Institut National de Recherche en Informatique et Automatique, France (3rd                  |

|                   | Party to GENCI)                                                                             |

| IST               | Instituto Superior Técnico, Portugal (3rd Party to UC-LCA)                                  |

| IT4Innovations    | IT4Innovations National supercomputing centre at VŠB-Technical                              |

|                   | University of Ostrava, Czech Republic                                                       |

| IUCC              | Inter University Computation Centre, Israel                                                 |

| JUELICH           | Forschungszentrum Juelich GmbH, Germany                                                     |

|                   | Governmental Information Technology Development Agency, Hungary                             |

| KTH               | Royal Institute of Technology, Sweden (3rd Party to SNIC)                                   |

|                   | Linkoping University, Sweden (3rd Party to SNIC)                                            |

| NCSA              | National Centre for Supercomputing Applications, Bulgaria                                   |

| NTNU              | The Norwegian University of Science and Technology, Norway (3rd Party                       |

|                   | to SIGMA)                                                                                   |

| <del>_</del>      | National University of Ireland Galway, Ireland                                              |

|                   | Partnership for Advanced Computing in Europe aisbl, Belgium                                 |

|                   | Poznan Supercomputing and Networking Center, Poland                                         |

| RISCSW            | RISC Software GmbH                                                                          |

| RZG         | Max Planck Gesellschaft zur Förderung der Wissenschaften e.V., Germany    |

|-------------|---------------------------------------------------------------------------|

|             | (3 rd Party to GCS)                                                       |

| SIGMA2      | UNINETT Sigma2 AS, Norway                                                 |

| SNIC        | Swedish National Infrastructure for Computing (within the Swedish Science |

|             | Council), Sweden                                                          |

| SoC         | System on Chip                                                            |

| STFC        | Science and Technology Facilities Council, UK (3rd Party to EPSRC)        |

| SURFsara    | Dutch national high-performance computing and e-Science support center,   |

|             | part of the SURF cooperative, Netherlands                                 |

| UC-LCA      | Universidade de Coimbra, Labotatório de Computação Avançada, Portugal     |

| UCPH        | Københavns Universitet, Denmark                                           |

| UHEM        | Istanbul Technical University, Ayazaga Campus, Turkey                     |

| UiO         | University of Oslo, Norway (3rd Party to SIGMA)                           |

| ULFME       | Univerza v Ljubljani, Slovenia                                            |

| UmU         | Umea University, Sweden (3rd Party to SNIC)                               |

| UnivEvora   | Universidade de Évora, Portugal (3rd Party to UC-LCA)                     |

| UPC         | Universitat Politècnica de Catalunya, Spain (3rd Party to BSC)            |

| UPM/CeSViMa | Madrid Supercomputing and Visualization Center, Spain (3rd Party to BSC)  |

| USTUTT-HLRS | Universitaet Stuttgart – HLRS, Germany (3rd Party to GCS)                 |

| WCNS        | Politechnika Wrocławska, Poland (3rd Party to PNSC)                       |

|             |                                                                           |

## **Executive Summary**

This document is the second deliverable of PRACE-5IP Work Package 5 "Task 5.1 - Technology and market watch" and represents a periodic annual update on technology and market trends. It is thus the continuation of a well-established effort to carry out an assessment of the HPC market based on market surveys, supercomputing conferences, and exchanges between vendors and experts involved in the work package.

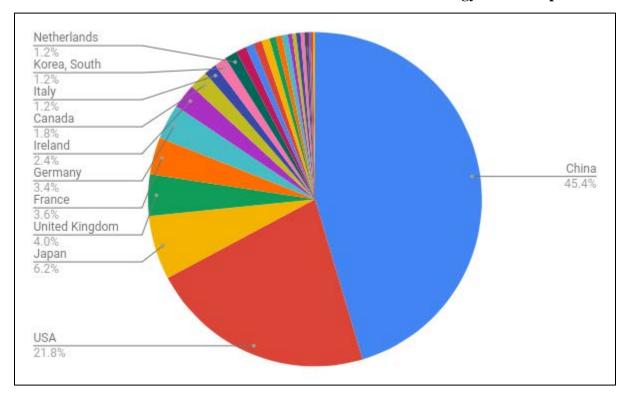

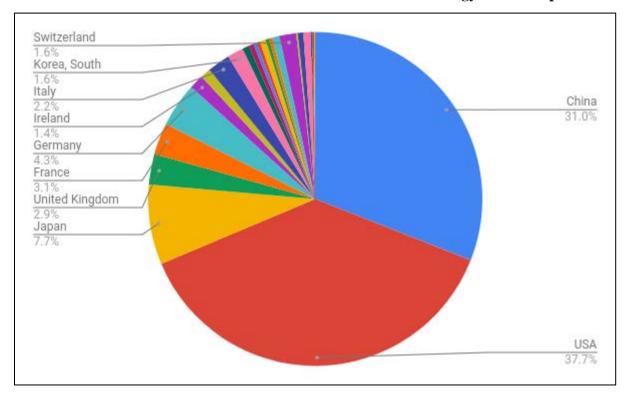

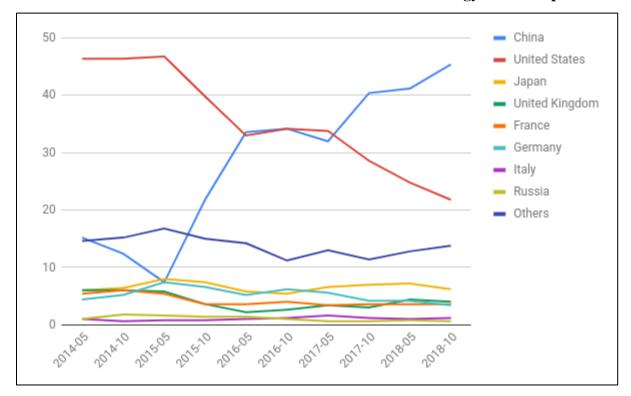

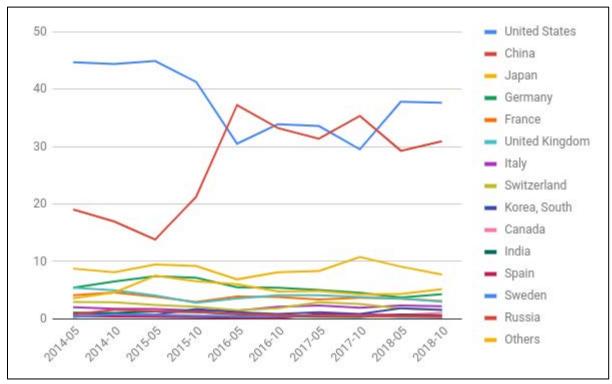

The Top500 (Nov 2018) list is still dominated by China and the United States, that rank very close to each other, with, this time, the United States in the first and second place, with 21.8% of system share and 37.7% of performance share, China on third and fourth position, with 45.4% of system share and 31% of performance share. Two machines installed in Europe are in the Top10: SuperMUC-NG (LRZ, Germany) and Piz Daint (CSCS, Switzerland). Japan still dominates the Green500 list with four supercomputers ranked in the Top10. The first and second ranked supercomputers in the Top500 list, Summit and Sierra, are also the machines showing the best HPCG performance. The only European supercomputer in the Top10 of HPCG is Piz Daint. A new benchmark related to IO performance (IO500) initiated in 2017 is gaining momentum with 63 entries while a proposal for a new benchmark on large scale deep learning called Deep500 have been presented.

Plans for exascale are well-defined in China, USA and Japan. In China, three tracks are explored in parallel with three prototypes deployed by Sugon, Tianhe, and Sunway (ShenWei) in 2018. In Japan, the post-K project, targeting exascale class supercomputer in 2021, is progressing on schedule with the test started on the first prototype of the ARM-based CPU developed by Fujitsu. In the United States, the ECP project is addressing application development, software technology, and hardware technology and exascale systems testbeds. In Europe, EuroHPC is a Joint Undertaking established in 2018 with, as one of its goals, to construct an exascale supercomputer based on European technology.

HPC as Cloud computing offering has already been available for some time and is a real option for some HPC workloads. It generally complements, rather than replaces, the traditional HPC systems. Big players like Amazon, Microsoft and Google have commercial offerings that target the HPC market. The main trend in 2018 for HPC is bare metal service, while solutions based on containers have some advantages in terms of redundancy and enhanced information security. Offers including GPU, targeting mostly AI, may also be of interest for HPC. Even quantum computing (IBM Quantum System for example) is also available in the cloud.

Regarding the consolidation in the HPC market, the acquisition of Cavium by Marvell is an important event since the ThunderX ARM-based processors are among the most promising for HPC.

In the EU landscape, EuroHPC is the central and overarching new piece, consolidating or recomposing the ecosystem. It brings the promise of better coordination and more funding for HPC in Europe, both for infrastructures and for R&I, including applications. In this context, existing entities like PRACE, ETP4HPC, and BDVA, need to evolve in order to take into account this new context. Among the coordination and support actions, EXDCI-2 continues the coordination of the

HPC ecosystem with important enhancements with respect to EXDCI, so as to better address the convergence of big data, cloud and HPC. On the R&I side, centers of excellence and FET HPC projects remain important and active players in the field while the new EPI (European Processor Initiative) is of major importance for Europe. On the infrastructure side, PPI4HPC and HBP are contributing respectively for deploying innovative equipment in HPC centers and developing a data infrastructure complementing the current supercomputer infrastructure.

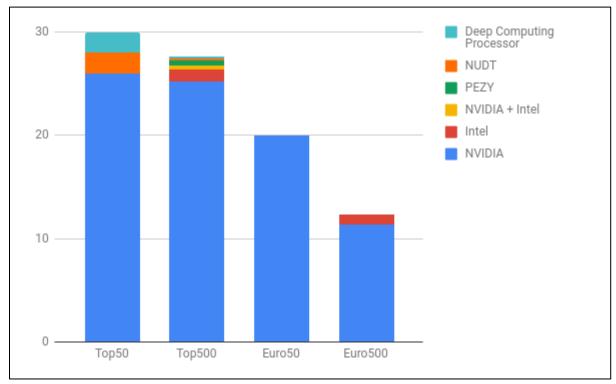

In terms of core technologies for HPC system processors, Intel is now facing the competition of new competitors: AMD with the EPYC architecture, and Marvell, with the ThunderX ARM-based processor family. Several large systems based on these processors have already been announced. The ARM ecosystem is very active with processors targeting HPC announced by Huawei and Fujitsu. The POWER processor, coupled with NVIDIA GPU, is used for the supercomputers Summit and Sierra, which are listed on position #1 and #2 of the Top500 list as of November 2018. In terms of accelerators for HPC, these systems mostly rely on NVIDIA GPUs with AMD being so far the only competitor but with less success than NVIDIA. FPGA is still a niche market.

The most used volatile memory is currently DDR4 which tops with a DIMM size of 128GB running at 2933MT/s. Another class of volatile memory technology important to HPC is High Bandwidth Memory (HBM), today usually implemented as stacked memory, allowing parallel access to multiple (up to 8) slices. It supports speeds up to 2GT/s. Non-volatile memory technologies are still emerging but may be used in the future on compute node and on IO systems.

Regarding data storage and data management, technologies and components are evolving, new services are being deployed some targeting specific workload like AI. Tape storage is still widely used with capacity increasing over time. This is the same for disk storage, DDN being the main player. Flash and non-volatile memories are expected to play an increasing role in the near future.

In terms of vendor solutions and roadmaps, HPE remains in the 2<sup>nd</sup> position in the HPC world with products derived from SGI (acquired by HPE). HPE has installed the largest ARM-based cluster in Sandia National Lab. Fujitsu continues to be the main provider of high-end HPC solutions in Japan. Chinese vendors (mostly Huawei, Lenovo) are actively investing in the HPC market. Atos/Bull currently has 22 supercomputers ranked in the Top500 and has announced a blade for ARM processors.

Paradigm shifts in HPC technologies include AI, heterogenous architectures, and neuromorphic computing. Since our last report, AI is gaining momentum in a number of dimensions: to assist regular HPC simulations ("augmented HPC") or to replace HPC simulation. HPC can also be used to create high fidelity training AI databases. Modular heterogeneous solutions are becoming widespread with the double objectives of limited power consumption and programmability. In this approach, the user will no longer see a supercomputer as a single homogeneous entity but rather as an aggregation of specialized modules sharing common resources such as parallel file systems or visualization nodes on a central network. The term "neuromorphic computing" broadly refers to compute architectures that are inspired by features of brains as found in nature. There is a strong interest, at the level of research, into such devices in the context of brain modelling as well as artificial intelligence and machine learning.

#### 1 Introduction

The PRACE-5IP Work Package 5 (WP5), "HPC Commissioning and Prototyping", is defined by three main tasks: T5.1 "Technology and market watch, vendor relationships independent of procurements"; T5.2 "Best practice for energy-efficient HPC center infrastructures design and operations"; T5.3 "Extended best practice guide for prototypes or demonstrators". WP5 aims to deliver updated information on the HPC ecosystem, market surveys and best practices, providing guidance to decision-makers at all levels.

In particular, Task 5.1 focuses on assessing the match between the current and upcoming system architectures and the requirements of the users. To this end, a strong effort was devoted to tracking the evolution of HPC technologies based on vendor roadmaps, as well as collecting updates coming from EU projects and initiatives. This task is the continuation of a well-established effort, using assessments of the HPC market based on market surveys, Top500 and Green500/HPCG lists analyses, supercomputing conferences, and exchanges between vendors and experts who are involved in the work package. Trends and innovations based on the work of prototyping activities in previous PRACE implementation projects are also exploited, as well as the observation of current or new technological R&D projects, such as the PRACE-3IP PCP, the Human Brain Project PCP, FP7 exascale projects, Horizon 2020 FETHPC1-2014 and follow-ups in future Work Programmes. The outcome of these activities is reported in this deliverable, that builds on the important work performed for the previous document – "Market and Technology Watch Report Year 1" – and complements its overall view.

The deliverable contains many technical details on recent HPC topics. It is intended for persons who are actively working in the HPC field. Practitioners should read this document to get an overview of developments on the infrastructure side and how this may affect planning for future data centers and systems. Users should refer to this document as an overall view of HPC hardware and expect some of the solutions described to be available to them in the near future. Developers should read this to gain knowledge of recent and future trends, in order to make informed decisions on the development of their applications.

The deliverable is organized into six main chapters. Besides this introduction, Chapter 1, it contains:

- Chapter 2: "Worldwide HPC landscape and market overview", which provides a geographical and market analysis, an overview of large EU and worldwide initiatives, and current trends on HPC cloud computing;

- Chapter 3: "EU landscape overview" which focuses on EU landscape, providing an update on the main projects and technology oriented initiatives;

- Chapter 4: "Core technologies and components" is a quick overview of processors, accelerators, memory and storage technologies and interconnect technologies;

- Chapter 5: "Data Storage and Data Management Technologies and Components" provides an overview of present storage models, architectures and solutions;

- Chapter 6: "Overview of Vendor solutions/roadmaps" tracks the evolution of main players' roadmaps;

**D5.2**

• Chapter 7: "Paradigm shifts in HPC technologies" which reports the most promising technologies for future HPC systems, including neuromorphic, AI and heterogeneous architectures.

### 2 Worldwide HPC landscape and Market overview

#### 2.1 Quick update of HPC worldwide

This section provides an overview of HPC worldwide, with a special focus on Europe based on statistical data provided from the Top500 [1], the Green 500 [2], the HPCG [3] and the IO500 [4] benchmarks. In the subsequent analysis, special attention is given to the 10, 20 and 50 most powerful systems in the world according to the Top500 and Green500 rankings.

#### 2.1.1 Countries

November 2018 results for  $R_{max}$  (HPL performance) values in Top500 (TFlop/s), power efficiency (GFlop/s/watt) values in Green 500, HPCG (PFlop/s) and IO500 ( $\sqrt{GiB*IOP}/s$ ) are presented Table 1.

|    | Top500                       | Green500                       | HPCG                         | IO500                                 |  |

|----|------------------------------|--------------------------------|------------------------------|---------------------------------------|--|

| 1  | USA (Summit)                 | Japan (Shoubu system B)        | USA (Summit)                 | USA (Summit)                          |  |

| 2  | USA (Sierra)                 | USA (DGX SaturnV Volta)        | USA (Sierra)                 | UK (Data Accelerator) <sup>a</sup>    |  |

| 3  | China (Sunway<br>TaihuLight) | USA (Summit) Japan (K Computer |                              | Computer) Republic of Korea (Nurion)  |  |

| 4  | China (Tianhe-2A)            | Japan (ABCI)                   | USA (Trinity)                | Japan (Oakforest-PACS) <sup>b</sup>   |  |

| 5  | Switzerland (Piz<br>Daint)   | Japan (TSUBAME3.0)             | Japan (ABCI)                 | USA (WekaIO)                          |  |

| 6  | USA (Trinity)                | USA (Sierra)                   | Switzerland (Piz Daint)      | Saudi Arabia (ShaheenII) <sup>c</sup> |  |

| 7  | Japan (ABCI)                 | Japan (AIST AI Cloud)          | China (Sunway<br>TaihuLight) | UK (Data Accelerator) <sup>d</sup>    |  |

| 8  | Germany (SuperMUC-NG)        | Spain (MareNostrum P9<br>CTE)  | Republic of Korea (Nurion)   | USA (Exascaler on GCP)                |  |

| 9  | USA (Titan)                  | China (PreE)                   | Japan (Oakforest-<br>PACS)   | Japan (Oakforest-PACS) <sup>e</sup>   |  |

| 10 | USA (Sequoia)                | Taiwan (Taiwania 2)            | USA (Cori)                   | Saudi Arabia (ShaheenII) <sup>f</sup> |  |

<sup>&</sup>lt;sup>a</sup> Filesystem: Lustre, Client nodes: 512, Client total procs: 4224

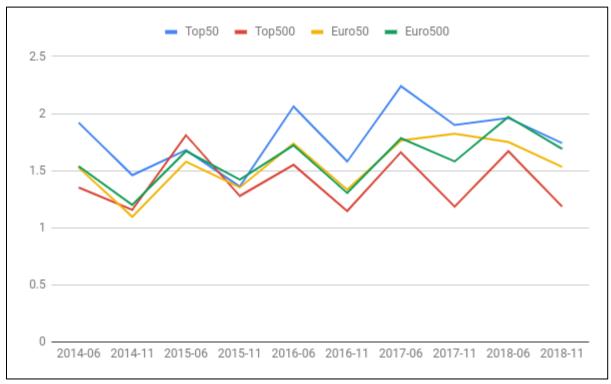

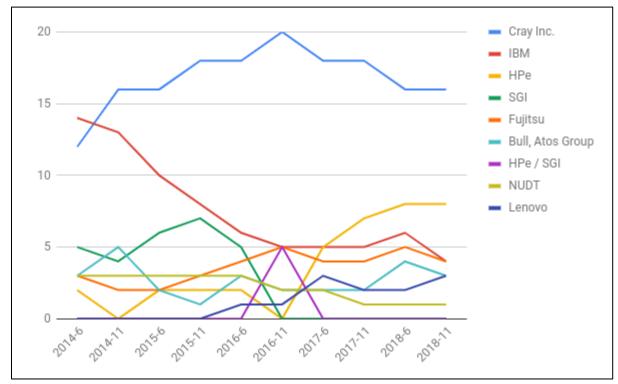

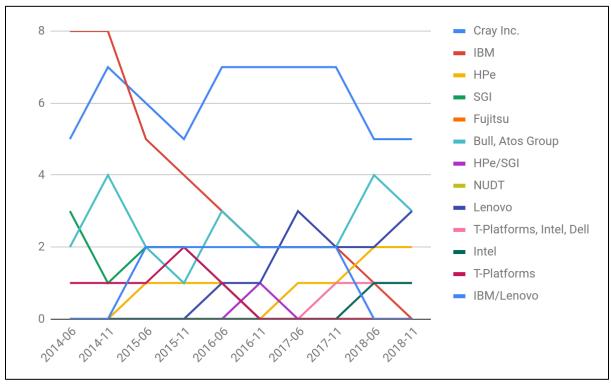

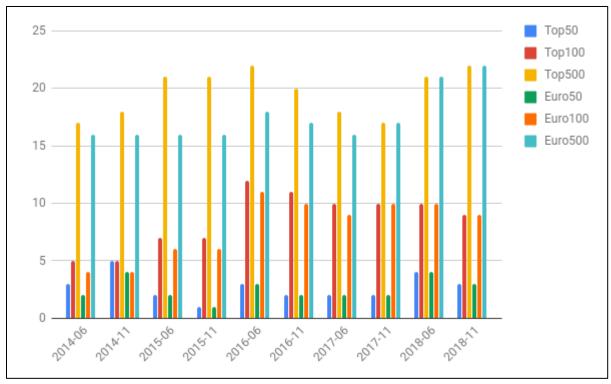

Table 1: Top10 systems in benchmark results for Top500/Green500/HPCG/IO500.