# E-Infrastructures H2020-EINFRA-2014-2015

# EINFRA-4-2014: Pan-European High Performance Computing Infrastructure and Services

# PRACE-4IP

# **PRACE Fourth Implementation Phase Project**

**Grant Agreement Number: EINFRA-653838**

# D5.1 Market and Technology Watch Report Year 1

#### Final

Version: 1.1

Author(s): Jean-Philippe Nominé, CEA

Date: 19.04.2016

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: EINFR                                                                              | Project Ref. №: EINFRA-653838      |  |

|---------------|----------------------------------------------------------------------------------------------------|------------------------------------|--|

|               | <b>Project Title: PRACE Fo</b>                                                                     | ourth Implementation Phase Project |  |

|               | <b>Project Web Site:</b> <a href="http://doi.org/10.2016/j.jpg/">http://doi.org/10.2016/j.jpg/</a> | ://www.prace-project.eu            |  |

|               | Deliverable ID: D5.1                                                                               |                                    |  |

|               | Deliverable Nature: Report                                                                         |                                    |  |

|               | <b>Dissemination Level:</b>                                                                        | Contractual Date of Delivery:      |  |

|               | Public                                                                                             | 30 / 04 / 2016                     |  |

|               |                                                                                                    | Actual Date of Delivery:           |  |

|               |                                                                                                    | 30 / 04/ 2016                      |  |

|               | <b>EC Project Officer: Leor</b>                                                                    | nardo Flores Añover                |  |

# **Document Control Sheet**

|            | Title: Market and Technology Watch Report Year 1 |                                        |  |  |

|------------|--------------------------------------------------|----------------------------------------|--|--|

| Document   | ID: D5.1                                         |                                        |  |  |

|            | Version: 1.1                                     | Status: Final                          |  |  |

|            | Available at: <a href="http://wv">http://wv</a>  | ilable at: http://www.prace-project.eu |  |  |

|            | <b>Software Tool:</b> Microso                    | ft Word 2010                           |  |  |

|            | <b>File(s):</b> D5.1.doc                         | ex                                     |  |  |

|            | Written by:                                      | Jean-Philippe Nominé, CEA              |  |  |

| Authorship | Contributors:                                    | Felip Moll, BSC                        |  |  |

| •          |                                                  | Oscar Yerpes, BSC                      |  |  |

|            |                                                  | Giannis Koutsou, CASTORC               |  |  |

|            |                                                  | Francois Robin, CEA                    |  |  |

|            |                                                  | Carlo Cavazzoni, CINECA                |  |  |

|            |                                                  | Olli-Pekka Lehto, CSC                  |  |  |

|            |                                                  | Dirk Pleiter, FZJ                      |  |  |

|            |                                                  | Michael Stephan, FZJ                   |  |  |

|            |                                                  | Eric Boyer, GENCI                      |  |  |

|            |                                                  | Philippe Segers, GENCI                 |  |  |

|            |                                                  | Ioannis Liabotis, GRNET                |  |  |

|            |                                                  | Dimitrios Dellis, GRNET                |  |  |

|            |                                                  | Nikolaos Nikoloutsakos, GRNET          |  |  |

|            |                                                  | Branislav Jansik, IT4I-VSB             |  |  |

|            |                                                  | Filip Stanek, IT4I-VSB                 |  |  |

|            |                                                  | Gert Svensson, KTH                     |  |  |

|            |                                                  | Andreas Johansson, LiU                 |  |  |

|            |                                                  | Michael Ott, BADW-LRZ                  |  |  |

|            |                                                  | Torsten Wilde, LRZ                     |  |  |

|            |                                                  | Radek Januszewski, PSNC                |  |  |

|            |                                                  | Norbert Meyer, PSNC                    |  |  |

|            | D : 11                                           | Huub Stoffers, SURFsara                |  |  |

|            | Reviewed by:                                     | Hank Nussbacher, IUCC                  |  |  |

|            |                                                  | Florian Berberich, JUELICH - PMO       |  |  |

|            | Approved by:                                     | MB/TB                                  |  |  |

#### **Document Status Sheet**

| Version | Date       | Status        | Comments                                         |  |

|---------|------------|---------------|--------------------------------------------------|--|

| 0.1     | 29/12/2016 | Draft outline | Detailed outline as agreed during Dec. 10,       |  |

|         |            |               | 2016, F2F meeting                                |  |

| 0.2     | 25/03/2016 | Partial draft | Inclusion of contributions received until        |  |

|         |            |               | March 20 <sup>th</sup>                           |  |

| 0.3     | 29/03/2016 | Draft         | First full inclusion of almost all contributions |  |

|         |            |               | (still missing a couple)                         |  |

| 0.4     | 01/04/2016 | Draft         | Misc. addenda (sections 2.3, 3.4, 4.1, chapter   |  |

|         |            |               | 6, draft conclusion)                             |  |

| 0.5     | 04/04/2016 | Draft         | Almost full version for finalisation telco of    |  |

|         |            |               | April 4 <sup>th</sup>                            |  |

| 0.6     | 04/04/2016 | Draft         | Editorial improvements of v0.5                   |  |

| 0.7     | 05/04/2016 | Draft         | Various corrections                              |  |

| 1.0     | 06/04/2916 | Final         | For internal PRACE review                        |  |

| 1.1     | 19/04/2016 | Final version | Corrected for MB/TP approval, from internal      |  |

|         |            |               | reviews                                          |  |

# **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure, Market Survey, Technology |

|------------------|----------------------------------------------------------------|

|                  | Watch                                                          |

#### Disclaimer

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° EINFRA-653838. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2016 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract EINFRA-653838 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

# **Table of Contents**

| Pro | ject a | and Deliverable Information Sheet              | i  |

|-----|--------|------------------------------------------------|----|

| Do  | cume   | ent Control Sheet                              | i  |

| Do  | cume   | ent Status Sheet                               | ii |

| Do  | cume   | ent Keywords                                   | ii |

|     |        | f Contents                                     |    |

|     |        | Figures                                        |    |

|     |        | Гables                                         |    |

|     |        | ces and Applicable Documents                   |    |

|     |        | Acronyms and Abbreviations                     |    |

|     |        | Project Partner Acronyms                       |    |

|     |        | ve Summary                                     |    |

| 1   |        | roduction                                      |    |

| 2   |        | orldwide HPC landscape and market overview     |    |

| 4   | 2.1    | A quick snapshot of HPC worldwide              |    |

|     | 4.1    | 2.1.1 Countries                                |    |

|     |        | 2.1.2 Accelerators.                            |    |

|     |        | 2.1.3 Age                                      |    |

|     |        | 2.1.4 Vendors                                  |    |

|     |        | 2.1.5 Computing efficiency                     |    |

|     |        | 2.1.6 Energy efficiency                        |    |

|     | 2.2    | Some more business analysis                    |    |

|     | 2.2    | 2.2.1 General impressions from SC'15           |    |

|     |        | 2.2.2 Market trends according to some analysts |    |

|     | 2.3    | Large initiatives world-wide                   |    |

|     | 2.0    | 2.3.1 US NSCI                                  |    |

|     |        | 2.3.2 Japan Post K and Flagship 2020.          |    |

|     |        | 2.3.3 China                                    |    |

|     |        | 2.3.4 Europe                                   |    |

| 3   | Cor    | re technologies and components                 |    |

| 3   |        | Processors                                     |    |

|     | 3.1    | 3.1.1 Intel x86                                |    |

|     |        | 3.1.2 AMD x86                                  |    |

|     |        | 3.1.2 AMD x00                                  |    |

|     |        | 3.1.4 POWER - OpenPOWER                        |    |

|     |        | 3.1.5 SPARC                                    |    |

|     |        | 3.1.6 FPGA                                     |    |

|     | 3.2    | Highly parallel components and compute engines |    |

|     | 3.2    | 3.2.1 Intel Xeon Phi                           |    |

|     |        | 3.2.2 NVIDIA GPUs                              |    |

|     |        | 3.2.3 PACS-G                                   |    |

|     | 3.3    |                                                |    |

|     | 5.5    | 3.3.1 DDR-SDRAM                                |    |

|     |        | 3.3.2 High-bandwidth memory technologies       |    |

|     |        | 3.3.3 Non-volatile memory technologies         |    |

|     |        | ,                                              |    |

|   | 3.4 | Interconnect                                                         | 37 |

|---|-----|----------------------------------------------------------------------|----|

|   |     | 3.4.1 Intel OmniPath & TrueScale                                     |    |

|   |     | 3.4.2 Ethernet                                                       |    |

|   |     | 3.4.3 Bull BXI                                                       | 41 |

|   |     | 3.4.4 <i>Infiniband</i>                                              | 44 |

|   |     | 3.4.5 <i>NUMAlink</i>                                                |    |

|   |     | 3.4.6 EXTOLL                                                         | 46 |

|   |     | 3.4.7 <i>Cray ARIES</i>                                              | 47 |

|   |     | 3.4.8 Fujitsu TOFU-2                                                 | 49 |

|   |     | 3.4.9 IBM BlueGene/Q                                                 | 50 |

|   |     | 3.4.10 <i>TH Express-2</i>                                           | 50 |

| 4 | Sol | utions and architectures                                             | 52 |

|   | 4.1 | Vendors overview                                                     | 52 |

|   |     | 4.1.1 <i>ATOS/Bull</i>                                               | 52 |

|   |     | 4.1.2 <i>Cray</i>                                                    | 53 |

|   |     | 4.1.3 Fujitsu                                                        | 53 |

|   |     | 4.1.4 <i>IBM</i>                                                     | 54 |

|   |     | 4.1.5 NEC                                                            | 55 |

|   |     | 4.1.6 <i>LENOVO</i>                                                  | 55 |

|   |     | 4.1.7 HPE                                                            | 56 |

|   |     | 4.1.8 <i>SGI</i>                                                     | 56 |

|   |     | 4.1.9 <i>D-WAVE</i>                                                  |    |

|   | 4.2 | Storage Organization for Exascale Computing Systems                  |    |

|   |     | 4.2.1 Reducing data movement.                                        |    |

|   |     | 4.2.2 Tiering Solution                                               |    |

|   | 4.3 | Trends in cooling systems                                            |    |

|   | 4.4 | Trends and return of experience in virtualisation and cloud delivery |    |

|   | 4.4 | 4.4.1 Cloud                                                          |    |

|   |     | 4.4.2 Containers                                                     |    |

| _ |     |                                                                      |    |

| 5 |     | nagement tools                                                       |    |

|   | 5.1 | System Monitoring                                                    |    |

|   |     | 5.1.1 <i>CACTI</i>                                                   |    |

|   |     | 5.1.2 OVIS                                                           |    |

|   |     | 5.1.3 Total Recall                                                   | 73 |

|   | 5.2 | User Level Tools                                                     | 74 |

|   |     | 5.2.1 XDMOD (XD Metrics on Demand)                                   | 74 |

|   |     | 5.2.2 LLview: User-level System Monitoring                           | 74 |

|   |     | 5.2.3 XALT                                                           |    |

|   |     | 5.2.4 REMORA                                                         | 75 |

|   | 5.3 | Energy Efficiency                                                    | 76 |

|   |     | 5.3.1 Redfish                                                        |    |

|   |     | 5.3.2 Power API                                                      |    |

|   | 5.4 | Next-generation monitoring and log analytics – CSC's Experience      | 76 |

|   |     | 5.4.1 Monitoring                                                     |    |

|   |     | 5.4.2 Log analytics                                                  |    |

|   |     | 5.4.3 Experiences                                                    |    |

|   |     | 5.4.4 Other resources                                                |    |

|   | 5.5 | CINECA Dashboard – a single pane of glass for all data sources       |    |

| 6 | EH  | Projects for Exascale and Big Data                                   |    |

| J | 6.1 | FP7                                                                  |    |

|   |     | H2020 – FETHPC                                                       |    |

|   | U.4 | 11#V#V - I' I' 1 111 \(\cdots\)                                      |    |

| 6.3 | Centres of Excellence for Computing Applications                           | 8  |

|-----|----------------------------------------------------------------------------|----|

| 6.4 | Coordination and support actions: EXDCI and Eurolab4HPC - NESUS            | 8  |

|     | 6.4.1 EXDCI                                                                | 8  |

|     | 6.4.2 Eurolab4HPC                                                          | 8  |

|     | 6.4.3 <i>NESUS</i>                                                         | 8  |

| 6.5 | Others HPC technology R&D projects: ITEA programmes                        | 8  |

| 6.6 | Pre-Commercial Procurements (PRACE, HBP)                                   | 9  |

|     | 6.6.1 <i>PRACE</i>                                                         | 9  |

|     | 6.6.2 Human Brain Project                                                  | 90 |

| Con | ıclusion                                                                   | 92 |

| Anr | nex                                                                        | 93 |

|     | Summaries of 19 FETHPC projects (Work Programme 2014-2015 of Horizon 2020) |    |

# **List of Figures**

| Figure 1: evolution of the fraction of cumulated RMAX overtime for top HPC countries          | 4  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2: evolution of the fraction of cumulated RMAX overtime for top HPC countries / Europe | 5  |

| Figure 3: Top 10/20/50 systems in Europe                                                      | 6  |

| Figure 3: Fraction of systems with accelerators                                               | 7  |

| Figure 4: Average age of systems                                                              | 8  |

| Figure 5: Top500 vendors                                                                      |    |

| Figure 6: Top500 European vendor                                                              |    |

| Figure 7: HPL vs. HPCG efficiency comparison                                                  |    |

| Figure 8: Energy efficiency in Top10/50 (Top500 and Green500 references)                      |    |

| Figure 9: AMD Zen compared with the previous generation Excavator architecture                |    |

| Figure 10: AMD A1000 series processor models                                                  |    |

| Figure 11: AMD A1000 series architecture                                                      |    |

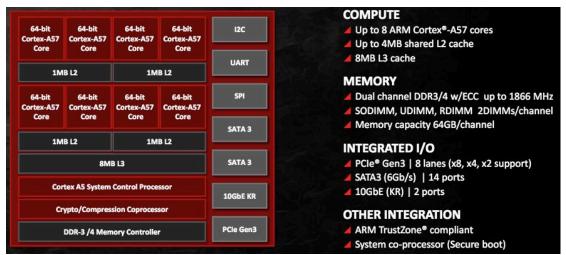

| Figure 12: APM X-Gene Roadmap                                                                 |    |

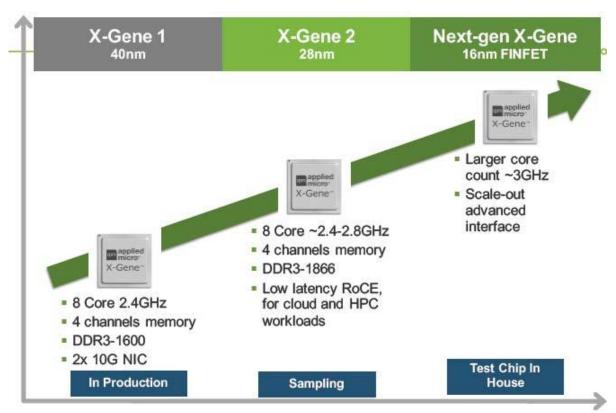

| Figure 13: ThunderX high-level CPU architecture                                               |    |

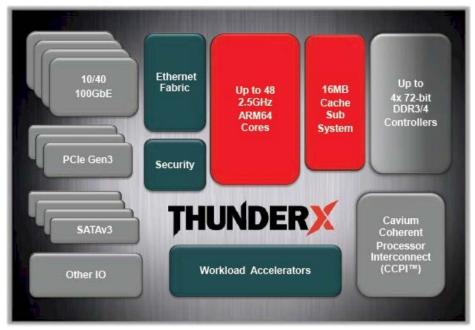

| Figure 14: Intel KNL overview                                                                 |    |

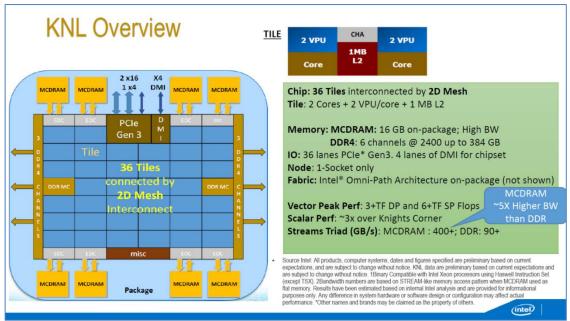

| Figure 15: High Level picture of Knight Landing package                                       |    |

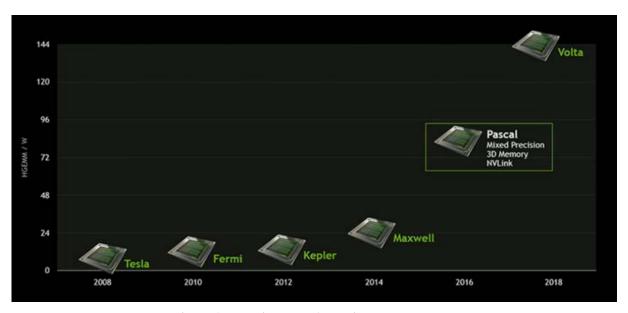

| Figure 16: Public NVIDIA architecture roadmap.                                                |    |

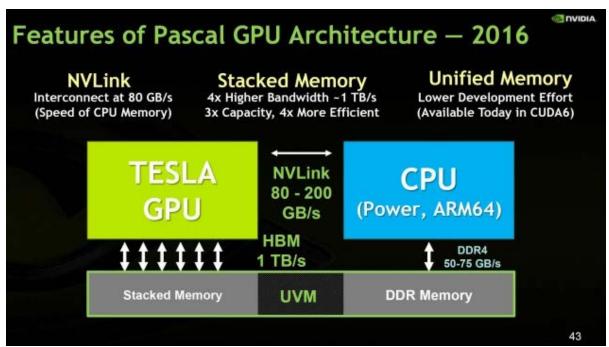

| Figure 17: NVIDIA Pascal architecture                                                         |    |

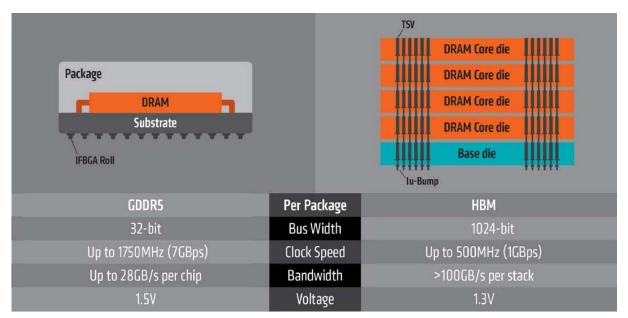

| Figure 18: Main characteristics of high bandwidth 3D stacked memory for Pascal                |    |

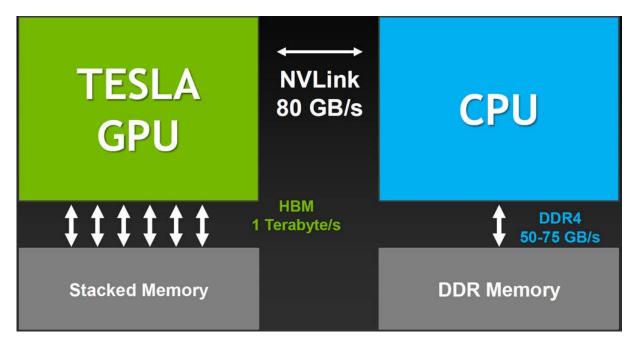

| Figure 19: High level scheme of NVLink as used in the future IBM Power node                   |    |

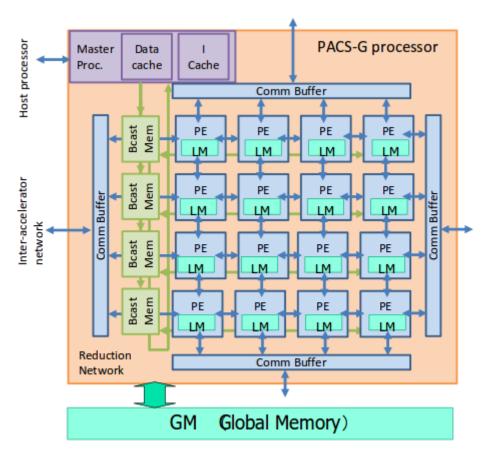

| Figure 20: PACS-G processor                                                                   |    |

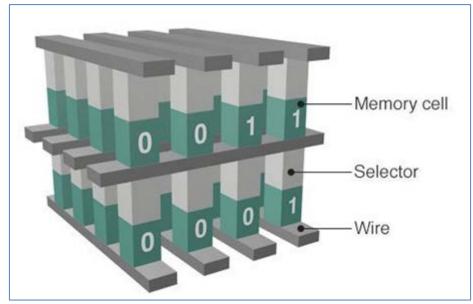

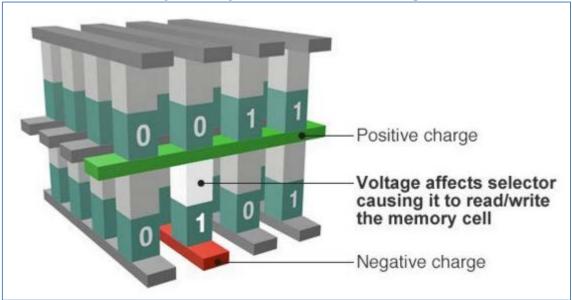

| Figure 21: High level scheme of 3D XPoint chip                                                |    |

| Figure 22: High level representation of memory cell selection process                         |    |

| Figure 23: Future API towards non-volatile memory enabling direct load/store operations [61]  |    |

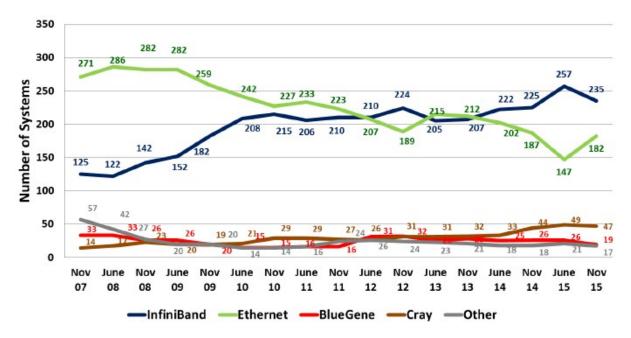

| Figure 24: Trends of interconnect families (TOP500)                                           |    |

|                                                                                               |    |

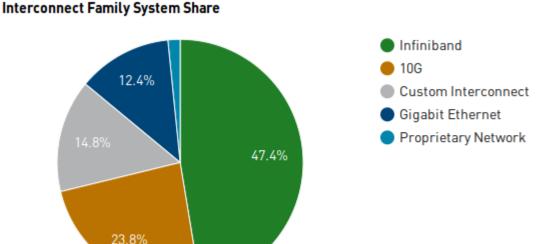

| Figure 25: TOP500 list (November 2015) Interconnect family market share by systems            |    |

| Figure 26: Intel OPA portfolio overview                                                       |    |

|                                                                                               |    |

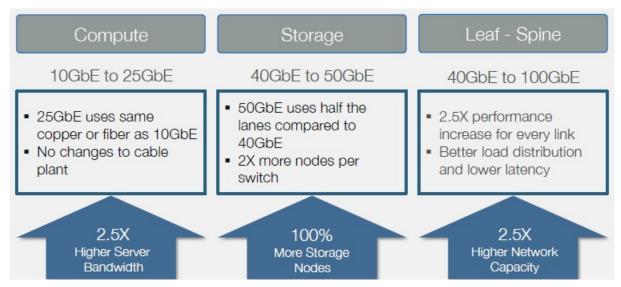

| Figure 28: Mellanox Ethernet Switches portfolio                                               |    |

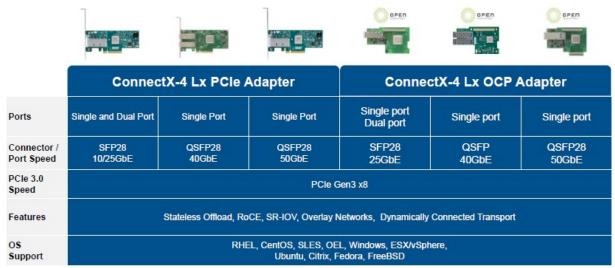

| Figure 29: Mellanox Ethernet NIC overview                                                     |    |

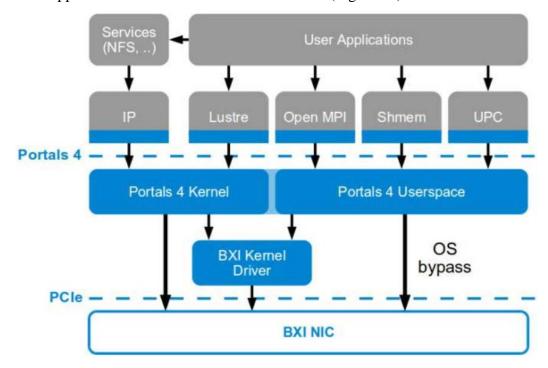

| Figure 30: BXI software stack                                                                 |    |

| Figure 31: BXI NIC block diagram                                                              |    |

| Figure 32: Mellanox future vision of intelligent network                                      |    |

| Figure 33: NUMAlink single IRU topology                                                       |    |

| Figure 34: NUMAlink topology with 4 IRUs                                                      |    |

| Figure 35: TOURMALET block diagram                                                            |    |

| Figure 36: Custom Active Optical Cable from Extoll                                            |    |

| Figure 37: Aries system-on-a-chip device                                                      |    |

| Figure 38: ARIES SW stack overview                                                            |    |

| Figure 39: TOFU-2 vs. TOFU-1 architecture                                                     |    |

| Figure 40: TH Express-2 NIC block diagram                                                     |    |

| Figure 41: Bull Sequana cell                                                                  | 53 |

| Figure 42: Fujitsu density-optimized PRIMERGY CX chassis                                      |    |

| Figure 43: IBM Firestone server [90]                                                          | 55 |

| Figure 44: exascale I/O challenges                                                            | 59 |

| Figure 45: SGI Zero Copy Architecture                                                         | 60 |

| Figure 46: SGI Zero Copy Architecture                                                         | 60 |

| Figure 47: Data appear local, even if it's not                                                | 61 |

| Figure 48: SAGE tiering layout                                                                | 61 |

| Figure 49: Tiering usage in HPC facilities                                                    |    |

| Figure 50: left - IME typical peak provisioning / right - DDN Infinite Memory Engine          |    |

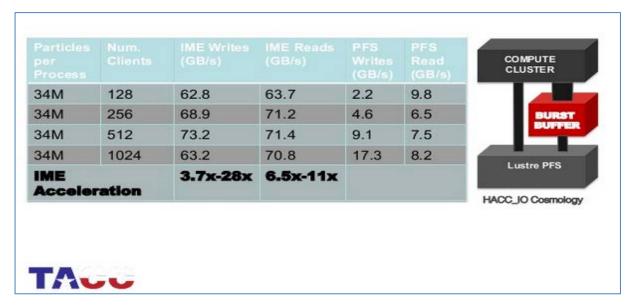

| Figure 51: Acceleration by IME – Cosmology application at TACC                                |    |

| Figure 52: Seagate CL300 Small block accelerator                                              |    |

| <del>-</del>                                                                                  |    |

| Figure 53: A Grafana dashboard to monitor cPouta capacity and performance                  | 67 |

|--------------------------------------------------------------------------------------------|----|

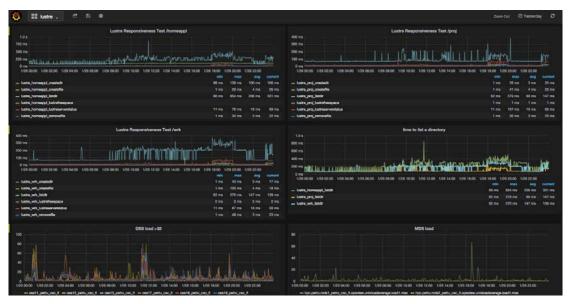

| Figure 54: Example screenshot from Grafana of Lustre load monitoring                       | 77 |

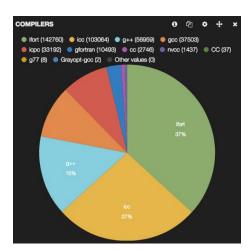

| Figure 55: Compiler invocation counts from CSC's Taito cluster frontends using ELK         | 78 |

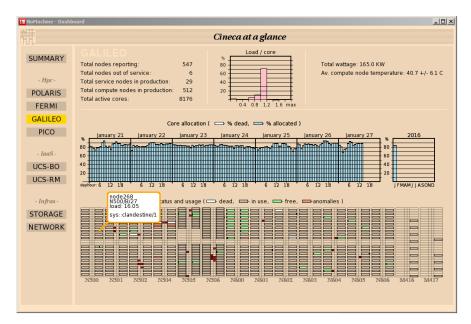

| Figure 56: A sample view of the current dashboard application                              | 80 |

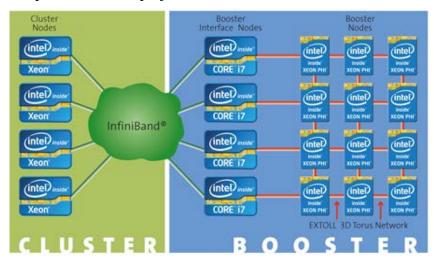

| Figure 57: DEEP hardware architecture                                                      | 81 |

| Figure 58: H2020 HPC projects (FETHPC and CoEs)                                            | 84 |

|                                                                                            |    |

|                                                                                            |    |

| List of Tables                                                                             |    |

| Table 1: countries for Top50 analysis                                                      | 3  |

| Table 2: Social and scientific priority issues to be tackled by using Post K computer      | 15 |

| Table 3: TrueScale and OPA edge switch comparison                                          | 38 |

| Table 4: Price comparison of selected interconnects                                        | 40 |

| Table 5: FETHPC 1-2015 H2020 call topic                                                    |    |

| Table 6: FETHPC 1-2015 H2020 call topic                                                    | 83 |

| Table 7: Architecture and Compute topics of EU HPC projects                                | 85 |

| Table 8: Interconnect, Memory & Storage Data-Intensive Real Time topics of EU HPC projects | 86 |

| Table 9: Programming Models, Algorithms and Mathematics topics of EU HP projects           | 87 |

| Table 10: ITEA HPC projects                                                                | 90 |

# **References and Applicable Documents**

- [1] PRACE: <a href="http://www.prace-project.eu">http://www.prace-project.eu</a>

- [2] Top 500: <u>www.top500.org/</u>

- [3] Green 5000: http://www.green500.org/

- [4] HPCG Benchmark: http://hpcg-benchmark.org/

- [5] HPL Benchmark: <a href="http://www.top500.org/project/linpack/">http://www.top500.org/project/linpack/</a>

- [6] <a href="http://www.hpcwire.com/2015/11/18/sugon-vp-on-global-market-strategy-the-vmware-venture-and-robotic-immersive-cooling/">http://www.hpcwire.com/2015/11/18/sugon-vp-on-global-market-strategy-the-vmware-venture-and-robotic-immersive-cooling/</a>

- [7] <a href="http://www.hpcwire.com/2016/03/11/idc-server-report-china-leads-growth-ibm-power-strengthens-arm-stumbles/">http://www.hpcwire.com/2016/03/11/idc-server-report-china-leads-growth-ibm-power-strengthens-arm-stumbles/</a>

- [8] <a href="http://www.idc.com/getdoc.jsp?containerId=prUS41076116">http://www.idc.com/getdoc.jsp?containerId=prUS41076116</a>

- [9] <a href="http://www.marketsandmarkets.com/PressReleases/Quantum-High-Performance-Computing.asp">http://www.marketsandmarkets.com/PressReleases/Quantum-High-Performance-Computing.asp</a>

- [10] <a href="http://hpcadvisorycouncil.com/events/2016/stanford-workshop/pdf/Snell.2016TrendsHPCandHyperscale.Intersect360Rsrch.pdf">http://hpcadvisorycouncil.com/events/2016/stanford-workshop/pdf/Snell.2016TrendsHPCandHyperscale.Intersect360Rsrch.pdf</a>

- [11] <a href="http://www.marketsandmarkets.com/Market-Reports/Quantum-High-Performance-Computing-Market-631.html?gclid=CNDg0cmf5ssCFZcy0wodeT8OVw">http://www.marketsandmarkets.com/Market-Reports/Quantum-High-Performance-Computing-Market-631.html?gclid=CNDg0cmf5ssCFZcy0wodeT8OVw</a>

- [12] <a href="https://www.whitehouse.gov/the-press-office/2015/07/29/executive-order-creating-national-strategic-computing-initiative">https://www.whitehouse.gov/the-press-office/2015/07/29/executive-order-creating-national-strategic-computing-initiative</a>

- [13] <a href="http://energy.gov/articles/department-energy-awards-425-million-next-generation-supercomputing-technologies">http://energy.gov/articles/department-energy-awards-425-million-next-generation-supercomputing-technologies</a>

- [14] http://www.hpcwire.com/2016/02/10/final-obama-budget-fy17/

- [15] https://asc.llnl.gov/CORAL/

- [16] http://www.theregister.co.uk/2015/04/10/us\_intel\_china\_ban/

- [17] http://www.scientific-computing.com/features/feature.php?feature\_id=467

- [18] IDC Report SMART 2014/0021 "High Performance Computing in the EU: Progress on the Implementation of the European HPC Strategy" http://ec.europa.eu/newsroom/dae/document.cfm?doc\_id=10334

- [19] <a href="http://www.hpcwire.com/off-the-wire/riken-selects-fujitsu-develop-new-supercomputer/">http://www.hpcwire.com/off-the-wire/riken-selects-fujitsu-develop-new-supercomputer/</a>

- [20] http://www.aics.riken.jp/en/postk/outcome

- [21] Japan Concludes Exascale Feasibility Study: http://www.hpcwire.com/2014/12/03/japan-concludes-exascale-feasibility-study/

- [22] Japan Preps for HPC-Big Data Convergence: http://www.hpcwire.com/2015/06/18/japan-preps-for-hpc-big-data-convergence/

- [23] <a href="https://ec.europa.eu/programmes/horizon2020/en/h2020-section/high-performance-computing-hpc">https://ec.europa.eu/programmes/horizon2020/en/h2020-section/high-performance-computing-hpc</a>

- [24] <a href="http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2</a>

<a href="https://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/topics/2">https://ec.eu/research/participants/participants/participants/participants/participants/participants/participants/participants/participants/participants/participants/participants/participants/participants/participan

- [25] <a href="http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/calls/h2020-fethpc-2016-2017.html">http://ec.europa.eu/research/participants/portal/desktop/en/opportunities/h2020/calls/h2020-fethpc-2016-2017.html</a>

- [26] <a href="http://ec.europa.eu/research/participants/data/ref/h2020/wp/2016\_2017/main/h2020-wp1617-fet\_en.pdf">http://ec.europa.eu/research/participants/data/ref/h2020/wp/2016\_2017/main/h2020-wp1617-fet\_en.pdf</a>

- [27] SRA <a href="http://www.etp4hpc.eu/en/sra.html">http://www.etp4hpc.eu/en/sra.html</a>

- [28] ETP4HPC <a href="http://www.etp4hpc.eu/">http://www.etp4hpc.eu/</a>

- [29] ETP4HPC members http://www.etp4hpc.eu/en/membership.html

- [30] EXDCI <a href="https://exdci.eu/">https://exdci.eu/</a>

- [31] <a href="https://exdci.eu/events/european-hpc-summit-week">https://exdci.eu/events/european-hpc-summit-week</a>

- [32] http://www.etp4hpc.eu/en/news/25-exdci-workshop-in-rome-september9-and0.html

- [33] <a href="https://ec.europa.eu/digital-single-market/en/news/study-high-performance-computing-eu-progress-implementation-european-hpc-strategy-final-report">https://ec.europa.eu/digital-single-market/en/news/study-high-performance-computing-eu-progress-implementation-european-hpc-strategy-final-report</a>

- [34] <a href="https://ec.europa.eu/digital-single-market/en/news/communication-high-performance-computing-hpc-europes-place-global-race">https://ec.europa.eu/digital-single-market/en/news/communication-high-performance-computing-hpc-europes-place-global-race</a>

- [35] <a href="https://ec.europa.eu/research/openscience/index.cfm?pg=open-science-cloud">https://ec.europa.eu/research/openscience/index.cfm?pg=open-science-cloud</a>

- [36] http://knowledgebase.e-irg.eu/documents/243153/299805/IPCEI-HPC-BDA.pdf

- $[37] \ \ \frac{http://www.ccs.tsukuba.ac.jp/eng/wordpress/wp-content/uploads/2014/04/CCS-MitsuhisaSato.pdf}$

- [38] Tom R. Halfhill, "POWER8 hits the merchant market," The Linley Group, Microprocessor Report, December 2014.

- [39] E. J. Fluhr et al., "POWER8: A 12-core server-class processor in 22nm SOI with 7.6Tb/s off-chip bandwidth," ISSCC 2014, doi:10.1109/ISSCC.2014.6757353.

- [40] http://openpowerfoundation.org/ (accessed 19.03.2016)

- [41] https://www-03.ibm.com/press/us/en/pressrelease/42980.wss (accessed 19.03.2016)

- [42] <a href="http://openpowerfoundation.org/wp-content/uploads/2015/03/Ashley-John\_OPFS2015\_NVIDIA\_031215.pdf">http://openpowerfoundation.org/wp-content/uploads/2015/03/Ashley-John\_OPFS2015\_NVIDIA\_031215.pdf</a> (accessed 19.03.2016)

- [43] <a href="http://www.nallatech.com/wp-content/uploads/IBM\_CAPI\_Users\_Guide.pdf">http://www.nallatech.com/wp-content/uploads/IBM\_CAPI\_Users\_Guide.pdf</a> (accessed 19.03.2016)

- [44] <a href="http://openpowerfoundation.org/blogs/interconnect-your-future-mellanox-100gb-edr-capi-infiniband-and-interconnects/">http://openpowerfoundation.org/blogs/interconnect-your-future-mellanox-100gb-edr-capi-infiniband-and-interconnects/</a> (accessed 19.03.2016)

- [45] <a href="http://on-demand.gputechconf.com/gtc/2015/presentation/S5786-Tjerk-Straatsma.pdf">http://on-demand.gputechconf.com/gtc/2015/presentation/S5786-Tjerk-Straatsma.pdf</a> (accessed 19.03.2016)

- [46] <a href="https://software.intel.com/en-us/articles/what-disclosures-has-intel-made-about-knights-landing">https://software.intel.com/en-us/articles/what-disclosures-has-intel-made-about-knights-landing</a>

- [47] http://www.bull.com/tera-1000-cea-completes-first-milestone-towards-exascale

- [48] <a href="http://www.hardwareluxx.com/index.php/news/hardware/memory/36373-idf-2015-ddr4-roadmap-for-2015-2016.html">http://www.hardwareluxx.com/index.php/news/hardware/memory/36373-idf-2015-ddr4-roadmap-for-2015-2016.html</a> (accessed 20.03.2016)

- [49] <a href="https://www.skhynix.com/products.do?ct1=36&ct2=44&lang=eng">https://www.skhynix.com/products.do?ct1=36&ct2=44&lang=eng</a> (accessed 20.03.2016)

- [50] <a href="http://www.hybridmemorycube.org">http://www.hybridmemorycube.org</a> (accessed 20.03.2016)

- [51] Toshio Yoshida, "SPARC64TM Xifx: Fujitsu's Next Generation Processor for HPC," HotChips 2014, <a href="https://www.fujitsu.com/hk/Images/20140811hotchips26.pdf">https://www.fujitsu.com/hk/Images/20140811hotchips26.pdf</a> (accessed 20.03.2016)

- [52] <a href="https://www.altera.com/en\_US/pdfs/literature/ug/ug\_hmcc.pdf">https://www.altera.com/en\_US/pdfs/literature/ug/ug\_hmcc.pdf</a> (accessed 20.03.2016)

- [53] <a href="https://www.micron.com/about/blogs/2016/february/gddr5x-has-arrived">https://www.micron.com/about/blogs/2016/february/gddr5x-has-arrived</a>

- [54] https://www.jedec.org/standards-documents/results/GDDR5X (access 26.03.2016)

- [55] M. Webb, "Alternative Non-Volatile Memory Adoption Timeline," FlashMemory Summit 2015.

- [56] R. Davis, "NVMe over Fabrics: Learning from early developments, "FlashMemory Summit 2015.

- [57] http://www.ddn.com/products/infinite-memory-engine-ime14k/

- [58] http://www.crav.com/products/storage/datawarp

- [59] J. Handy, "Flash Technology: Annual Update," FlashMemory Summit 2015.

- [60] J. Pappas, "Annual Update on Interfaces," FlashMemory Summit 2015.

- [61] SNIA, "NVM Programming Model (NPM) Version 1.1," March 2015.

- [62] D. Voigt, "Programming for Non-Volatile Memory," FlashMemory Summit 2015.

- [63] JDEC, "High Bandwidth Memory (HBM) DRAM," JESD235A, November 2015

- (http://www.jedec.org/standards-documents/docs/jesd235a

- [64] http://top500.org/statistics/list/

- [65] <a href="http://www.nextplatform.com/2015/11/16/intel-rounds-out-scalable-systems-with-omni-path/">http://www.nextplatform.com/2015/11/16/intel-rounds-out-scalable-systems-with-omni-path/</a>

- [66] <a href="http://www.nextplatform.com/2015/09/14/arista-wields-tomahawks-in-25g-ethernet-price-war/">http://www.nextplatform.com/2015/09/14/arista-wields-tomahawks-in-25g-ethernet-price-war/</a>

- [67] Christelle Piechurski, BULL, BULL Booth, SC15, November 2015

- [68] <a href="http://www.hoti.org/hoti23/slides/derraji.pdf">http://www.hoti.org/hoti23/slides/derraji.pdf</a>

- [69] Saïd Derradji, Thibaut Palfer-Sollier, Jean-Pierre Panziera, Axel Poudes, François Wellenreiter, The BXI Interconnect architecture, paper sent to the author

- [70] Gilad Shainer, Mellanox, Conversation with Author, SC15, November 2015

- [71] <a href="http://www.mellanox.com/page/products\_dyn?product\_family=227&mtag=switch\_ib2\_ic">http://www.mellanox.com/page/products\_dyn?product\_family=227&mtag=switch\_ib2\_ic</a>

- [72] https://www.sgi.com/pdfs/4192.pdf

- [73] Ulrich Krackhardt, Extoll, Extoll Booth, SC15, November 2015

- [74] <a href="http://extoll.de/products/tourmalet">http://extoll.de/products/tourmalet</a>

- [75] Wilfried Oed, CRAY, Conversation with Author, SC15, November 2015

- [76] <a href="http://www.cray.com/sites/default/files/resources/CrayXCNetwork.pdf">http://www.cray.com/sites/default/files/resources/CrayXCNetwork.pdf</a>

- [77] http://www.fujitsu.com/global/Images/tofu-interconnect2\_tcm100-1055326.pdf

- [78] <a href="https://www.olcf.ornl.gov/summit/">https://www.olcf.ornl.gov/summit/</a>

- [79] http://link.springer.com/article/10.1007%2Fs11704-014-3500-9#/page-1

- [80] http://www.bull.com/

- [81] <a href="http://atos.net/en-us/home/we-are/news/press-release/2015/pr-2015\_11\_12\_01.html">http://atos.net/en-us/home/we-are/news/press-release/2015/pr-2015\_11\_12\_01.html</a>

- [82] http://www.bull.com/sequana

- [83] http://www.scientific-computing.com/news/news story.php?news id=2719

- [84] Technical Advances in the SGI UV Architecture, 2012 https://www.sgi.com/pdfs/4192.pdf

- [85] SGI product portfolio, https://www.sgi.com/products/servers/, retrieved March 2016

- [86] Private correspondence between the Author and the SGI, 2015-2016.

- [87] http://www.fujitsu.com/primergy (accessed 29.03.2016)

- [88] http://docs.ts.fujitsu.com/dl.aspx?id=c0e740df-f6a3-4e5b-ae78-fd6567bade6c (accessed 29.03.2016)

- [89] https://www.fujitsu.com/global/Images/key-hardware-technologies-for-the-next-generation-primehpc-post-fx10.pdf (accessed 29.03.2016)

- [90] A. Caldeira et al., "IBM Power Systems S822LC Technical Overview and Introduction," IBM Redpaper publication, 20

- [91] <a href="http://www.openstack.org">http://www.openstack.org</a>

- [92] <a href="http://www.rdoproject.org">http://www.rdoproject.org</a>

- [93] https://wiki.openstack.org/wiki/Packstack

- [94] https://wiki.openstack.org/wiki/Neutron/DVR.

- [95] https://research.csc.fi/taito-supercluster

- [96] <a href="http://www.docker.com">http://www.docker.com</a>

- [97] <a href="https://www.ibm.com/developerworks/community/blogs/hpcgoulash/entry/a\_whale\_of\_a\_time?lang=en">https://www.ibm.com/developerworks/community/blogs/hpcgoulash/entry/a\_whale\_of\_a\_time?lang=en</a>

- [98] <a href="http://www.isc-events.com/isc15\_ap/sessiondetails.htm?t=session&o=227&a=select">http://www.isc-events.com/isc15\_ap/sessiondetails.htm?t=session&o=227&a=select</a>

- [99] http://investors.cray.com/phoenix.zhtml?c=98390&p=irol-newsArticle&ID=2112970

- [100] https://www.nersc.gov/research-and-development/user-defined-images/

- [101] http://www.lanl.gov/projects/apex/schedule.php

- [102] Cacti®, "The Complete RRDTool-based Graphing Solution". 2004. 18 Jan. 2016 <a href="http://www.cacti.net/">http://www.cacti.net/</a>

- [103] <a href="http://oss.oetiker.ch/rrdtool/">http://oss.oetiker.ch/rrdtool/</a>

- [104] Ovis, "Sandia National Laboratories". 2007. 18 Jan. 2016 https://ovis.ca.sandia.gov/

- [105] Birngruber, E., "Total recall: holistic metrics for broad systems performance" 2015. http://dl.acm.org/citation.cfm?id=2835001

- [106] "XDMoD Portal. 2011". 18 Jan. 2016 <a href="https://xdmod.ccr.buffalo.edu/">https://xdmod.ccr.buffalo.edu/</a>

- [107] Forschungszentrum Jülich JSC "Components of LLview". 2013. 18 Jan. 2016 http://www.fz-juelich.de/ias/jsc/EN/Expertise/Support/Software/LLview/llview-components\_node.html

- [108] "XALT" Texas Advanced Computing Center. 2015. 18 Jan. 2016 https://www.tacc.utexas.edu/research-development/tacc-projects/xalt

- [109] Rosales, C., "Remora: A Resource Monitoring Tool for Everyone..." 2015. http://hust15.github.io/files/HUST15-Rosales-Remora-Slides.pdf

- [110] "Redfish Resource Explorer". 2015. 18 Jan. 2016 http://redfish.dmtf.org/

- [111] PowerAPI: Sandia National Laboratories". 2014. 18 Jan. 2016 http://powerapi.sandia.gov/

- [112] Laros III, James H et al., "High Performance Computing-Power Application Programming Interface Specification Version 1.0". - *Sandia National Laboratories*, *Tech. Rep. SAND2014-17061* (2014)

- [113] https://collectd.org/

- [114] http://graphite.wikidot.com/

- [115] http://grafana.org/

- [116] http://graphite.readthedocs.org/en/latest/tools.html

- [117] https://www.elastic.co/products

- [118] http://www.nersc.gov/research-and-development/apex/

- [119] https://www.hepix.org/

- [120] http://qnib.org/2015/10/29/melig-2/

- [121] PRACE 2IP deliverable D5.2, "Updated Best Practices for HPC Procurement and Infrastructure" August 2014

- [122] http://exascale-projects.eu/ an overview on FP7 funded projects

- [123] http://www.deep-project.eu/deep-project/

- [124] http://www.deep-er.eu

- [125] http://www.scientificcomputing.com/news/2015/07/booster-system-installed-j%C3%BClich-completes-deep-supercomputer

- [126] http://www.montblanc-project.eu/

- [127] http://cresta-project.eu

- [128] http://www.epigram-project.eu/

- [129] https://projects.imec.be/exa2ct/

- [130] http://www.numexas.eu/

- [131] <u>https://ec.europa.eu/programmes/horizon2020/en/news/21-new-h2020-high-performance-computing-projects</u>

- [133] http://www.etp4hpc.eu/en/euexascale.html

- [134] <u>https://ec.europa.eu/programmes/horizon2020/en/news/eight-new-centres-excellence-computing-applications</u>

- [135] https://exdci.eu/

- [136] http://www.eurolab4hpc.eu/

- [137] http://www.nesus.eu/

- [138] https://itea3.org/all-projects/page-all.html

- [139] http://ec.europa.eu/digital-agenda/en/pre-commercial-procurement

- [140] https://www.humanbrainproject.eu/

- $[141] \underline{\text{http://ec.europa.eu/research/participants/data/ref/h2020/other/wp/2016\_2017/annexes/h2020} \\ -\underline{\text{wp1617-annex-g-trl\_en.pdf}}$

- [142] http://www.prace-ri.eu/ueabs/

- [143] http://www.sage-project.eu/home.html

- [144] https://www.tacc.utexas.edu/

- [145] <u>http://wccftech.com/nvidia-pascal-nvlink-200-gbs-interconnect-hbm2-stacked-memory-1-tbs-bandwidth-powering-hpc-2016</u>

# **List of Acronyms and Abbreviations**

aisbl Association Internationale Sans But Lucratif

(legal form of the PRACE-RI)

BXI Bull eXascale Interconnect

CoE Center of Excellence (for Computing Applications)

CORAL Joint Collaboration of Oak Ridge, Argonne, and Lawrence Livermore

**US HPC Centers**

CPU Central Processing Unit

cPPP contractual Public Private Partnership

CSA Coordination and Support Actions (type of Horizon 2020 project)

CUDA Compute Unified Device Architecture (NVIDIA)

DARPA Defense Advanced Research Projects Agency

DP Double Precision Floating point (usually in 64-bit)

DSM Digital Single Market EC European Commission

EU European Union

EFlop/s Exaflop/s Exa (= 10<sup>18</sup>) Floating point operations (usually in DP) per

second, also EF/s

EXDCI European Extreme Data & Computing Initiative

FETHPC HPC programme of H2020 Future and Emerging Technologies branch

7<sup>th</sup> Framework Programme for Research and Technological

Development of the European Union (Research and Innovation funding

programme for 2007-2013.)

FGPA Field Programmable Gate Array

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GFlop/s Giga (= 10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also GF/s

GHz Giga (=  $10^9$ ) Hertz, frequency =  $10^9$  periods or clock cycles per second

GPU Graphic Processing Unit

H2020 The EU Framework Programme for Research and Innovation 2014-

2020

HBP Human Brain Project

HPC High Performance Computing; Computing at a high performance level

at any given time; often used synonym with Supercomputing

HPCG High Performance Conjugate Gradient – a benchmark developed as

complement or alternative to HPL

HPDA High Performance Data Analytics

HPL High Performance LINPACK benchmark (used for Top500 ranking)

IPCEI Important Project of Common European Interest

ISC International Supercomputing Conference; European equivalent to the

US based SCxx conference. Held annually in Germany.

KB Kilo (=  $2^{10} \sim 10^3$ ) Bytes (= 8 bits), also KByte

KNC Knights Corner, Intel® MIC Xeon® Phi™ processors (first generation)

KNF Knights Ferry, Intel® MIC Xeon® Phi<sup>™</sup> processors (prototype)

KNL Knights Landing, Intel® MIC Xeon® Phi™ processors (second

generation)

LINPACK Software library for Linear Algebra

MB Management Board (highest decision making body of the project)

MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (= 10<sup>6</sup>) Bytes (= 8 bits) per second, also MByte/s

MFlop/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also MF/s

MIC Intel Many Integrated Core Processor Architecture

MPI Message Passing Interface

NDA Non-Disclosure Agreement. Typically signed between vendors and

customers working together on products prior to their general

availability or announcement.

NSCI US President Executive Order establishing the National Strategic

Computing Initiative

OPA Omni Path technology

PCP Pre-Commercial Procurement

PFlop/s Peta (= 10<sup>15</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second. also PF/s.

PRACE Partnership for Advanced Computing in Europe; Project Acronym

RI Research Infrastructure

RIA Research and Innovation Action (type of H2020 project)

R<sub>max</sub> Top500 system measured (LINPACK) maximum performance

R<sub>peak</sub> Top500 system theoretical maximum performance

SC Supercomputing Conference; US equivalent to the European based ISC

conference. Held annually in U.S.

SKU Stock Keeping Unit SoC System on a Chip

SRA Strategic Research Agenda

TB Technical Board (group of Work Package leaders) TB Tera (=  $2^{40} \sim 10^{12}$ ) Bytes (= 8 bits), also TByte

TCO Total Cost of Ownership. Includes recurring costs (e.g. personnel,

power, cooling, maintenance) in addition to the purchase cost.

TFlop/s Tera (=  $10^{12}$ ) Floating-point operations (usually in 64-bit, i.e. DP) per

second, also TF/s

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the Tier-0 systems; national or topical HPC centres would constitute Tier-1

# **List of Project Partner Acronyms**

BADW-LRZ Leibniz-Rechenzentrum der Bayerischen Akademie der

Wissenschaften, Germany (3<sup>rd</sup> Party to GCS)

BSC Barcelona Supercomputing Center - Centro Nacional de

Supercomputacion, Spain

CaSToRC Computation-based Science and Technology Research Center,

Cyprus

CEA Commissariat à l'Energie Atomique et aux Energies Alternatives.

France (3<sup>rd</sup> Party to GENCI)

CINECA CINECA Consorzio Interuniversitario, Italy

CSC CSC Scientific Computing Ltd., Finland

EPCC at The University of Edinburgh, UK

GCS Gauss Centre for Supercomputing e.V.

GENCI Grand Equipement National de Calcul Intensiv, France GRNET Greek Research and Technology Network, Greece

IT4I IT4Innovations National Supercomputing Center of VSB-TUO

IUCC Inter University Computation Centre, Israel JUELICH Forschungszentrum Juelich GmbH, Germany

KTH Royal Institute of Technology, Sweden (3 rd Party to SNIC)

LiU Linkoping University, Sweden (3 rd Party to SNIC)

NIIF National Information Infrastructure Development Institute,

Hungary

PRACE Partnership for Advanced Computing in Europe aisbl, Belgium PSNC Poznan Supercomputing and Networking Center, Poland

SNIC Swedish National Infrastructure for Computing (within the

Swedish Science Council), Sweden

SURFsara Dutch national high-performance computing and e-Science

support center, part of the SURF cooperative, Netherlands

USTUTT-HLRS Universitaet Stuttgart – HLRS, Germany (3<sup>rd</sup> Party to GCS)

VSB-TUO Vysoka Skola Banska - Technicka Univerzita Ostrava, Czech

Republic

# **Executive Summary**

The PRACE-4IP Work Package 5 (WP5), "Best Practices for HPC Systems Commissioning", has three objectives:

- Procurement independent vendor relations and market watch (Task 1)

- Best practices for energy-efficient HPC Centre Infrastructures design and operations (Task 2)

- Best practices for prototype planning and evaluation (Task 3)

This Work Package builds on the important work performed in previous PRACE Projects in terms of technology watch, know-how and best practices for energy-efficient HPC Centre Infrastructures design and operations, and prototyping of HPC systems. It aims at delivering information and guidance useful for decision makers at different levels. Among them, PRACE aisbl and PRACE sites general managers are clear targets for the technology and market information and orientations collected in this deliverable, but all technical specialists of PRACE partners can be interested in some of the material collected.

This deliverable is the first one of PRACE-4IP Work Package 5 Task 1, it corresponds to a periodic annual update on technology and market trends. This Task 5.1, "Procurement independent vendor relations and market watch", corresponds to the first objective of Work Package 5. It is thus the continuation of a well-established effort, using assessment of the HPC market based on market surveys, supercomputing conferences, and exchanges with vendors and between experts involved in the work package. Trends and innovations based on the work of prototyping activities in previous PRACE projects are also exploited, as well as the observation of current or new technological R&D projects, such as the PRACE-3IP PCP, the Human Brain Project PCP, FP7 Exascale projects and Horizon 2020 FETHPC1-2014 and follow-ups in future Work Programmes.

#### 1 Introduction

The PRACE-4IP Work Package 5 (WP5), "Best Practices for HPC Systems Commissioning", has three objectives:

- Procurement independent vendor relations and market watch (Task 1),

- Best practices for energy-efficient HPC Centre Infrastructures design and operations (Task 2),

- Best practices for prototype planning and evaluation (Task 3).

This Work Package builds on the important work performed in all previous PRACE Projects [1] in terms of technology watch, know-how and best practices for energy-efficient HPC Centre Infrastructures design and operations, and prototyping of HPC systems. It aims at delivering information and guidance useful for decision makers at different levels.

Task 5.1 of PRACE-5IP, "Procurement independent vendor relations and market watch", corresponds to the first objective of Work Package 5. It is the continuation of a well-established effort, using assessment of the HPC market based on market surveys, Top500 analyses, supercomputing conferences, and exchanges with vendors and between experts involved in the work package. Trends and innovations based on the work of prototyping activities in previous PRACE projects are also exploited, as well as the observation of current or new technological R&D projects, such as the PRACE-3IP PCP, the Human Brain Project PCP, FP7 Exascale projects and Horizon 2020 FETHPC1-2014 and follow-ups in future Work Programmes.

This is the first deliverable from Task 1 of Work Package 5 of PRACE. It focussed on technology and market watch only: this means that some best practice and state-of-the-art aspects which were sometimes intertwined with technology watch in past deliverables are now dealt with in other deliverables or white papers (and tasks) of WP5.

This deliverable may contain quite a lot of technical detail on some topics, and is intended for persons actively working in the HPC field. Practitioners should read this document to get an overview of developments on the infrastructure side, and how it may affect planning for future data centres and systems.

This deliverable will be updated by another similar report in one year. It is organised in 5 main chapters. In addition to the introduction (Chapter 1) and the conclusions (Chapter 7) it contains:

- Chapter 2: "Worldwide HPC landscape and market overview" first uses Top500, analysed with a geographical, business topical angle, then proposes some extra considerations from other sources, as well as a brief overview of large HPC initiatives world-wide

- Chapter 3: "Core technologies and components" is a quick overview of processors, accelerators, memory and storage technologies, interconnect technologies

- Chapter 4: "Solution and architectures" gives some vendor snapshots, and looks at some trends in storage, cooling and virtualisation and cloud delivery.

- Chapter 5: "Management tools" is an overview of various tools at system, user resources or log analysis levels.

- Chapter 6: "EU Projects for Exascale and Big Data" scans FP7, H2020 and other projects towards exascale.

# 2 Worldwide HPC landscape and market overview

## 2.1 A quick snapshot of HPC worldwide

The purpose of this section is to present an overview of HPC worldwide, with a special focus on Europe, based on statics derived from the Top500, the Green 500 and the HPCG benchmarks [2][3][4][5].

The focus here is on large systems. Therefore, each time such analysis is applicable and meaningful, special attention is paid to systems among the 50 most powerful in the world according to the Top500 ranking (called "Top50" hereafter). This choice was made according to the fact that, in most cases:

- a Tier-0 system is part of the 50 most powerful system in the world during most of its lifetime.

- a Tier-1 system is part of Top 50 at the time of its installation.

#### 2.1.1 Countries

Analysis was done for the countries that were at least once part of the 10 largest countries in terms of cumulated  $R_{max}$  in the Top50 in the past 5 years:

| Country        | Cumulated R <sub>max</sub> in Top50 (06-2011 to 11-2015) |    |                                      |

|----------------|----------------------------------------------------------|----|--------------------------------------|

|                | Number of times part of the 10 largest countries         |    | Number of times in the best position |

| United States  | 10                                                       | 1  | 10                                   |

| China          | 10                                                       | 2  | 6                                    |

| Japan          | 10                                                       | 2  | 4                                    |

| Germany        | 10                                                       | 3  | 2                                    |

| France         | 10                                                       | 4  | 1                                    |

| United Kingdom | 10                                                       | 5  | 4                                    |

| Italy          | 8                                                        | 7  | 4                                    |

| Switzerland    | 6                                                        | 5  | 1                                    |

| Australia      | 6                                                        | 8  | 2                                    |

| Russia         | 5                                                        | 7  | 2                                    |

| Saudi Arabia   | 3                                                        | 5  | 2                                    |

| Korea, South   | 3                                                        | 6  | 2                                    |

| Sweden         | 2                                                        | 9  | 1                                    |

| Canada         | 1                                                        | 10 | 1                                    |

| Spain          | 1                                                        | 10 | 1                                    |

Table 1: countries for Top50 analysis

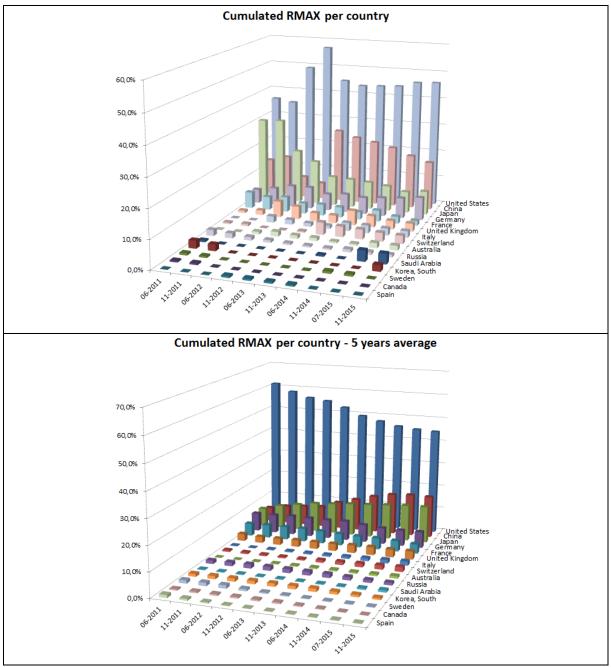

Figure 1 and Figure 2 below show the evolution of the fraction of cumulated Rmax overtime for these countries derived from the Top500. Two figures are shown: one being the fraction of cumulated Rmax for a specific Top500 edition, one being the average over the 5 previous years for a specific Top500 edition. The 5-year period allows to smooth the fluctuations; it was chosen since it is the typical lifetime of a supercomputer.

Regarding the world, the figure shows that, for the previous 18 months, the position of United States and China tends to stabilize after a period during which there was a strong decrease of the United States and a strong increase of China. The other big players are Japan and several European countries.

Regarding Europe, Germany is heading the race while France, United Kingdom, Italy and Switzerland are close to each other with a decreasing slope for France, increasing for the others.

Figure 1: evolution of the fraction of cumulated RMAX overtime for top HPC countries

Figure 2: evolution of the fraction of cumulated RMAX overtime for top HPC countries / Europe

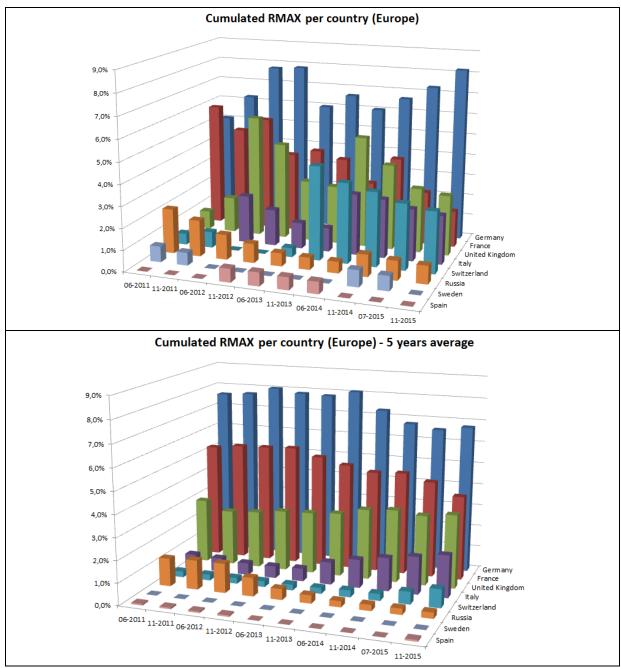

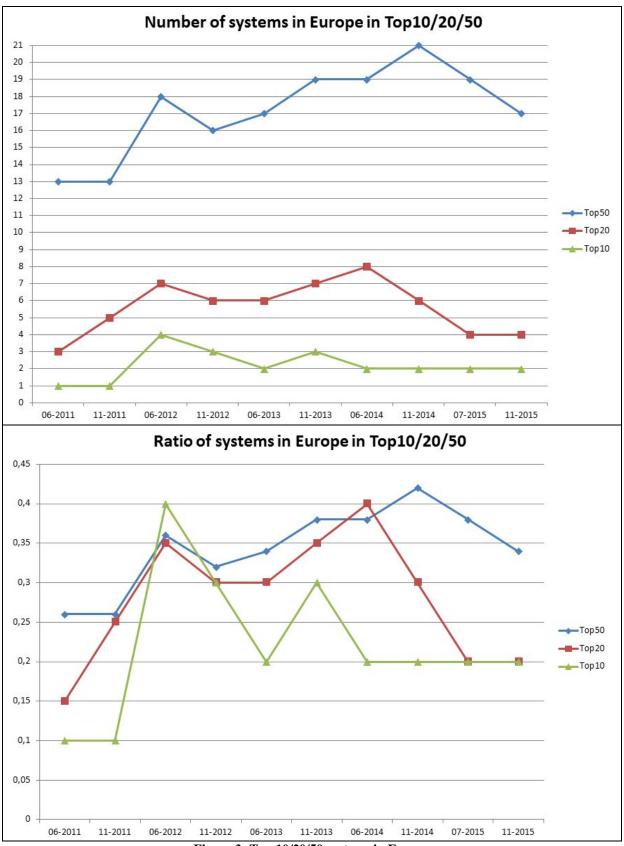

Figure 3 below focuses on Europe in terms of number of systems in the Top10/20/50. The figure shows clearly that the largest systems are not in Europe.

Figure 3: Top 10/20/50 systems in Europe

#### 2.1.2 Accelerators

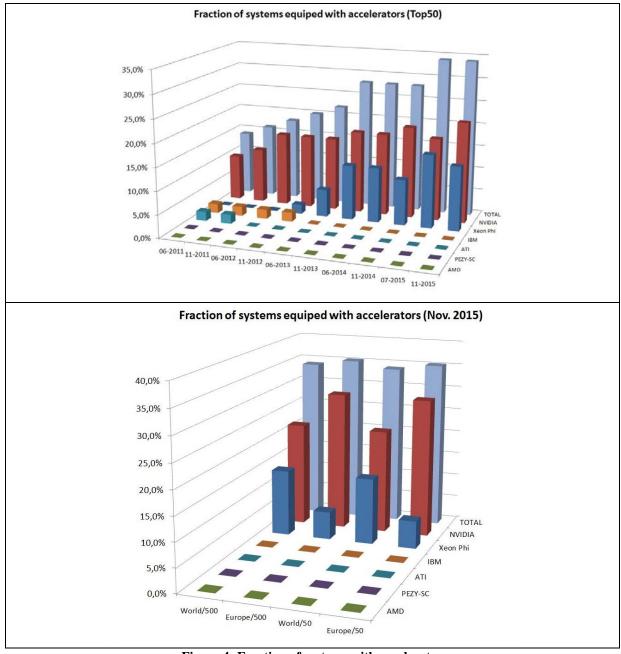

Figure 4 below, on the left, shows the fraction of systems equipped with accelerators in the Top50. The figure on the right compares Europe with the world in term of accelerators both for the Top50 and the Top500.

Regarding the first figure, the growth of fraction of system equipped with accelerators tends to slow down. Nvidia GPU and Intel Xeon Phi are the major players and are quite comparable in terms of penetration, with a slight advantage for Nvidia GPU.

Regarding the second figure, the fraction of accelerators is roughly the same in the Top50 and in the Top500. The penetration of Intel Xeon Phi in Europe is much lower than in the world, Nvidia GPU being by far in Europe (both in Top50 and Top500) the leader.

Figure 4: Fraction of systems with accelerators

#### 2.1.3 Age

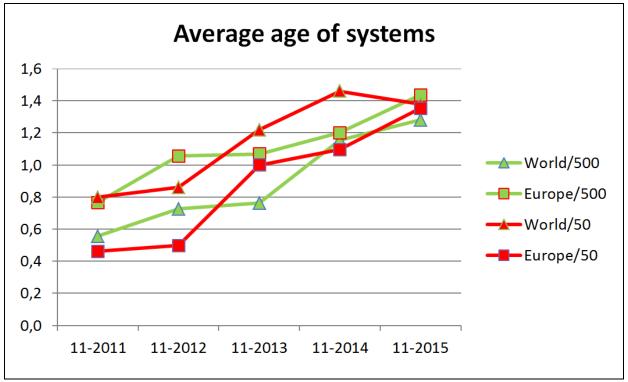

Figure 5 below shows the age of systems (in terms of time of presence in the Top500) for the world and for Europe.

The age of systems has been steadily increasing for the last 5 years for the Top50 and the Top500 except for the last year during which the average age of system in the Top50 has slightly decreased at the world level.

Figure 5: Average age of systems

#### 2.1.4 Vendors

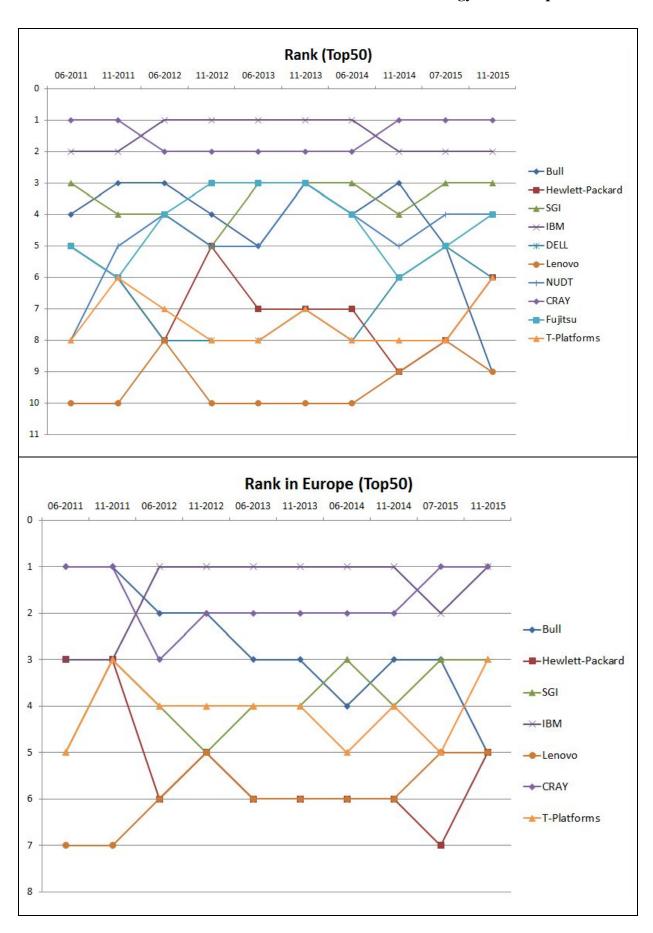

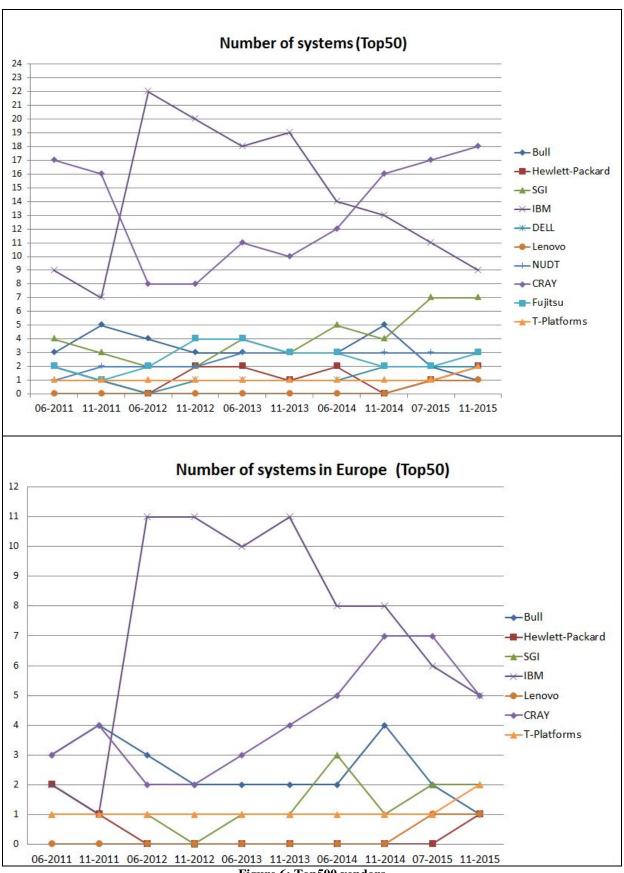

The charts in Figure 6 below show the relative position of the vendor at the world and European level. The most visible trend is the fall of IBM, related to the fact that IBM is no longer selling x86 HPC systems (LENOVO taking over for this activity), and the rise of Cray. This trend is visible at European level and stronger at the world level.

Figure 6: Top500 vendors

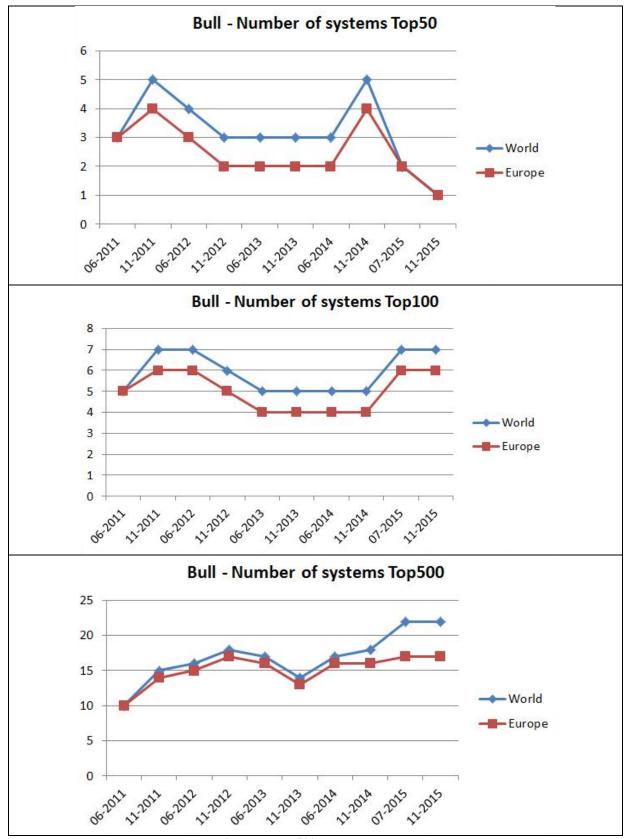

Figure 7 below focus on the only European vendor at Top50/Tier-0 capability level (excluding vendors from Russia): Bull. They show that the presence of Bull in the Top50 has recently decreased, the presence is stable in the Top100 and increasing in the Top500.

Figure 7: Top500 European vendor

#### 2.1.5 Computing efficiency

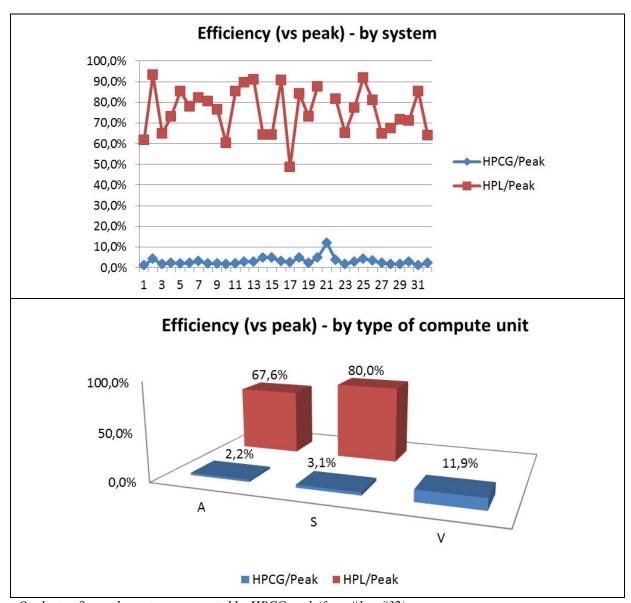

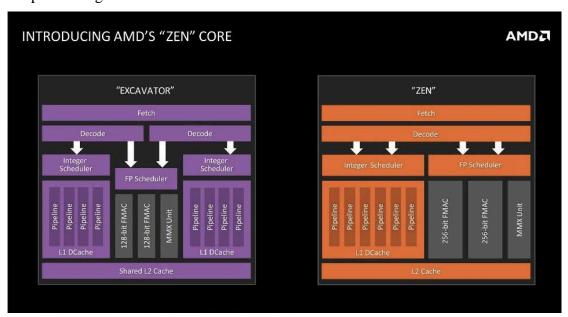

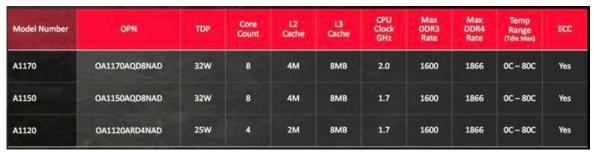

In Figure 8 HPCG shows a much smaller variation than HPL, with the exception of system #21. This system is a NEC SX-ACE based system (Earth Simulator at CEIST), and the same pattern applies to all the SX-ACE systems on the HPCG list. This architecture seems to score well on the HPCG benchmark relative to HPL.

On the top figure the systems are sorted by HPCG rank (from #1 to #32) On the bottom figure, A= accelerated, S= scalar, V=vector.

Figure 8: HPL vs. HPCG efficiency comparison

#### 2.1.6 Energy efficiency

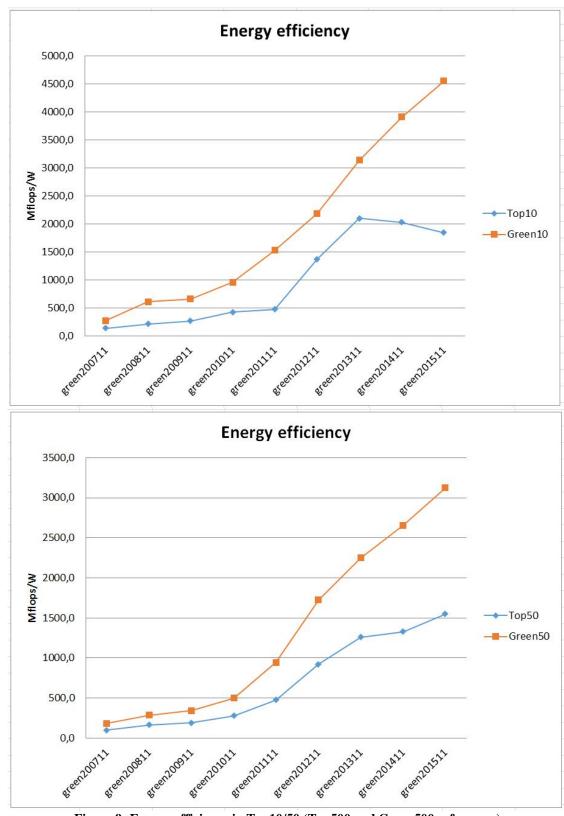

While the Green500 efficiency ratio is steadily climbing upwards, the Top10 systems are showing a slight decrease. As seen in the second graph of Figure 9 this is not the case when widening the base to Top50. This reflects a more marked focus on peak performance for the high end and a widening gap between  $R_{\text{max}}$  and  $R_{\text{peak}}$ . Between 2013 and 2015 several energy efficient systems exited the Top10.

Figure 9: Energy efficiency in Top10/50 (Top500 and Green500 references)

## 2.2 Some more business analysis

#### 2.2.1 General impressions from SC'15

Intel was dominating the conference and had a very high visibility, also through collaborations with other vendors. Some vendors even seemed to keep their non-Intel based products out of the limelight due to this. Not much in the way of products was shown, that wasn't based on Intel hardware on the CPU level.

Storage played a more important role than ever, along with data analysis. This is of course fuelled by the "Big Data" trend.

Chinese vendor Sugon (formerly Dawning) made a large showing on the TOP500, but this was mainly due to putting in the effort to benchmark already installed systems. There have been some press releases about Sugon and its primary Chinese competitor Inspur, both having a strong presence at SC15, about their possible new US and Europe go-to-market strategy [6].

#### 2.2.2 Market trends according to some analysts

There is a converging vision and analysis of the market analysts on a few facts and projections [7][8][9][10][11]:

- good overall shape of the HPC and servers market, especially in Asia/Pacific and with a strong China lead that is pulling the growth (top four Chinese OEMs Inspur, Huawei, Lenovo, and Sugon); high-end of the sever market, which is roughly the HPC segment, has less robust and more irregular growth

- HPE a quantitative leader, all the more than the usual challenger, IBM, which has now split LENOVO and IBM shares in total roughly accounting for past IBM alone share

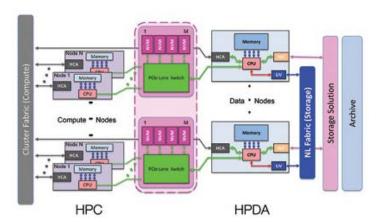

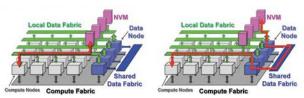

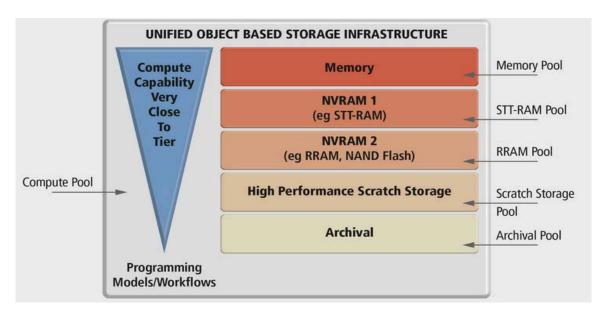

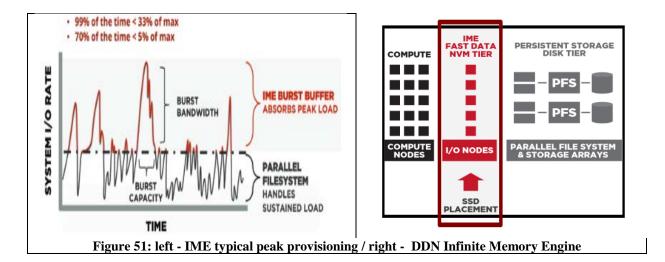

- still dominant x86 position, IBM POWER server sales growing, ARM server sales not growing

- storage, HPDA (High Performance Data Analytics), rising in terms of market volume Some of these trends merely confirm the impressions and observations collected during SC15, as explained in previous section.

## 2.3 Large initiatives world-wide

#### 2.3.1 *US NSCI*

In July 2015 President Obama issued an Executive Order establishing the National Strategic Computing Initiative (NSCI) aiming at ensuring the United States continues leading in this field over the coming decades [12][13]. NSCI defines a multi-agency framework for furthering U.S. "economic competitiveness and scientific discovery" through orchestrated advances in high performance computing (HPC). We can see this as a further step in US efforts to structure and fund a federal initiative in the area of HPC – in the last decades we had observed a number of different programmes from DARPA or DOE, with some progressive connection and alignment of the policies and approaches of different labs or agencies (the DOE/NNSA with a three-lab approach, then DOE NNSA and Office of Science together - CORAL joint Collaboration of Oak Ridge, Argonne, and Lawrence Livermore (CORAL) was established in early 2014). CORAL procurement is typical of US approach, with a single process to acquire next-generation supercomputers with strong R&I requirements for three DOE national laboratories [15]. As IDC states [18][33]: "Government and government-related portions of the U.S. HPC market are effectively closed to non-U.S. system vendors by "Buy American" legislation and other preferential policies and practices".

This time the global economic impact of the NSCI programme, boosting innovation and expanding HPC usage to industrial and societal usages, are particularly emphasized. The announcement has been widely commented since mid-2015 and a recurring discussion has been on funding amounts and sustainability – the US political mechanisms and agenda make the funding process complex and progressive. This goes with a revised target of exascale machines by 2023.

## 2.3.2 Japan Post K and Flagship 2020

Japan launched in 2014 a new flagship HPC project for the 2020 horizon - now called the FLAGSHIP 2020 Project - targeting exascale for the succession of K computer in 2020. MEXT - Ministry of Education, Culture, Sports, Science and Technology - is still the driving authority, with RIKEN AICS (Advanced Institute for Computational Science) in charge of the implementation of the dedicated project, which encompasses technology development and related application enabling. There was a tender leading to the selection of Fujitsu as the vendor in charge [19][20][21][22]. Kobe AICS site would host the future system. Budget is in the order of 850 M€(110 billion yens), including R&D, machine acquisition and application development. Co-design is strongly asserted between RIKEN and Fujitsu. Scientific and societal challenges have already been carefully selected with organisations in charge, covering 9 themes in 5 areas as shown in table Table 2 below.

| Priority issues                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Achievement of a society that provides health and longevity                                                                             |

| Theme 1 - Innovative drug discovery infrastructure through functional control of biomolecular systems                                   |

| Theme 2 - Integrated computational life science to support personalized and preventive medicine                                         |

| Disaster prevention and global climate problems                                                                                         |

| Theme 3 - Development of integrated simulation systems for hazard and disaster induced by earthquake and tsunami                        |

| Theme 4 Advancement of meteorological and global environmental predictions utilizing observational "Big Data"                           |

| Energy problems                                                                                                                         |

| Theme 5- Development of new fundamental technologies for high-efficiency energy creation, conversion/storage and use                    |

| Theme 6 - Accelerated development of innovative clean energy systems                                                                    |

| Enhancement of industrial competitiveness                                                                                               |

| Theme 7 - Creation of new functional devices and high-performance materials to support next-generation industries                       |

| Theme 8 - Development of innovative design and production processes that lead the way for the manufacturing industry in the near future |

| Development of basic science                                                                                                            |

| Theme 9 - Elucidation of the fundamental laws and evolution of the universe                                                             |

Table 2: Social and scientific priority issues to be tackled by using Post K computer

The term FLAGSHIP is also an abbreviation of Future LAtency core-based General-purpose Supercomputer with HIgh Productivity, which shows the strong concern for usability and targeted pervasiness of usage of outcomes of the project.

#### 2.3.3 China

China has had a steady HPC ambition, primarily via government entities Chinese Academy of Sciences (CAS) and its academic partner the National University of Defense Technology (NUDT) for quite a while, even including the development of domestic processors. Recent economic slowing down in China may affect this but probably not change the mid to long-term trend. Chinese government investments in HPC have risen rapidly in recent years, and the willingness of independence from non-Chinese (primarily U.S.)

Last year there were 'diplomatic' moves between the US and China, U.S. government blocking Intel from exporting its processors to upgrade Tianhe-2 and some other leading supercomputers in China - claiming that the computers were being used for nuclear weapons research. This probably exacerbated or at least did not slow down Chinese plans for developing indigenous technology [16].

The U.S. government's recent decision to ban Intel from exporting Xeon x86 and Xeon Phi processors to upgrade Tianhe-2 and several other leading supercomputers in China may accelerate China's efforts (and financing) to advance domestic processor development. Also of note, China has urged investment banks and other "critical infrastructure" sites to replace non-Chinese HPC systems (primarily IBM) with Chinese supercomputers. Lenovo's acquisition of IBM's x86 server business should enable Lenovo as a Chinese firm to move into these sites. Some Chinese supercomputers already incorporate Chinese processors. Work is on-going on the follow-up of Tianhe-2 Express-2 interconnect network, compliant with Intel Phi but also a domestic DSP chip now announced by the National University of Defence – the Matrix 2000 GPDSP 'China Accelerator', a 64-bit, 2.4 Teraflops one (in double precision) running at 1 GHz with a power consumption of around 200W –comparable to the Intel Xeon Phi [17].

## 2.3.4 *Europe*

Horizon 2020 HPC programme is now well established, with the contractual Public Private Partnership (cPPP) encompassing technology and related R&D, and Centres of Excellence for Computing Applications (CoEs) [23]. Nineteen so-called FETHPC projects were selected in 2015, plus two Coordination and Support Actions (CSA) [131]. Besides this eight Centres of Excellences [119] were also selected from the calls launched in the framework of Work Programme 2014-2015.

Chapter 6 gives more details on these projects, with some quick technical hints.

The 'HPC infrastructure' pillar is not formally included in the scope of the cPPP (which covers Technologies – FETHPC – and Applications – CoEs), but has strong links developed at PRACE aisbl and PRACE IP projects levels. PRACE aisbl [1] is still working on the transition to 'PRACE 2" after the successful initial period of 5 years of the infrastructure. PRACE 3IP project is still running via its PCP activity – see section 6.6.1- in parallel of PRACE 4IP. A PRACE 5IP project has just been submitted in EINFRA-11-2016 call closing end of March [24].

FETHPC and CàE calls within Work Programme 2014-2015 of H2020 totalised around 140 M€of EC funding, out of the 700 provisioned for the HPC cPPP.

ETP4HPC [28] has been growing steadily (gaining more members, 72 as of March 2016 [29]) and produced a new release of its Strategic Research Agenda (SRA) in November 2016 [27]. This document is the more detailed technical reference going with the HPC call in Work

Programme 2016-2107, which was elaborated using the EC/ ETP4HPC structured dialogue within the cPPP framework.

The FETHPC call in Work Programme 2016-2017has 3 topics [25][26]:

- FETHPC-01-2016: Co-design of HPC systems and applications, for RIA (Research and Innovation Action) projects, closing September 2016 with a budget of €41 M€

- FETHPC-02-2017: Transition to Exascale Computing, for RIA projects, closing September 2017, with a budget of €40 M€

- FETHPC-03-2017: Exascale HPC ecosystem development, for CSA (Coordination and Support Action) projects, closing September 2017 with a budget of €4 M€

It can thus be said that the programme is on track and well engaged now. It already shows increased interaction between academia, research organisations, and private companies on the technology supply side (including many SMEs). However, the fragmentation into many relatively small projects remains quite high, even if WP 2016-2107 is showing some focus effort (FETHPC-01-2016 topic).

It must be noted that a significant amount of funding remains to be allocated out of the cPPP 700 M€ Future Work Programme 2018-2020 should thus have higher funding that the two previous ones. ETP4HPC is working on the R&D contents for this future stage, also proposing a concept of Extreme Scale Demonstrators that would integrate outcomes of R&D projects funded in Work Programmes 2014-2015 and 2016-2107 (see ETP4HPC SRA 2015 - chapter 8 in [27]).

FETHPC-1 call of WP206-2017 also funded two CSAs (cf section 6.4). EXDCI, the European Extreme Data & Computing Initiative, is one of these [30]. Its objective is to coordinate the development and implementation of a common strategy for the European HPC Ecosystem. The two most significant HPC bodies in Europe, PRACE and ETP4HPC, joined their expertise in this 30-month project. EXDCI's first period (first 6 months) activities show very promising momentum for the whole EU HPC community to develop joint visions (Rome Sept 2015 [32], Prague May 2016 [31]).

Mid-2015 IDC report (SMART action funded by the EC [18][33]) was published on the progress of the European HPC Strategy toward ensuring European leadership in the supply and use of HPC systems and services by 2020, and provided recommendations for its implementation. Good progress has been reported regarding the overall progress and momentum, while emphasizing some questions or shortcomings.

A general trend and a framework for analysis is the intertwining of HPC with a growing number of industrial applications and scientific and societal domains. This places HPC as one of the key contributors to the Digital Single Market (DSM) strategy being developed by the EC since more than one year [34]. More precise plans are expected to be made public soon (April) in this perspective, updating and widening 2012 EC Communication "High Performance Computing (HPC): Europe's place in a global race", including the notion of a European Science Cloud [35].

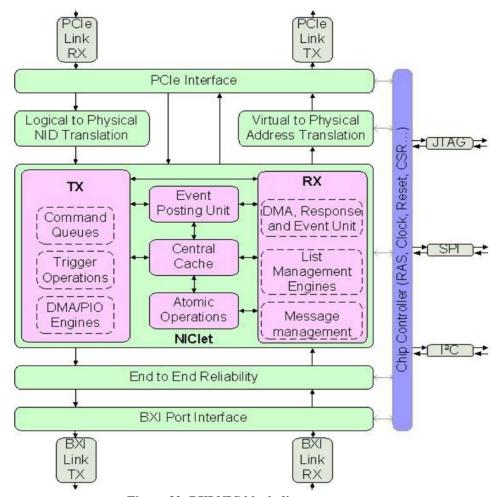

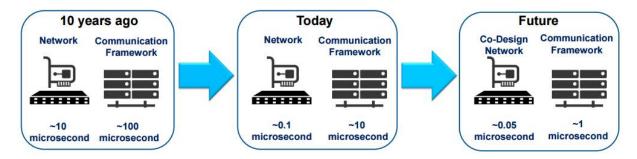

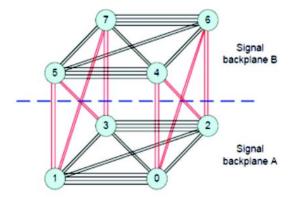

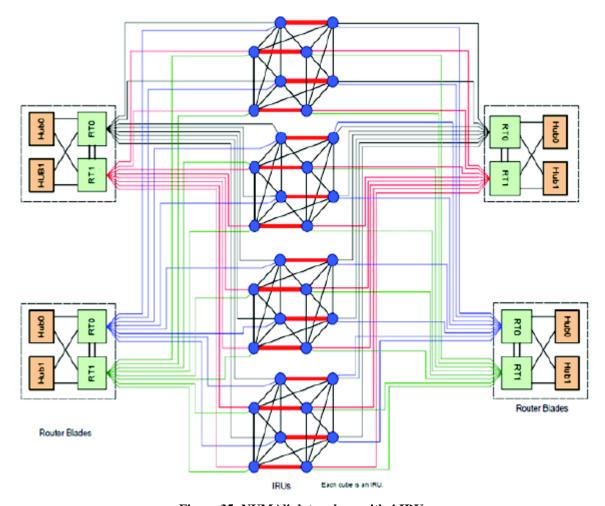

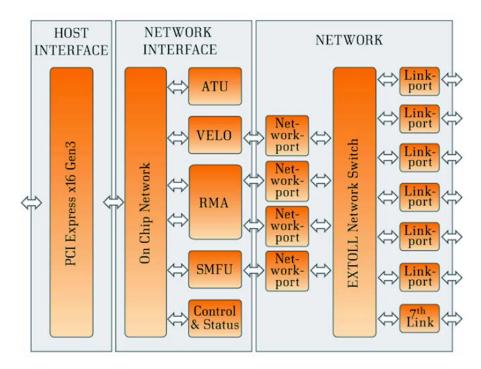

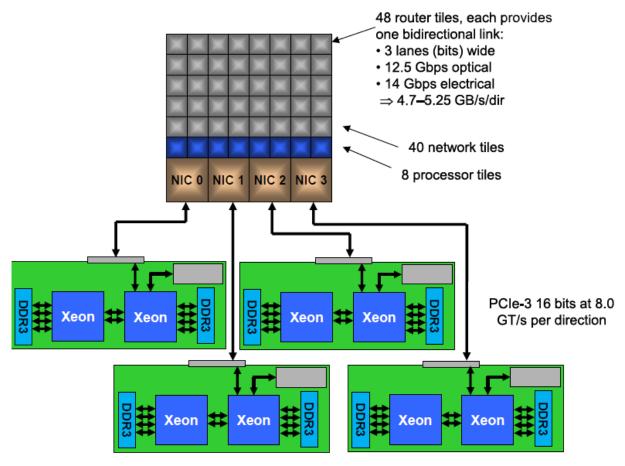

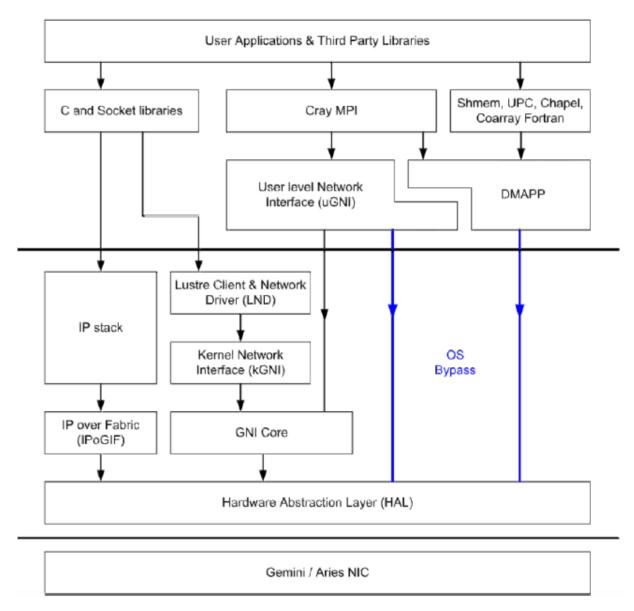

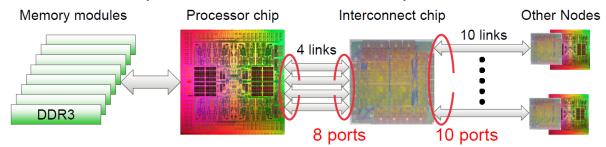

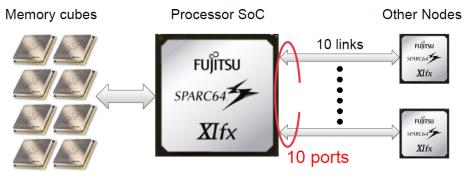

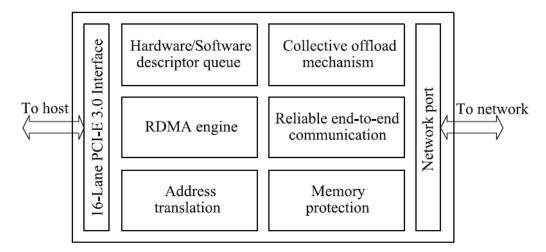

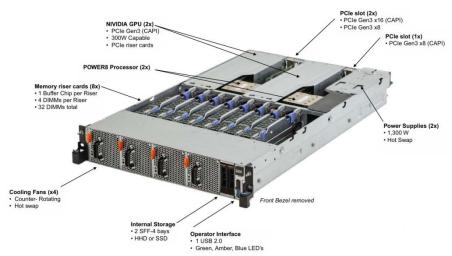

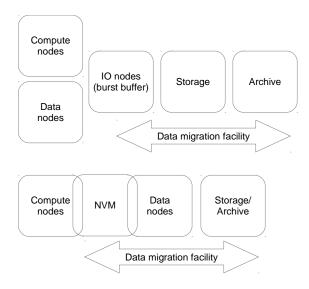

Meanwhile (November 2015) an initiative led by a few Member States (Luxembourg, France, Italy, Spain) has been announced, so-called IPCEI HPC-BDA, an Important Project of Common European Interest mixing HPC and Big Data objectives [36]. This is understood as an action from volunteering countries wanting to optimise different aspects of a large European initiative aligned with the objectives of the aforementioned plan to come. Aggregation of fundings from EC sources, national sources and private sources to support the project, state aids regulations, competition regulation are aspects that such an IPECI can help