## SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

# INFRA-2012-2.3.1 – Third Implementation Phase of the European High Performance Computing (HPC) service PRACE

## PRACE-3IP

# **PRACE Third Implementation Phase Project**

**Grant Agreement Number: RI-312763**

# D8.3.4 Technical lessons learnt from the implementation of the joint PCP for PRACE-3IP

**Final**

Version: 1.5

Author(s): Stephen Booth, EPCC

Date: 10.01.2018

## **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-312763                                                               |                |  |

|---------------|-----------------------------------------------------------------------------------------|----------------|--|

|               | Project Title: PRACE Third Implementation Phase Project                                 |                |  |

|               | Project Web Site: <a href="http://www.prace-project.eu">http://www.prace-project.eu</a> |                |  |

|               | Deliverable ID: D8.3.4                                                                  |                |  |

|               | <b>Deliverable Nature:</b> <report></report>                                            |                |  |

|               | Deliverable Level: Contractual Date of Delivery:                                        |                |  |

|               | PU                                                                                      | 31 / 12 / 2017 |  |

|               | Actual Date of Delivery:                                                                |                |  |

|               | 15 / 01 / 2018                                                                          |                |  |

|               | EC Project Officer: Leonardo Flores Añover                                              |                |  |

<sup>\* -</sup> The dissemination level are indicated as follows: PU – Public, PP – Restricted to other participants (including the Commission Services), RE – Restricted to a group specified by the consortium (including the Commission Services). CO – Confidential, only for members of the consortium (including the Commission Services).

## **Document Control Sheet**

|          | Title: Technical lessons learnt from the implementation of the joint |               |  |

|----------|----------------------------------------------------------------------|---------------|--|

| Document | PCP for PRACE-3IP                                                    |               |  |

|          | ID: D8.3.4                                                           |               |  |

|          | Version: 1.5                                                         | Status: Final |  |

|          | Available at:                                                        |               |  |

## **Document Status Sheet**

| Version | Date       | Status | Comments             |

|---------|------------|--------|----------------------|

| 0.1     | 19/10/2017 | Draft  | Initial outline      |

| 0.2     | 20/10/2017 | Draft  |                      |

| 0.3     | 27/10/2017 | Draft  | PCP section          |

| 0.4     | 10/11/2017 | Draft  | General lessons      |

| 0.5     | 28/11/2017 | Draft  | Technical background |

| 0.6     | 11/12/2017 | Draft  | E4 sections          |

#### D8.3.4 Technical lessons learnt from the implementation of the joint PCP for PRACE-3IP

| 0.7 | 11/12/2017 | Draft     | ATOS-BULL sections      |  |

|-----|------------|-----------|-------------------------|--|

| 0.8 | 12/12/2017 | Draft     | User experiences        |  |

| 0.9 | 14/12/2017 | Draft     | Formatting              |  |

| 1.0 | 14/12/2017 | Draft     | User experience section |  |

| 1.1 | 16/12/2017 | Draft     | Commits & corrections   |  |

| 1.2 | 22/12/2017 | Draft     | Editorial updates       |  |

| 1.3 | 09/01/2017 | Pre-Final | Updates based on        |  |

|     |            |           | internal review reports |  |

| 1.4 | 10/01/2017 | Pre-Final | Error in Table 19 fixed |  |

| 1.5 | 10/01/2018 |           | Last corrections        |  |

## **Document Keywords**

| Keywords: | PRACE, HPC, Research Infrastructure, Joint Pre Commercial |

|-----------|-----------------------------------------------------------|

|           | Procurement, Energy Efficiency                            |

|           |                                                           |

#### **Disclaimer**

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° RI-312763. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2018 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-312763 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

## **Table of Contents**

| Pr | roject and Deliverable Information Sheet                           | i   |

|----|--------------------------------------------------------------------|-----|

| Do | ocument Control Sheet                                              | i   |

| Do | ocument Status Sheet                                               | i   |

| Do | ocument Keywords                                                   | ii  |

|    | able of Contents                                                   |     |

|    | ist of Figures                                                     |     |

|    |                                                                    |     |

|    | ist of Tables                                                      |     |

|    | eferences and Applicable Documents                                 |     |

| Li | ist of Acronyms and Abbreviations                                  | vii |

| Ex | xecutive Summary                                                   | 12  |

|    | 1 Introduction                                                     | 13  |

|    | 2 Overview of the PRACE PCP                                        | 13  |

|    | 3 Technical Background                                             | 14  |

| 4  | Lessons learned from the Atos-Bull KNL pilot system                | 17  |

| -  | 4.1 Description of the system                                      |     |

|    | 4.1.1 System description                                           |     |

|    | 4.1.2 Software environment                                         |     |

|    | 4.1.3 Energy efficiency aspects of the design                      |     |

|    | Technology related                                                 |     |

|    | Infrastructure for Energy monitoring and optimization              | 22  |

|    | 4.2 Suitability for general purpose HPC                            | 28  |

|    | 4.2.1 Ease of code development and porting                         | 28  |

|    | 4.2.2 Energy monitoring/prediction                                 | 29  |

|    | 4.2.3 System usability                                             |     |

|    | 4.3 Impact on energy efficiency                                    |     |

|    | 4.3.1 Final results for HPL                                        |     |

|    | 4.3.2 Final results for NEMO                                       |     |

|    | 4.3.3 Final results for SPECFEM3D                                  |     |

|    | Small test case                                                    |     |

|    | Large test case                                                    |     |

|    | 4.3.4 Final results for BQCD                                       |     |

|    | 4.3.5 Final results for Quantum Espresso                           |     |

|    | 4.4 Schedule and timing                                            |     |

|    | 4.5 Impact on Atos-Bull roadmap                                    |     |

|    | 4.6 Summary of lessons learned from the Atos-Bull KNL pilot system |     |

| 5  | Lessons learned from the Maxeler data-flow pilot system            |     |

|    | 5.1 Description of the Maxeler data-flow pilot system              |     |

|    | 5.1.1 System description                                           |     |

|    | 5.1.2 Software environment                                         |     |

|    | 5.1.3 Energy efficiency aspects of the design                      |     |

|    | 5.2 Suitability for general purpose HPC                            |     |

|    | 5.3 Impact on energy efficiency                                    |     |

|    | 5.4 Schedule and timing                                            |     |

|    | 5.5 Impact on Maxeler roadmap                                      | 46  |

|    | 5.6 Lessons Learnt                                       | 47 |

|----|----------------------------------------------------------|----|

| 6  | Lessons learned from the E4 Power-8+/Pascal pilot system | 47 |

|    | 6.1 Description of the system                            | 47 |

|    | 6.1.1 System description                                 | 48 |

|    | Compute node                                             | 48 |

|    | Liquid cooling                                           | 48 |

|    | Compute accelerators                                     | 48 |

|    | 6.1.2 Energy efficiency aspects of the design            | 49 |

|    | Technology related                                       |    |

|    | Infrastructure for Energy monitoring and optimization    | 49 |

|    | 6.2 Suitability for general purpose HPC                  | 52 |

|    | 6.2.1 Ease of code development and porting               | 52 |

|    | 6.2.2 Energy monitoring/prediction                       | 52 |

|    | 6.2.3 System usability                                   | 53 |

|    | 6.3 Impact on energy efficiency                          | 53 |

|    | 6.4 Schedule and timing                                  | 55 |

|    | 6.5 Impact on E4 roadmap                                 | 56 |

|    | 6.6 Lessons Learnt                                       | 56 |

| 7  | Lessons learned from the E4 ARM prototype system         | 57 |

| •  | 7.1 Description of the E4 ARM prototype system           |    |

|    | 7.1.1 System description.                                |    |

|    | 7.1.2 Software environment                               |    |

|    | 7.1.3 Energy efficiency aspects of the design            |    |

|    | 7.2 Suitability for general purpose HPC                  |    |

|    | 7.2.1 Ease of code development and porting               |    |

|    | 7.2.2 Energy monitoring/prediction                       |    |

|    | 7.2.3 System usability                                   |    |

|    | 7.2.4 User experiences and feedback                      |    |

|    | 7.3 Impact on energy efficiency                          |    |

|    | 7.4 Schedule and timing                                  |    |

|    | 7.5 Impact on E4 roadmap                                 |    |

| 8  | User experiences and feedback                            |    |

| U  | 8.1 EoCoE                                                |    |

|    | 8.2 PRACE-4IP                                            |    |

|    | 8.2.1 KNL pilot system                                   |    |

|    | 8.2.2 Power8 + GPGPU pilot system                        |    |

| 9  | General lessons                                          |    |

| 9  |                                                          |    |

|    | 9.1 Impact of downstream component schedules             |    |

|    | 9.2 Interconnect                                         |    |

|    | 9.3 File-systems                                         |    |

|    | 9.4 Cooling systems                                      |    |

|    | 9.5 Energy aware scheduling                              |    |

|    | 9.6 Use of FPGAs                                         |    |

| 10 | Conclusions                                              | 66 |

# **List of Figures**

| Figure 1: Sequana Cell view                                                                      | 17  |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 2: Sequana KNL blade with 3 KNL nodes                                                     | 18  |

| Figure 3: SCS5 Components                                                                        | 19  |

| Figure 4: Internal view of the 15kW shelf                                                        | 21  |

| Figure 5: HDEEM board                                                                            | 22  |

| Figure 6: Evolution of power metrics for a compute node                                          | 24  |

| Figure 7: Architecture of the metrics framework                                                  |     |

| Figure 8: Example of energy visualization                                                        | 26  |

| Figure 9: Adaptive Power Management behaviour during Linpack                                     | 27  |

| Figure 10: Node 1048 power evolution                                                             | 31  |

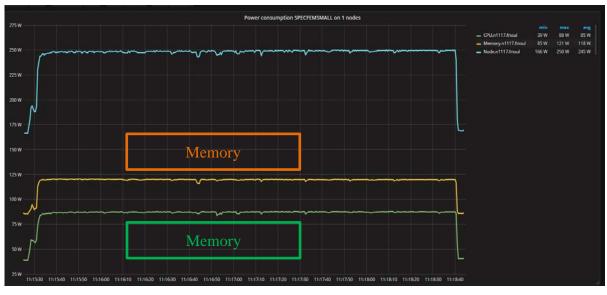

| Figure 11: SPECFEM3D small test case on 1 node                                                   | 32  |

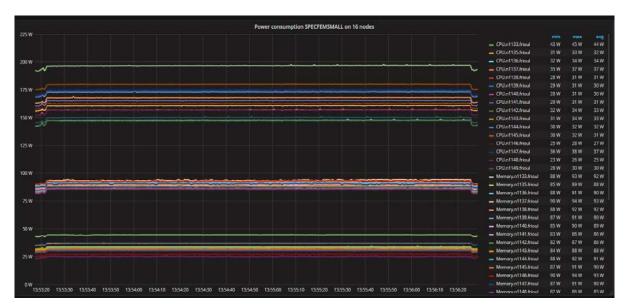

| Figure 12: SPECFEM3D small test case on 16 nodes                                                 | 33  |

| Figure 13: zoom of specfem3D small test case on 16 nodes                                         | 33  |

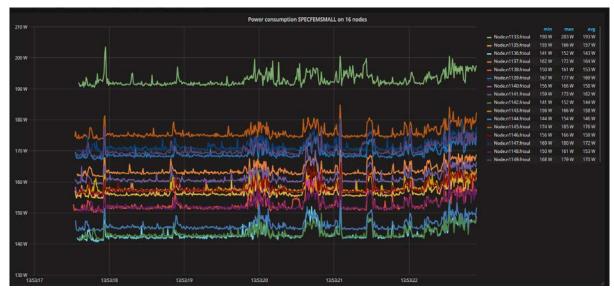

| Figure 14: Specfem3D large test case, zoom on 1 copy                                             | 34  |

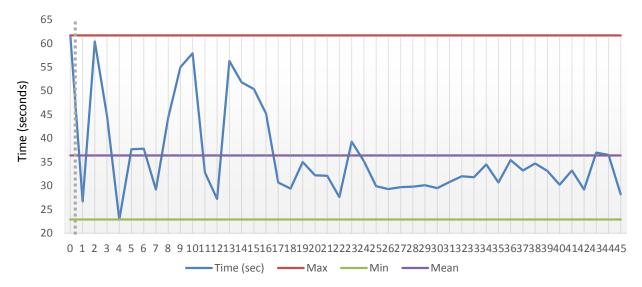

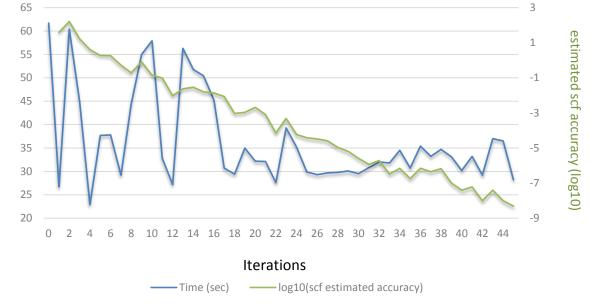

| Figure 15 Time in second per interation in Quantum ESPRESSO                                      | 37  |

| Figure 16: Time in second per iteration with respect to scf estimated accuracy (log10) for Quant | um  |

| Espresso                                                                                         |     |

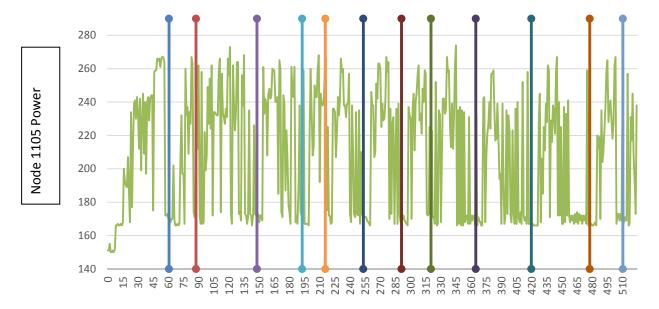

| Figure 17: Node n1105 Power per second, from initialisation to iteration 11                      | 38  |

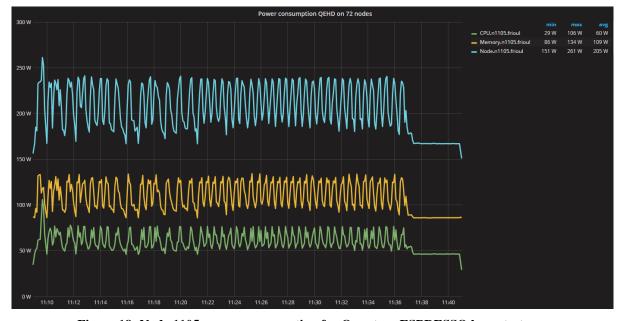

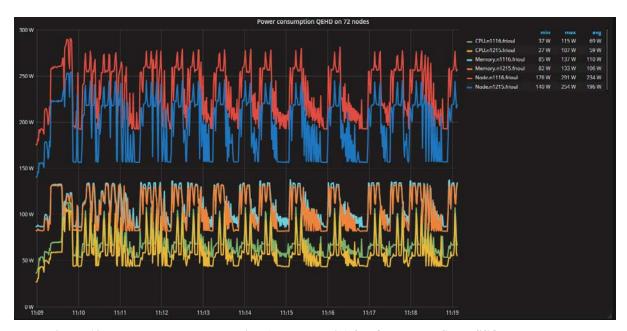

| Figure 18: Node 1105 energy consumption for Quantum ESPRESSO large test case                     |     |

| Figure 19: Nodes energy consumption (max and min) for Quantum ESPRESSO large test case           | 39  |

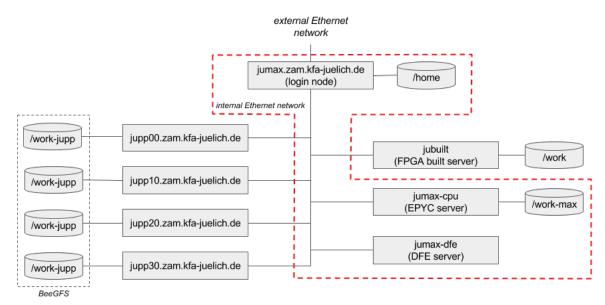

| Figure 20: Overview on the planned testbed for reconfigurable and data-intensive computing with  | the |

| integrated Maxeler Pilot System. The components of the latter are shown by the dashed line       | 41  |

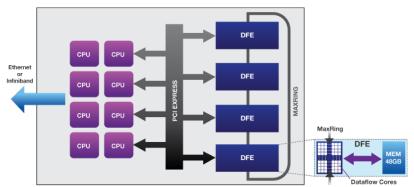

| Figure 21: Maxeler MPC series node architecture (©Maxeler).                                      | 42  |

| Figure 22: A Maxeler MAX5C card (©Maxeler).                                                      | 42  |

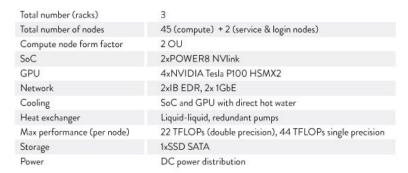

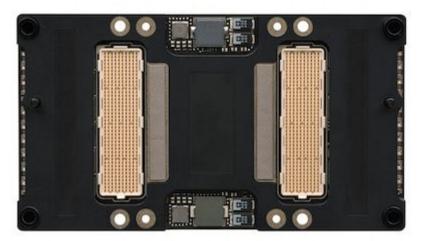

| Figure 23: DAVIDE compute node                                                                   |     |

| Figure 24: NVIDIA Tesla P100                                                                     |     |

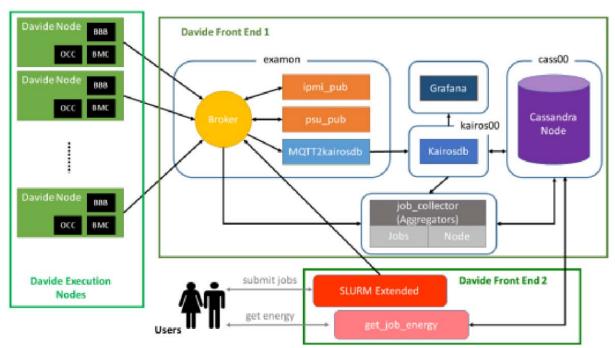

| Figure 25: EXAMON: The general architecture of the monitoring framework                          |     |

| Figure 26: HPL energy efficiency of DAVIDE with different cooling systems as compared to the     |     |

| system of the Green500 in 2013 (Eurora by Eurotech co-funded by PRACE as well)                   |     |

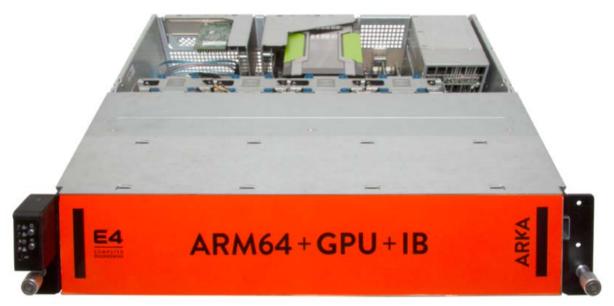

| Figure 27: ARM+GPU compute node                                                                  |     |

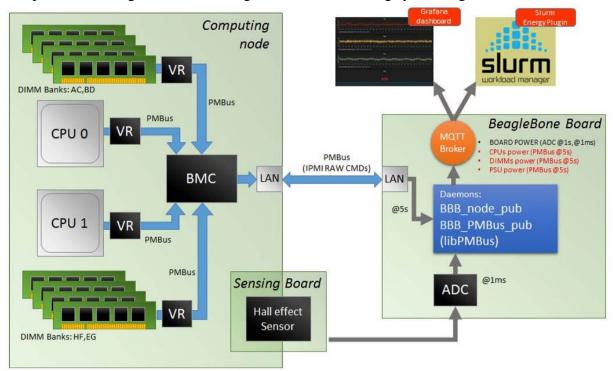

| Figure 28: block diagram of the monitoring system                                                | 59  |

|                                                                                                  |     |

|                                                                                                  |     |

| List of Tables                                                                                   |     |

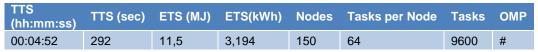

| Γable 1: TTS and ETS projections for 0.5 PFLOP/s Bull Pilot System.                              | 30  |

| Table 2: HPL large test case results                                                             |     |

| Γable 3: HPL GFlops per Watts (nodes)                                                            |     |

| Γable 4: NEMO small test case BULL results                                                       |     |

| Table 5: NEMO large test case BULL results                                                       |     |

| Γable 6: SPECFEM3D mesher small test case results                                                |     |

| Γable 7: SPECFEM3D solver small test case results                                                |     |

| Table 8: SPECFEM3D mesher large test case results for 1 copy                                     |     |

| Table 9: SPECFEM3D solver large test case results for 1 copy                                     |     |

| Table 10: BQCD small test case BULL results                                                      |     |

| Table 11: BQCD large test case BULL results                                                      |     |

| Table 12: Quantum Espresso small test case BULL results                                          |     |

| Table 13: Quantum Espresso parameters value for large test case                                  |     |

| Table 14: Quantum Espresso large test case Atos-Bull results                                     |     |

| Table 15: Quantum Espresso energy consumed for job 8017 and 8201                                 |     |

| Table 16: Quantum Espresso energy consumed for job 8256 and 8201                                 |     |

| Table 17: Comparisons of QE runs with and without energy consumption                             |     |

| Table 18: Comparison of TTS and ETS on the Maxeler pilot system.                                 |     |

| Table 19: Comparison between reference and measured values for TTS / ETS on E4 pilot system      | 55  |

## **References and Applicable Documents**

- [1] ExaScale Computing Study: Technology Challenges in Achieving Exascale Systems DARPA TR-2008-13

- [2] "Mediterranean-stile job scheduler for supercomputers do less when it's too hot!", A. Borghesi, C. Conficoni, M. Lombardi et Al, 2015 International Conference on High Performance Computing & Simulation, HPCS 2015, Amsterdam, Netherlands, July 20-24, 2015.

- [3] D7.7 Performance and energy metrics on PCP systems, PRACE-4IP Deliverable

- [4] http://www.eocoe.eu/events/scientific-applications-towards-exascale

- [5] The bi-annually published Top500 list (<a href="https://www.top500.org">https://www.top500.org</a>) comprises the world's 500 fastest HPC systems in terms of throughput of floating-point operations while executing the High Performance Linpack benchmark.

#### D8.3.4

## **List of Acronyms and Abbreviations**

AAA Authorization, Authentication, Accounting.

ACF Advanced Computing Facility

ADP Average Dissipated Power

AISBL Association International Sans But Lucratif

(legal form of the PRACE-RI)

AMD Advanced Micro Devices

APGAS Asynchronous PGAS (language)

API Application Programming Interface

APML Advanced Platform Management Link (AMD)

ASIC Application-Specific Integrated Circuit

ATI Array Technologies Incorporated (AMD)

BAdW Bayerischen Akademie der Wissenschaften (Germany)

BCO Benchmark Code Owner

BLAS Basic Linear Algebra Subprograms

BSC Barcelona Supercomputing Center (Spain)

CAF Co-Array Fortran

CAL Compute Abstraction Layer

CCE Cray Compiler Environment

ccNUMA cache coherent NUMA

CEA Commissariat à l'énergie atomique et aux énergies alternatives

CGS Classical Gram-Schmidt

CGSr Classical Gram-Schmidt with re-orthogonalisation

CINECA Consorzio Interuniversitario, the largest Italian computing centre (Italy)

CINES Centre Informatique National de l'Enseignement Supérieur (represented

in PRACE by GENCI, France)

CLE Cray Linux Environment

CoE Center of Execellence

CPU Central Processing Unit

CSC Finnish IT Centre for Science (Finland)

CSCS The Swiss National Supercomputing Centre (represented in PRACE by

ETHZ, Switzerland)

CSR Compressed Sparse Row (for a sparse matrix)

CUDA Compute Unified Device Architecture (NVIDIA)

DARPA Defense Advanced Research Projects Agency

DDN DataDirect Networks

DDR Double Data Rate

DEISA Distributed European Infrastructure for Supercomputing Applications.

EU project by leading national HPC centres.

DGEMM Double precision General Matrix Multiply

DIMM Dual Inline Memory Module

DKRZ Deutsches Klimarechenzentrum

DMA Direct Memory Access

DNA DeoxyriboNucleic Acid

DP Double Precision, usually 64-bit floating point numbers

DRAM Dynamic Random Access memory

EC European Community

EEA European Economic Area

EESI European Exascale Software Initiative

EoCoE Energy oriented Centre of Excellence

Eol Expression of Interest

EP Efficient Performance, e.g., Nehalem-EP (Intel)

EPCC Edinburg Parallel Computing Centre (represented in PRACE by

EPSRC, United Kingdom)

EPSRC The Engineering and Physical Sciences Research Council (United

Kingdom)

eQPACE extended QPACE, name of the FZJ WP8 prototype

ETHZ Eidgenössische Technische Hochschule Zuerich, ETH Zurich

(Switzerland)

ESFRI European Strategy Forum on Research Infrastructures; created

roadmap for pan-European Research Infrastructure.

EX Expandable, e.g., Nehalem-EX (Intel)

FC Fiber Channel

FFT Fast Fourier Transform FHPCA FPGA HPC Alliance

FP Floating-Point

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FZJ Forschungszentrum Jülich (Germany)

GASNet Global Address Space Networking

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GCS Gauss Centre for Supercomputing (Germany)

GDDR Graphic Double Data Rate memory

GÉANT Collaboration between National Research and Education Networks to

build a multi-gigabit pan-European network, managed by DANTE.

GÉANT2 is the follow-up as of 2004.

GENCI Grand Equipment National de Calcul Intensif (France)

GFlop/s Giga (= 10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also GF/s

GHz Giga (= 10<sup>9</sup>) Hertz, frequency =10<sup>9</sup> periods or clock cycles per second

GigE Gigabit Ethernet, also GbE

GLSL OpenGL Shading Language

GNU GNU's not Unix, a free OS

GPGPU General Purpose GPU

GPU Graphic Processing Unit

GS Gram-Schmidt

GWU George Washington University, Washington, D.C. (USA)

HBA Host Bus Adapter HCA Host Channel Adapter

HCE Harwest Compiling Environment (Ylichron)

HDD Hard Disk Drive HE High Efficiency

HET High Performance Computing in Europe Taskforce. Taskforce by

representatives from European HPC community to shape the European HPC Research Infrastructure. Produced the scientific case and valuable

groundwork for the PRACE project.

HMM Hidden Markov Model

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hewlett-Packard

HPC High Performance Computing; Computing at a high performance level

at any given time; often used synonym with Supercomputing

HPCC HPC Challenge benchmark, <a href="http://icl.cs.utk.edu/hpcc/">http://icl.cs.utk.edu/hpcc/</a>

HPCS High Productivity Computing System (a DARPA program)

HPL High Performance LINPACK

HT HyperTransport channel (AMD)

HWA HardWare accelerator

IB InfiniBand IB Architecture

IBM Formerly known as International Business Machines

ICE (SGI)

IDRIS Institut du Développement et des Ressources en Informatique

Scientifique (represented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IESP International Exascale Project

IL Intermediate Language IMB Intel MPI Benchmark

I/O Input/Output

IOR Interleaved Or Random

IPMI Intelligent Platform Management Interface

ISC International Supercomputing Conference; European equivalent to the

US based SC0x conference. Held annually in Germany.

IWC Inbound Write Controller

JSC Jülich Supercomputing Centre (FZJ, Germany) KB Kilo (=  $2^{10} \sim 10^3$ ) Bytes (= 8 bits), also KByte

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC,

Sweden)

LBE Lattice Boltzmann Equation

LINPACK Software library for Linear Algebra

LLC

LLNL Laurence Livermore National Laboratory, Livermore, California (USA)

LQCD Lattice QCD

LRZ Leibniz Supercomputing Centre (Garching, Germany)

LS Local Store memory (in a Cell processor) MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (= 10<sup>6</sup>) Bytes (= 8 bits) per second, also MByte/s

MDT MetaData Target

MFC Memory Flow Controller

MFlop/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also MF/s

MGS Modified Gram-Schmidt

MHz Mega (=  $10^6$ ) Hertz, frequency = $10^6$  periods or clock cycles per second MIPS Originally Microprocessor without Interlocked Pipeline Stages; a RISC

processor architecture developed by MIPS Technology

MKL Math Kernel Library (Intel)

ML Maximum Likelihood

Mop/s Mega (=  $10^6$ ) operations per second (usually integer or logic operations)

MoU Memorandum of Understanding.

MPI Message Passing Interface

MPP Massively Parallel Processing (or Processor)

MPT Message Passing Toolkit MRAM Magnetoresistive RAM

MTAP Multi-Threaded Array Processor (ClearSpead-Petapath)

mxm DP matrix-by-matrix multiplication mod2am of the EuroBen kernels

NAS Network-Attached Storage

NCF Netherlands Computing Facilities (Netherlands)

NDA Non-Disclosure Agreement. Typically signed between vendors and

customers working together on products prior to their general

availability or announcement.

NoC Network-on-a-Chip NFS Network File System

NIC Network Interface Controller

NUMA Non-Uniform Memory Access or Architecture

OpenCL Open Computing Language

OpenGL Open Graphic Library

Open MP Open Multi-Processing

ORNL Oak Ridge National Laboratory

OS Operating System

OSS Object Storage Server

OST Object Storage Target

PCIe Peripheral Component Interconnect express, also PCI-Express

PCI-X Peripheral Component Interconnect eXtended

PGAS Partitioned Global Address Space

PGI Portland Group, Inc.

pNFS Parallel Network File System

POSIX Portable OS Interface for Unix

PPE PowerPC Processor Element (in a Cell processor)

PRACE Partnership for Advanced Computing in Europe; Project Acronym

PSNC Poznan Supercomputing and Networking Centre (Poland)

QCD Quantum Chromodynamics

QCDOC Quantum Chromodynamics On a Chip

QDR Quad Data Rate

QPACE QCD Parallel Computing on the Cell

QR — QR method or algorithm: a procedure in linear algebra to compute the

eigenvalues and eigenvectors of a matrix

RAM Random Access Memory

RDMA Remote Data Memory Access

RISC Reduce Instruction Set Computer

RNG Random Number Generator

RPM Revolution per Minute SAN Storage Area Network

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SAS Serial Attached SCSI

SATA Serial Advanced Technology Attachment (bus)

SDK Software Development Kit

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SHMEM Share Memory access library (Cray)

SIMD Single Instruction Multiple Data

SM Streaming Multiprocessor, also Subnet Manager

SME Small and Medium Sized Enterprise

#### D8.3.4 Technical lessons learnt from the implementation of the joint PCP for PRACE-3IP

SMP Symmetric MultiProcessing

SNIC Swedish National Infrastructure for Computing (Sweden)

SP Single Precision, usually 32-bit floating point numbers

SPE Synergistic Processing Element (core of Cell processor)

SPH Smoothed Particle Hydrodynamics

SPU Synergistic Processor Unit (in each SPE)

SSD Solid State Disk or Drive

STFC Science and Technology Facilities Council (represented in PRACE by

EPSRC, United Kingdom)

STRATOS PRACE advisory group for STRAtegic TechnOlogieS

STT Spin-Torque-Transfer

SURFsara Dutch national High Performance Computing & e-Science Support

Center

TARA Traffic Aware Routing Algorithm

TB Tera (= 240 ~ 1012) Bytes (= 8 bits), also TByte

TCO Total Cost of Ownership. Includes the costs (personnel, power, cooling,

maintenance, ...) in addition to the purchase cost of a system.

TDP Thermal Design Power

TFlop/s Tera (= 1012) Floating-point operations (usually in 64-bit, i.e. DP) per

second, also TF/s

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the Tier-0 systems; national or topical HPC centres would constitute Tier-1

UFM Unified Fabric Manager (Voltaire)

UNICORE Uniform Interface to Computing Resources. Grid software for seamless

access to distributed resources.

UPC Unified Parallel C UV Ultra Violet (SGI)

VHDL VHSIC (Very-High Speed Integrated Circuit) Hardware Description

Language

## **Executive Summary**

Energy efficiency is one of the key challenges affecting many parts of the IT industry including High Performance Computing (HPC). The aim of the PRACE joint Pre Commercial Procurement (PCP), between CINECA (Italy), CSC (Finland), EPCC (UK), GENCI (France) and JSC (Germany) was to explore, for the first time in Europe in the field of HPC, to what extent pre-commercial procurement could be used to improve the energy efficiency of general purpose supercomputers capable of running real PRACE production workloads. This is a very challenging aim. The existing HPC marketplace already takes energy efficiency fairly seriously (at least for the largest systems) and many of the requirements for energy efficiency are the same as requirements for high performance. As a result, there were no major inefficiencies in current offerings that the project could address in order to obtain an easy win. In addition, the key technologies that consume most of the energy such as processors and memory are manufactured by large down-stream suppliers with a wide user base and very large R&D costs making them unlikely to be directly influenced by a project of this kind with an overall budget of 9 Mio. EUR, so the project was more targeting a leverage effect.

This project has demonstrated that it is possible to achieve better energy efficiency by relaxing the requirement for a general purpose supercomputer. Better energy efficiency is possible but comes at a cost of either making the system harder to use or only suitable for a smaller range of applications. Usually this is by exploiting some form of accelerator technology. The project explored a number of such architectures including large numbers of low-power cores (Intel KNL processor), GPGPU acceleration and data-flow architectures implemented using FPGAs. The KNL based solution was the most general purpose system. The GPGPU system gave a very good energy efficiency when the application codes supported the GPGPU properly. This is quite an interesting result; though GPGPUs will not be suitable for all types of problem many major application codes now have good support for GPGPUs. The data-flow/FPGA solution demonstrated the potential for even greater energy efficiency in some cases though the effort required to utilise this technology implies code re-writing sections, so such an approach may be better suited to dedicated usages, rather than general purpose systems.

Energy efficient whole HPC solutions requires also energy efficient power supplies and cooling systems. High end HPC system vendors typically include these technologies as part of their standard offering however the rest of the IT industry is still dominated by air-cooled solutions which could limit the potential bidders to procurements that require them. The PRACE PCP has demonstrated that a PCP type mechanism can be used to fund the development of additional products with state-of-the-art power and cooling solutions increasing competition in this area. As matter of fact, vendor roadmaps have been influenced by this PCP as reported in "Impact on vendor roadmap" of Atos-Bull, Maxeler and E4, respectively in 4.5, 5.5 and 6.5.

The project has also demonstrated the potential of energy aware scheduling and whole-system power capping that might be used to allow a system to adjust its operation to fit within local infrastructure power and cooling constraints. This will be also very important tools in a future exascale context were monitoring will be even more complex and critical.

To allow applications to be optimized with respect to their energy use it is essential to have high resolution energy profiling tools that will allow application developers to investigate the energy usage of their applications including sufficient time resolution to distinguish the relative energy usage of different parts of the application. The project has developed a number of powerful tools and instrumentation to allow this to happen, such tools are now expected to become part of the software stacks of the different vendors involved into the PRACE PCP.

#### 1 Introduction

This document collates the technical lessons learned from the PRACE PCP. We start with a review of the aims of the PRACE PCP and the overall technical landscape, as it is relevant to energy efficiency. Lessons are then drawn from each of the pilot systems delivered in the final phase of the PCP. Feedback and experiences from early users of the machines is analysed. Where additional lessons could be drawn, selected systems from earlier stages of the PCP are also considered as well as general lessons that are not specific to any particular system.

## 2 Overview of the PRACE PCP

The PRACE-3IP project performed a Pre-Commercial-Procurement (PCP). A PCP is primarily targeted towards the procurement of R&D services, but allows for a part of the budget to be spent on the procurement of equipment for demonstrating and testing the R&D results. The PRACE PCP was setup with the following technical goals: to procure/develop highly energy efficient HPC systems capable of general use, i.e. able to run real applications, be operated within a conventional HPC computing centre but nevertheless achieve very high total-system energy efficiency. In addition to the technical goals the PCP was also intended to develop the HPC vendor eco-system within the EEA and as such it is expected to result in commercially viable products.

The technical criteria were chosen as they reflect one of the most challenging issues facing the HPC market sector at the moment. It has been well recognised since at least 2008[1] that total energy consumption will be one of the major factors that could inhibit the adoption of Exascale systems. This will also be a major problem for smaller scale HPC systems. Though smaller HPC installations typically only are a fraction of the size of world-leading systems they will also be installed in facilities with only a fraction of the available power. Power consumption is already a significant part of the total cost of ownership of a HPC system. Current HPC procurements frequently consider energy efficiency as part of the evaluation process. The relative weighting of energy efficiency in procurements is expected to increase over time. Energy efficiency is also a major concern of the wider IT industry. At one end of the IT spectrum mobile computing requires high energy efficiency to maximise battery life. At the other end of the spectrum hyper-scale data centres as used by public cloud providers have many technologies in common with the HPC sector and share many of the same power and cooling issues.

The PRACE PCP did not place any restrictions on how energy efficiency was to be addressed. The systems were to be evaluated on total-system energy efficiency so vendors were free to address any aspects of the total system design.

Aligning the goals of the PCP with one of the major issues facing the HPC market sector has a number of results.

• First of all, this ensures that the research and development undertaken as part of the PCP will be commercially relevant. A PCP mechanism could be used to encourage vendors to develop new products to serve new user communities with specialised requirements. In that case it would be beneficial for the R&D activity to be run as codesign to bring together the domain knowledge of the end user with the technical knowledge of the vendor. In this case the vendors should have easily understood the requirements so there was no need for any co-design involving the procuring entities. However, this close alignment with a major issue facing a competitive industry such as IT does make it extremely challenging to make significant technical breakthroughs.

- Much of the energy budget of an HPC system goes towards components such as processors, memory and networks. The scale of the industry sectors that manufacture these is so large that we cannot expect that a €9M PCP to have any significant direct influence over them but we could with some confidence expect them to be addressing energy efficiency in some form. In addition any easily exploitable route to energy efficiency specific to HPC will probably already have been explored by some of the existing HPC vendors.

- This does not prevent the PCP from acting as a mechanism to evolve the vendor ecosystem. Vendors could either have used the PCP as a way to develop new products in order to compete on equal terms with existing major players or to facilitate the development of more novel approaches that have not been adopted elsewhere. However, we have to accept that novel approaches with significant improvements in energy efficiency will probably come at some cost, for example systems that are harder to program or harder to use for some reason. As a result of this any vendor bidding for the PCP had to make an assessment of the market viability of these costs relative to the energy efficiency benefits when designing their solution so we would not expect the same levels of innovation as might be seen in a purely academic research project.

## 3 Technical Background

To be able to increase the energy efficiency of HPC it is necessary to either identify some inefficiency in current implementations that may be addressed or to entirely replace one of the current technologies used with a replacement technology that has a significantly energy cost. A disruptive change in the technologies used by the HPC industry would require significantly more funding than is available within this PCP so it is important to understand the current technical landscape and where inefficiencies might exist that could be exploited to improve overall energy efficiency.

To a first approximation the significant contributors to energy consumption in HPC compute nodes are CPU/logic, memory and data-movement. The CPU consumes the majority of the power. There is some scope within current CMOS technology to optimise for power efficiency. The performance of a processor is roughly proportional to the clock-speed and the degree of parallelism supported by the processor. However, increasing the clock-speed requires an increase in supply voltage and the dynamic power requirements of the processor are roughly proportional to the square of the supply voltage so increasing the clock-speed has a disproportionate negative impact on energy efficiency. Many modern processors support dynamic changes in clock speed allowing the processor to switch between high performance and low energy modes. This is particularly effective for codes that are memory rather than CPU bound where there is less performance advantage to a high clock-speed. Highly energy efficient system designs therefore tend to be characterised by relatively modest clock frequencies and high levels parallelism. In practice the number of applications that can effectively utilise very large numbers of low performance nodes is limited so most recent designs use a combination of node-based, thread-based and instruction-level (SIMD/vector) parallelism. SIMD/vector architectures may also be more energy efficient for HPC workloads because a higher proportion of the circuitry is used for implementing floating point pipelines, and hence the power budget is dedicated to floating point calculations than is the case for general purpose processor designs. On the other hand the investment needed to bring a new CPU (or even a customised version of an existing one) to market is huge, significantly greater than the research component of the PCP so at most the PCP could only influence the selection of components from existing available devices rather than result in any form of novel low energy processor design.

Currently the main memory in all commercial HPC systems utilises some form of Dynamic Random Access Memory (DRAM). DRAM memory cells only retain their information for a limited period of time before the charge in the capacitor leaks away losing the information. Therefore DRAM cells need to be refreshed periodically by the memory controller. DRAM is a particularly cost effective technology with respect to storage capacity; the storage cells are extremely simple as each bit of storage only requires a single transistor and a capacitor to implement. This means that DRAM requires significantly fewer manufacturing steps than processor logic and can be manufactured at low cost. However, this cost advantage is removed if the DRAM cells are manufactured on the same wafer as the processor or any other complex logic so the memory controller is an external device (usually part of the processor). Though not the largest energy cost in a HPC system DRAM does consume a significant part of the overall energy budget most of this being data-movement between the DRAM chips and the processor itself. The simple constructions of DRAM chips means that the memory interfaces use fairly simple electrical interfaces, which are not particularly energy efficient. One significant technological change within the timescale of the PCP is the introduction of 3D stacked memory. Though still a form of DRAM the packaging is radically different. Previously DRAM chips were packaged as individual devices mounted on memory DIMMs and connected to the processor through the motherboard. With stacked memory a 3D stack of memory chips is constructed. The majority of the thickness of the silicon wafer is removed during manufacture to allow a large number of electrical connections to be manufactured through the body of the chip giving a very high degree of connectivity within the stack and therefore supporting greater parallelism and high bandwidth throughput. These through-chip connections are called Through-Silicon-Vias (TSVs). In additional this memory stack is installed in-package very close to the processor or memory controller. Though the primary motivation for 3D stacked DRAM is increased performance the much shorter communication distances may result in improved energy efficiency compared with conventional DRAM. One technology that follows this approach is HBM (High Bandwidth Memory), which is standardised by JDEC since 2013. An alternative architecture (used by the Micron Hybrid Memory Cube) is to use a separate memory controller (again closely coupled with the DRAM stack) connected to the processor using high-speed-serial communication links. This architecture is also more energy efficient than convention DRAM and more flexible than directly connected HBM but at the cost of additional memory controller devices.

Data movement is one of the major consumers of energy in HPC systems. All current interconnects use the same underlying technologies. Though there are many different network products available the lowest level implementations (the physical transport layer of the OSI networking model) are essentially the same for all products. Over short distances electrical connections over copper cables are used, these are implemented over high speed serial links. The cost (both manufacturing costs and energy costs) of this technology are roughly proportional to the length of the connection. Over longer distances optical connections over fibre optic cables are used. In this case the costs (again both in terms of manufacturing and energy costs) are concentrated in the optical transceivers and are largely independent of distance so optical communications are the preferred technology over longer distances. The fundamental design principles of HPC networks are therefore very similar when optimising for manufacturing or energy costs. At most the optimal cross-over distance between electrical and optical communications might be different in an energy optimised design.

\_

<sup>&</sup>lt;sup>1</sup> https://www.jedec.org/document\_search?search\_api\_views\_fulltext=jesd235

The long term trend in interconnect technologies has been for the optimal electrical/optical cross-over distance to become shorter over time. There are significant R&D investments in silicon-photonics which have the potential to eliminate the copper cables entirely and connect fibre directly to silicon. This is a promising and potentially disruptive technology however, it is still in the research phase with some fundamental issues still to be resolved so it is not easy to predict a timescale when it might cross over into commercial products. When and if it does become available it may open up opportunities for innovative energy efficient designs.

Minimising the use of inter-node communication is a key part of parallel application performance the same optimisations used to improve performance and parallel scaling of applications are also those needed to improve the energy efficiency of the applications communications. Therefore we don't expect any major energy inefficiencies in the way that major HPC applications structure their inter-node communications.

Depending on the application there may be greater scope for energy efficiency improvements in data movement within memory systems. HPC applications are typically written to perform well in a memory hierarchy containing layers of cache memory. In this case good performance relies on ensuring a high proportion of cache hits rather than minimising the total amount of memory traffic. Techniques such as pipelining and pre-fetching allow the performance cost of memory accesses to be hidden by overlapping them with other operations but this does nothing to minimise the energy costs.

When using GPUs there is an additional time and energy cost in moving data between CPU and GPU memory. However, as this impacts performance as well as energy use well optimised GPU codes will already have been re-written to minimise these data movements. This is another reason why GPU systems may exhibit good energy efficiency.

Data-flow computers (as represented in the PCP by the Maxeler system) also attempt to minimise data movement. The aim of a data-flow system is to use re-configurable hardware to implement key computational kernels as a single pass through the data. Any data elements that are re-used within the kernel are retained in internal buffers until no longer needed.

The three pilot systems deployed by the PCP demonstrated three different responses to this technical landscape:

- The Intel KNL processor is an example of a many-core design using a large number of relatively simple CPU cores supplied with wide SIMD vector units. These therefore support a very high degree of parallelism with a large part of the available circuitry implementing the floating-point operations needed by HPC applications. This together with the 3D-stacked memory had the potential to improve energy efficiency while staying within the standard programming model of existing HPC systems to preserve the general-purpose nature of the solution.

- The NVIDIA P100 GPU accelerator uses 3D-stacked HBM2 and also uses wide vector instructions and high core counts internally. Using a GPGPU effectively requires a large application software investment. However the growing number of improving programming models has gained significant traction in recent years and large numbers of important HPC applications already support GPGPUs to some extent and there are a large number of existing application software engineers with the necessary skills.

- Using FPGAs to build application specific accelerators gives great flexibility to match circuit implementation to the requirements of the application. Constructing these accelerators as data-flow computers removes unnecessary memory traffic. However as with GPGPUs this requires a large application software investment and data-flow accelerators have not achieved the same market penetration as GPUs.

## 4 Lessons learned from the Atos-Bull KNL pilot system

#### 4.1 Description of the system

#### 4.1.1 System description

The Atos-Bull pilot system hosted by GENCI at CINES in Montpellier (France) has been deployed on Friday 14 April 2017. Hardware installation including cabling, powering and pipe connections was then finalized on 20 April 2017. The pilot system's hardware architecture is based on a standard Bull Sequana X1000 cell improved with specific PCP developments providing water cooled power supplies becoming the first installation with 100% water cooled racks.

For this PCP, Atos-Bull made the choice to use the last generation of Intel Xeon Manycore ("Knights Landing") architecture (also known as Intel Xeon Phi) and especially the Intel 68-core 7250 and Mellanox InfiniBand EDR interconnect.

Figure 1: Sequana Cell view

A complete Sequana cell has been installed equipped with 56 Atos-Bull Sequana X1210 Intel Xeon Knights Landing (KNL) blades, providing a total of 168 compute nodes.

Each KNL blade contains three KNL nodes, and each compute node is equipped with:

- 1x Intel Xeon-Phi Knights Landing 7250 16GB HBM MCDRAM 215W,

- 6x 16GB@2400MT/s DDR4 DIMMs,

- 1x 240GB 2.5" 7mm SATA3 SSD,

- 1x InfiniBand 4x EDR mezzanine board to connect one 100Gb/s link to the first level of fat-tree in switch rack,

- 1x HDEEM (High Definition Energy Efficiency Monitoring) FPGA to provide accurate and high frequency power measurement. This component is key for the PCP project.

Figure 2: Sequana KNL blade with 3 KNL nodes

The high-speed interconnect is designed through a Mellanox InfiniBand EDR Fat Tree topology with a 2:1 blocking factor.

Storage facilities access is granted through direct connections to the InfiniBand fabric and existing data management solutions relying on Lustre or PanFS file systems and accessed through routers.

On the pilot system, MooseFS has been deployed as parallel and highly performing file system. It spreads data over all local disk of each compute nodes (chunk servers), which are visible to the user as one virtual disk. MooseFS is compliant and acts like any other Unix-like file system supporting:

- Hierarchical structure: Files and Folders;

- File attributes:

- Special files: Pipes, Sockets, Block and Character devices;

- Symbolic and Hard links;

- Security attributes and ACLs.

With this solution, it was demonstrated an IO throughput of 30 GB/s in both write and read using IOR benchmark.

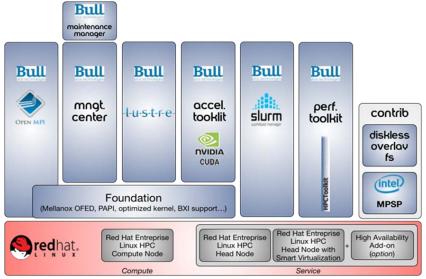

#### 4.1.2 Software environment

The Bull HPC software solution includes core components that provide tools, libraries and APIs to fulfil expectations of each kind of user:

- Administrators needing to install, configure and monitor all the physical and logical components of the solution to ensure maximum availability and performance,

- Developers needing tools to develop, and then manage code, analyse and tune applications;

- End-users needing efficient submission mechanisms and highly performing communications libraries.

The Bull Super Computer Suite version 5 (SCS 5) has been designed to address these different needs with simplicity and efficiency, maximizing stability of operational conditions and applications performance. Its main goals are to offer a set of autonomous components that can be used all together to create a complete solution, and to provide:

- a high-performance software environment for the supercomputer;

- an easy installation and modular update paths;

- the integration of hardware add-ons;

- quick security fixes;

- the support for several development environments;

• and an all-in-one solution for validating the system architectures whatever the size of the computer.

Based on selected foundation components, the hierarchical approach for managing thousands of equipment has been engineered and implemented to offer a scalable and easy-to-use environment. This solution is a completely new approach offering high level of resiliency and flexibility, from the installation to the day-to-day operations.

Figure 3: SCS5 Components

The Bull SCS 5 is based on a set of components that aim to provide software solution for different purposes on a HPC system. All those components are validated and built to perform at their maximum on a Red Hat Enterprise Linux HPC operating system.

- Bull Foundation

- Bull Management Center

- Bull Maintenance Manager

- Bull Lustre

- Bull SLURM

- Bull OpenMPI

- Bull Performance Toolkit

- Bull Accelerator Environment (NVIDIA CUDA)

The Bull SCS5 release 1 has been installed on the Pilot PCP. This release doesn't include any prototype of the tools developed during the PCP. However, such tools will be integrated into the next release of the solution.

#### 4.1.3 Energy efficiency aspects of the design

#### Technology related

The Atos-Bull Sequana concept: The Sequana integration has a Power Usage Effectiveness (PUE) ratio of very close to 1 and energy consumption 10 times lower than the previous generation of supercomputers. With Sequana, 100 percent of the components - including compute nodes, power supplies and switches - are cooled using an enhanced version of the patented Atos-Bull Direct Liquid Cooling (DLC) technology. The second generation DLC solution is a proven cooling solution that minimizes a system's global energy consumption by using warm water at up to 40° C. This is an enhanced version of the proven DLC technology

#### D8.3.4 Technical lessons learnt from the implementation of the joint PCP for PRACE-3IP

in the Bullx DLC cabinets used with B700 series and already deployed at many large HPC sites, including DKRZ in Germany and Météo France.

The Sequana platform is an energy-aware system that integrates fine-grain energy sensors and a new generation of the High Definition Energy Efficiency Monitoring (HDEEM) technology to facilitate energy optimization.

Through these innovations, the Atos-Bull Sequana X1000 provides the following features:

- The lowest TCO and carbon footprint of any regular supercomputer available today;

- Enables power-aware scheduling to ensure that applications run as cost effectively as possible without compromising performance.

DLC minimizes the total energy consumption of a system because cooling is achieved with inlet water as warm as  $40^{\circ}$  C. Sequana X1000 is designed to support very powerful and energy-hungry nodes. In combination with peripherals placed in racks with water-cooled doors, this means that the proposed solution can extract more than 100 percent of the heat generated by the solution and do so with year-round free cooling. As an option, the DLC solution can be used to cool machine room air.

Sequana X1000 DLC solution is sized to evacuate the heat generated in compute nodes and BXI or EDR/HDR switching components, even with the most extreme configurations. Uniquely, it also use direct liquid cooling on the power supply units (PSUs); this capability enabling to extract the final 10 percent of heat generated by the system to water.

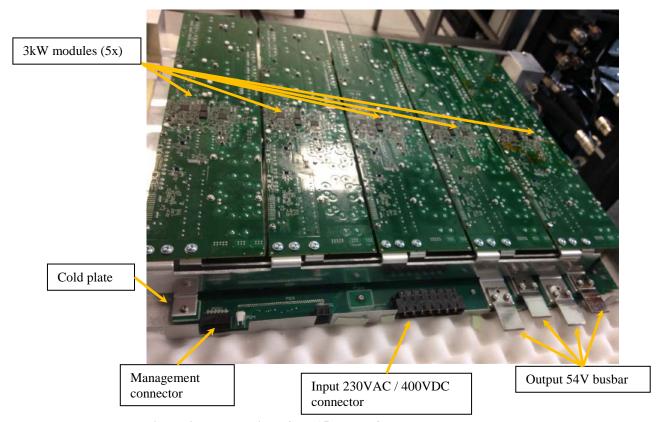

Water cooled Power Supply Units (PSU): In the initial Bull Sequana design, PSU were air-cooled and represented around 8% of total cell dissipation. During PCP phase II, a new PSU has been developed for PSU heat direct capture. Bull has first selected one partner "Brightloop Converters", a French SME specialized in high efficiency power converters, for the co-development of this PSU and the power shelves compatible with Sequana.

The objective is the full integration of two types of power shelves cooled by hot water in Sequana. Shelves will deliver up to 15,000 Watt of power at high performance capability and precise consumption measurement falling within the latest standards of the Green500<sup>2</sup>.

The validation tests of the 12 kW sWitch Power Shelf Module (WPSM) and 15 kW Compute Power Shelf Module (CPSM) are shared by Bull and its partner. The main focus for Bull in Phase III is the integration in Sequana and the validation of final solution.

The two shelves (12 kW and 15 kW) are based on the assembly of 3kW individual convertors, thermally drained to a cold plate via the use of internal heat spreaders. Each 3 kW module contains its own fuse, PFC (Power Factor Corrector) stage, and a LLC resonant converter<sup>3</sup>, to transform the input 230 VAC or 400 VDC to the main 54 V output.

These modules are mounted on a cold plate, and a backplane is used to interconnect them together and to the output connectors. An internal view of the 15 kW shelf is shown below. The 12 kW shelf is based on the same concept, except that it hosts only 4 modules, and that the external connectors are not located at the same place (and are different for the 54 V output).

<sup>&</sup>lt;sup>2</sup> http://www.green500.org

<sup>&</sup>lt;sup>3</sup> Resonant converters are a type of electric power converter that contains a network of inductors (L) and capacitors (C). LLC resonant converts are resonant converters with a specific topology and based on two inductors and one capacitor.

Figure 4: Internal view of the 15kW shelf

In each module, a dedicated DSP is used to control the primary side of the 3 kW module (PFC stage), and a second one is used for the secondary side (LLC stage). They are in charge of the regulation of the stage they are associated with. All DSP modules are managed by an additional DSP located on the shelf backplane. This last DSP (management DSP) is responsible for the management of the shelf, including power ON/OFF operation, monitoring, current sharing, and firmware upgrade. It communicates with the DSPs of the individual modules through a CAN bus, and with the rack power controller (PMC) through an I2C bus.

The required efficiency is higher than 94% at full load, which makes the shelf 80-Plus platinum certified.

The FAST\_PROCHOT\_N feature is handled at the shelf level by the management DSP, which asserts this signal low when the output power of the shelf exceeds 130% of its rated load. This is done very quickly (less than 100µs) so that the CPU can react fast enough (by reducing their drawn power) to avoid the PSU entering over power protection and shutting down.

To allow support for a local power backup source (ultra-capacitor modules) in case of short outages (up to 300 ms at full load, or 800 ms at half load), the shelf is required to restart in less than 150 ms upon input voltage recovery. Good load sharing and error handling is needed during this phase, so that no PSU exceeds its rated power, or enter any protection, while taking into account the tolerance in start time between all PSU of a same output rail (up to twenty 3 kW modules, e.g. 4 shelves).

Input power is monitored, at the shelf level, by the management DSP. It is based on the output power reported by dedicated sensors in each 3 kW module, and calculated using a pre-set look-up table to include the shelf efficiency. This one is characterized for different input voltages and temperatures conditions. The reported value is then filtered over a 100ms period of time. The obtained precision is required to be better than +/-3%, for loads ranging from 50% to 100% of full load.

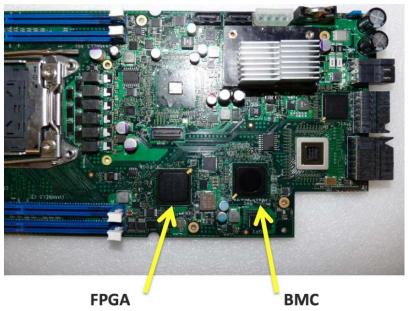

Infrastructure for Energy monitoring and optimization

During this project, different prototypes of energy efficiency oriented tools and products have been developed. On the hardware side, Atos-Bull Sequana blades provide accurate power consumption measures at a high frequency embedding the High Definition Energy Efficiency Monitoring (**HDEEM**) technology developed by Atos-Bull.

Figure 5: HDEEM board

More precisely, HDEEM provides

- a **sampling rate** up to:

- o 1 kHz for global power including sockets, DRAM, SSD and on-board,

- o 100 Hz for voltage regulators,

- And with an **high accuracy** with 2-5% of uncertainty after calibration,

- o 2% for blades.

- o 5% for VR.

- Different **collection modes** are available,

- o Out-of-band using BMC (4 Hz),

- o In-band through HDEEM API (eg SLURM).

One challenge of this PCP project was to develop tools able to collect HDEEM results as well as metrics coming from other components of the Sequana cells (switches for instance) and provide consolidated views of either jobs power consumption (for users) or the full system power consumption (for system administrators). As a result, the following components have been designed and developed within the PCP:

- Bull Energy Optimizer (**BEO**): Energy measurement tool that provides information on the whole system, which is non-intrusive, and provides 100 Hz sampling and 3-5% precision,

- **HDEEViz**: Power consumption visualization tool,

- Energy oriented **SLURM** plugin based on adaptive scheduling,

- Bull Dynamic Power Optimizer (**BDPO**): Energy optimization tools able to dynamically adapt runtime parameters to save energy without significant impact on the execution time.

#### **Description of the BEO component**

The energy measurement sub-system that is integrated into the Pilot System relies on a new product that will be available in the Bull SCS 5 software suite. This product, Bull Energy Optimizer (BEO), is a software product dedicated to power management for HPC clusters.

Bull Energy Optimizer was originally referred as "Power Manager" module in the technical offer of phase III.

The various use cases that BEO aims at addressing can be grouped into four broad categories:

- Collecting data related to power consumption;

- Supporting diagnosis activities such as understanding the mechanisms that leads to a given power consumption level, or being able to identify where power is actually consumed;

- Predicting the behaviour of the system from the analysis of statistic data, depending on the run-time system configuration and application deployment options;

- Prescribing configuration changes according to power management policies, based on power consumption models.

This version of BEO addresses the two first use cases, it focuses on the descriptive aspects: being able to carefully monitor power and energy consumption, alerting when metrics thresholds are exceeded.

In future versions, BEO will include Predicting and Prescriptive actions. BEO will also include dynamic power optimizations features, where run-time environment can be automatically changed according to specific power consumption targets & power management policies.

#### BEO main features are:

- Providing power and energy consumption information related to any subset of the cluster. Such a subset is defined as a managed container that can group Compute Nodes, Switches, Chassis, Racks, Islets, and Cluster;

- Providing energy consumption related to any set of SLURM jobs;

- Providing alerting functionality based on thresholds definition on a given set of metrics (ex: power limit for a set of hardware);

- Providing the ability to report energy costs, based on a configured description of power costs;

- Providing data as time series for a set of metrics;

These features are delivered as a Command Line Interface (CLI). Next releases will contain a REST API as well as a Graphical User Interface (GUI).

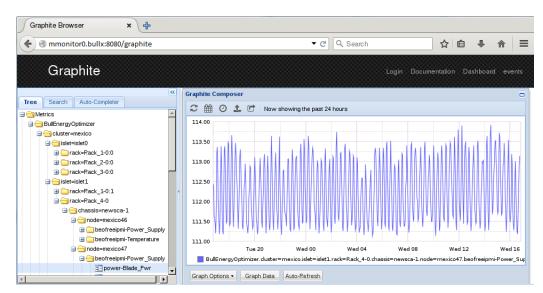

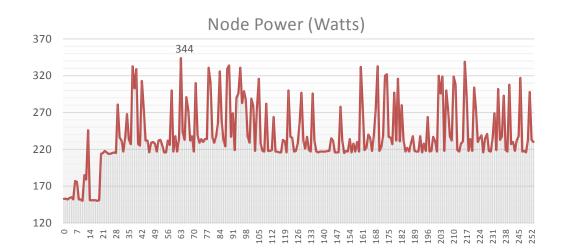

Additionally, it is possible to use the graphite Web interface to obtain a visual representation of the metrics via graphite/carbon. The following figure shows an example of the evolution of power metrics for a compute node:

Figure 6: Evolution of power metrics for a compute node

Today, it is possible to dynamically optimize the performances of an application through the software prototype named Bull Dynamic Performance Optimizer (BDPO).

Bull Energy Optimizer manages the information related to the power consumed in a supercomputer. It relies on metrics managed by graphite.

The infrastructure allowing the collection and the storage of the metrics is available via the SCS5 Metrics component of Bull SCS 5. Only a complementary configuration is necessary to process new power-related metrics.

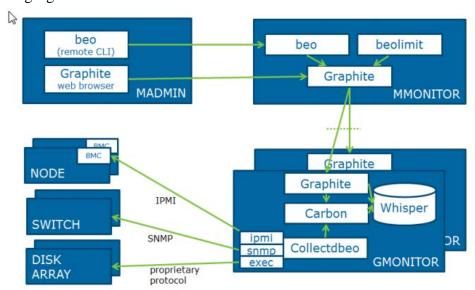

The following figure shows the architecture of the metrics framework:

Figure 7: Architecture of the metrics framework

Power-related metrics are collected on Island management nodes using a dedicated collectdbeo service for the equipment in its scope.

Metrics data are stored locally in whisper database files.

The top management nodes do not store any data, but consolidates information on-demand from the different island management nodes.

Bull Energy Optimizer needs the following services to operate:

• On Top management nodes:

- o httpd;

- o postgresql.

- On Island management nodes:

- o httpd;

- o carbon-cache-a;

- o collectdbeo (installed by Bull Energy Optimizer).

#### **Description of the BDPO component**

BDPO objective is to complete BEO (Bull Energy Optimizer) software with the capability to dynamically adjust the software and hardware resources' runtime settings for energy efficiency, based on the identification of the phases of the executed application. By doing so, BDPO aims at optimizing the energy consumption associated with the execution of an application, without degrading the performances of the latter.

To summarize the main objectives of Atos-Bull were the following:

- Target real HPC applications, thus not limited to simple benchmarks, and running on large clusters

- No, or limited, requirement for a preliminary knowledge of the application:

- o Limit extensive off-line profiling.

- No code annotation;

- No code modification:

- Works with all kind of applications (MPI, OpenMPI, Mixed MPI/OpenMP, ...)

- No, or limited, performance degradation:

- o Energy reduction not done with the cost of severe performance degradation;

- o Keep execution time under control.

- Multi-platform (mainly Xeon and Xeon Phi architectures) (GPU not targeted yet)

BDPO has two main features: Profiler and Optimizer.

- The Profiler feature can be used to carefully follow different metrics and study applications behaviour. However, its main goal is to provide enough information for the Optimizer feature to know how and when change resources' configuration according to the different applications' phases.

- The Optimizer is acting on CPU frequencies.

- o BDPO is able to follow three different metrics:

- o CPU: Hardware performance counters (libpfm+perf\_event interface):

- Compute intensity: IPC (instructions/cycle);

- Memory intensity: out-of-core memory traffic (on Haswell architecture only).

- o File system: Lustre statistics:

- Number of read and written bytes.

- o All the collected metrics, as well as the events (crossed thresholds, decisions taken by the tool), are dumped into log files. This allows to study BDPO behaviour offline after a run of the application.

#### **Description of the HDDEViz component**

HDEEViz stands for "High Definition Energy Efficiency VIsualiZation" and aims to provide a visualization framework for users to access power consumption profiling of their application. Such profiling is allowed by HDEEM (High Definition Energy Efficiency Monitoring) library at a sampling of 1 kHz.

An example of the interface is shown on the next figure:

Figure 8: Example of energy visualization

Priority was given to the non-intrusive property for HDEEViz, as well as portability and ergonomic.

- The current visualization tool chosen is Grafana: this choice is motivated by its portability and ease of use. Grafana is accessible on every web browser and offers ergonomic use to create graphics. This choice is reinforced by the "hands on" session in EoCoE workshop, where users had good comments on Grafana interface.

- InfluxDB is the current data basis used to store the energy consumption data. This is motivated by InfluxDB portability and maintainability.

- HDEEViz automates the trigger of power consumption data by using HDEEM library. It then synchronizes the energy consumption data and fills a time-series database (currently InfluxDB). It then provides a direct access for users to the Grafana dashboard result.

On the user side, three steps are needed for users to access to power consumption graphics:

- 1. Add to your job script the HDEEViz module load and call to the tool,

- 2. Connect to Grafana server through a Web Browser,

- 3. Visualize

HDEEViz requires SLURM resources job management software. The srun launcher is used and is currently the only one available.

However, HDEEViz does not requires any SLURM specific configuration. As HDEEViz uses HDEEM library, one must ensure that HDEEM is installed and running on all compute nodes. (Three functions used: startHdeem, clearHdeem, printHdeem). HDEEViz also needs python to be installed on the compute nodes with a list of modules that must be available.

Installation of HDEEViz then only consists in an archive of files that must be on a directory on a shared file system where you want to install HDEEViz. In the context of PCP, HDEEViz is installed on a management node that is dedicated to energy software only.

The supercomputer must have a Web browser available for users able to connect to node where Grafana is running. It is advisable to have client-server software allowing fast rendering like X2Go. This implies that the supercomputer must be equipped of a visualization node either.

Specific development on the SLURM resource manager

A first version of power adaptive scheduling was already pushed into SLURM open-source in the latest 15.08 version. This scheduling is based on centralized mechanism to dynamically reduce the number of resources available for users and low down the power of nodes when launching new jobs. The two main mechanisms used to get this are the dynamic CPU frequency scaling, to decrease the power of nodes, and shutdown of nodes, to reduce the number of resources. This technique allows defining in advance time windows with specific power limits.

In addition, the energy fair sharing technique allows scheduling jobs depending on users' past energy usage. Based on classic fair sharing, this scheduling technique adds the past jobs energy consumption to CPU-time on the calculation of priority.

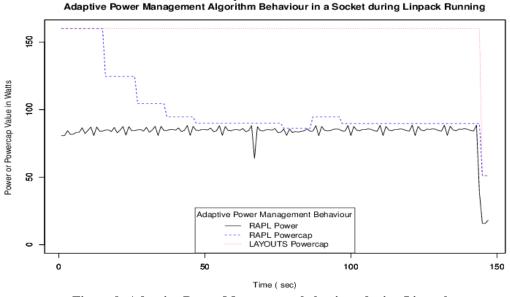

In this project, the focus was put on a new algorithm based on adaptive power management. Instead of fixing the power limit for the execution of jobs, the power adaptive mechanism adapts the power consumption limit during the execution.

The adaptation algorithm for power/RAPL plugin is at the level of sockets, so the adaption is at the fine-grained level. RAPL plugin power adaption is based on the step by step decrease or increase algorithm, so the real power consumption should not be updated immediately, but in the short span of time it should closely follow the application power consumption. The rate of increase, decrease and which criteria (threshold value) to increase or decrease are based on the configuration information, and it depends on the cluster and user behaviour. The behaviour of the powercaping on one socket depending on the real usage of power usage is graphically visualized in the following figure.

RAPL and Layouts information to visualize

Figure 9: Adaptive Power Management behaviour during Linpack

Since power is allocated close to the application behaviour then the unutilized power of one job should be given to another job to improve system utilization and should reduce waiting time of jobs. In the previous figure, the area between red and blue dotted lines is the unutilized power of the currently running job that should be given to other jobs, which are running in the system or waiting in the queue to reduce job waiting time and improve system utilization rate.

## 4.2 Suitability for general purpose HPC

#### 4.2.1 Ease of code development and porting

Both the porting and optimization exercise helped to evaluate and to foresee potential software and programmability issues introduced by the new processing architecture considered. The programmability and in particular the ease of programming is one of the key of the adoption of the technology by end users, keeping the "Ninja Gap" under control.

For some authors, in many ways, the hardware industry's shift toward parallelism has occurred much faster than the abilities of the software and systems designers to react. Technology provider such as Atos-Bull knows how to build complex multi-core processors or SoC, and we must build them to keep Moore's Law rolling along. But there is still issues on how to program them efficiently — both in terms of software development time and in terms of getting the best power-performance outcomes from them. Furthermore, the shift toward on-chip accelerators offers even greater programmability challenges. Finally, there are a host of programmability concerns that emanate from the basic goal of elevating power to a first-class design constraint alongside performance. For example, from a power perspective, information on the relative criticality of different communication or computation operations may be very useful, but current programming models offer few abstractions or constructs to help programmers manage this. This is clearly a strong challenges that technology provider are facing on today.

Atos-Bull made the choice of the Intel Xeon manycore architecture because of the promising FLOP/s per Watt ratio, but also because its architecture is derived for the x86 architecture. This is a great advantage of such architecture, in terms of knowledge, support and ecosystem.

All the codes have been ported without specific effort. Of course, some issues have been experienced, but not directly linked with the ISA itself. All the porting recipes have been detailed in the Atos main deliverables for Phase III of this project, and all source, makefiles, running scripts have been provided to the assessment committee.

To extract the maximum performance of the Intel KNL, one can start with two fundamental considerations: *scaling* in one hand and *vectorization & memory usage* in the other hand; therefore, the developers have to consider for optimizing their applications:

- **Hybrid programming**, mixing MPI and OpenMP. MPI has to be of course privileged for inter-socket communication whereas OpenMP (or threads) has been used intrasocket. The balance between the number of MPI tasks and the number of threads per tasks is highly depending on the OpenMP scalability of each application. For its part, the number of MPI threads per socket is limited by the footprint of the replicated data set and for the footprint of the MPI process itself. Question of the use of multithreading is also a key component of the performance, helping to mask the latency of memory accesses.

- **Vectorization**, through AVX-512 instruction set. Each KNL cores support two FMA 512-bits SIMD vector engine, leading to a core performance of 32 operations per cycle in double precision (64-bits). To exploit this computational power, code must be vectorised. Auto-vectorization done by the compiler itself is generally not sufficient; developers must re-write some data structures to enable vectorization, add also some compilation hints inserting compiler's pragmas or use intrinsic instructions. The codes could also benefit from vectorization using highly optimised library like mathematical core or kernel libraries.

- Optimize memory usage and especially the MCDRAM (fast memory). In order to

obtain decent performance, it is supposed that most of the usable data fits this fast

memory. It requires working on the data memory prefetching and data blocking to improve the spatial and temporal data locality.

## 4.2.2 Energy monitoring/prediction