### SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

## INFRA-2012-2.3.1 – Third Implementation Phase of the European High Performance Computing (HPC) service PRACE

#### PRACE-3IP

## **PRACE Third Implementation Phase Project**

**Grant Agreement Number: RI-312763**

# D7.2.2 Exploitation of HPC Tools and Techniques

#### **Final**

Version: 1.1

Author(s): Michael Lysaght, ICHEC

Bjorn Lindi, SIGMA-NTNU

Vit Vondrak, VSB

John Donners, SURFSARA Marc Tajchman, GENCI-CEA

Date: 20.11.2014

## **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-312763                                                               |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------|--|--|--|--|

|               | Project Title: PRACE Third Implementation Phase Project                                 |  |  |  |  |

|               | Project Web Site: <a href="http://www.prace-project.eu">http://www.prace-project.eu</a> |  |  |  |  |

|               | <b>Deliverable ID:</b> < 7.2.2>                                                         |  |  |  |  |

|               | <b>Deliverable Nature:</b> <report></report>                                            |  |  |  |  |

|               | Deliverable Level: Contractual Date of Delivery:                                        |  |  |  |  |

|               | PU 31 / 05 / 2014                                                                       |  |  |  |  |

|               | Actual Date of Delivery:                                                                |  |  |  |  |

|               | 31 / 05 / 2014                                                                          |  |  |  |  |

|               | EC Project Officer: Leonardo Flores Añover                                              |  |  |  |  |

<sup>\* -</sup> The dissemination level are indicated as follows: **PU** – Public, **PP** – Restricted to other participants (including the Commission Services), **RE** – Restricted to a group specified by the consortium (including the Commission Services). **CO** – Confidential, only for members of the consortium (including the Commission Services).

#### **Document Control Sheet**

|            | Title: Exploitation of HPC Tools and Techniques |                          |  |  |

|------------|-------------------------------------------------|--------------------------|--|--|

| Document   | ID: D7.2.2                                      |                          |  |  |

|            | Version: <1.1>                                  | Status: Final            |  |  |

|            | Available at: <a href="http://wv">http://wv</a> | vw.prace-project.eu      |  |  |

|            | <b>Software Tool:</b> Microso                   | ft Word 2007             |  |  |

|            | <b>File(s):</b> D7.2.2.d                        | ocx                      |  |  |

|            | Written by: Michael Lysaght, ICHEC              |                          |  |  |

| Authorship |                                                 | Bjorn Lindi, SIGMA-NTNU  |  |  |

|            |                                                 | Vit Vondrak, VSB         |  |  |

|            | John Donners, SURFSARA                          |                          |  |  |

|            |                                                 | Marc Tajchman, GENCI-CEA |  |  |

|            |                                                 |                          |  |  |

|               | I v n d v n n n n n n n n n n n n n n n n |

|---------------|-------------------------------------------|

| Contributors: | I Bethune, EPCC                           |

|               | F Reid, EPCC                              |

|               | C Basu, SNIC-LiU                          |

|               | S-H Ko, SNIC-LiU                          |

|               | C Moulinec, STFC                          |

|               | Y Fournier, EDF                           |

|               | B Benek Gursoy, ICHEC                     |

|               | H Nagel, NTNU                             |

|               | A Kwiecien, WCSS                          |

|               | M Uchronski, WCSS                         |

|               | M Gebarowski, WCSS                        |

|               | S Szkoda, WCSS                            |

|               | Z Koza, IFT                               |

|               | M Tykierko, WCSS                          |

|               | P Nolan, ICHEC                            |

|               | A McKinstry, ICHEC                        |

|               | J-C Meyer, NTNU                           |

|               | C Ozturan, Bogazici                       |

|               | S Soner, Bogazici                         |

|               | A Ronovsky, VSB                           |

|               | T Karasek, VSB                            |

|               | D Horak, VSB                              |

|               | · ·                                       |

|               | P Petkov, NCSA                            |

|               | I Todorov, STFC                           |

|               | D Grancharov, NCSA                        |

|               | N Ilieva, NCSA                            |

|               | E Likova, NCSA                            |

|               | L Litov, NCSA                             |

|               | S Markov, NCSA                            |

|               | A Duran, ITU-UHeM                         |

|               | S Celebi, ITU-UHeM                        |

|               | S Piskin, ITU-UHeM                        |

|               | M Tuncel, ITU-UHeM                        |

|               | A Abdel-Rehim, CASTORC                    |

|               | G Koutsou, CASTORC                        |

|               | C Urbach, University of Bonn              |

|               | G V Demirci, Bilkent                      |

|               | A Turk, Bilkent,                          |

|               | R Oguz Selvitopi, Bilkent                 |

|               | K Akbudak, Bilkent                        |

|               | C Aykanat, Bilkent                        |

|               | T Ponweiser, JKU                          |

|               | P Jovanovic, IPB                          |

|               | T Arslan, NTNU                            |

|               | J Rodriguez, BSC                          |

| Reviewed by:  | David Vincente, BSC                       |

|               | Thomas Eickermann, JUELICH                |

| Approved by:  | MB/TB                                     |

| 11            | ı                                         |

## **Document Status Sheet**

| Version | Date       | Status        | Comments               |

|---------|------------|---------------|------------------------|

| 0.1     | 11/05/2014 | Draft         | First draft for PMO    |

|         |            |               | review                 |

| 1.0     | 24/05/2014 | Final version | PMO Review comments    |

|         |            |               | addressed              |

| 1.1     | 20/11/2014 | After review  | Broken references      |

|         |            |               | corrected after review |

|         |            |               | prior to publication   |

#### **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure |

|------------------|-------------------------------------|

|                  |                                     |

#### Disclaimer

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° RI-312763. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2014 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-312763 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

## **Table of Contents**

| Proj | ject and Deliverable Information Sheet                                                                                          | i   |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Doc  | ument Control Sheet                                                                                                             | i   |

| Doc  | ument Status Sheet                                                                                                              | iii |

| Doc  | ument Keywords                                                                                                                  | iv  |

| Tab  | le of Contents                                                                                                                  | v   |

| List | of Figures                                                                                                                      | vi  |

|      | of Tables                                                                                                                       |     |

|      | erences and Applicable Documents                                                                                                |     |

|      | of Acronyms and Abbreviations                                                                                                   |     |

|      | •                                                                                                                               |     |

|      | cutive Summary                                                                                                                  |     |

| 1    | Introduction                                                                                                                    |     |

|      | 1.1 The Purpose of the document                                                                                                 |     |

|      | 1.2 Organisation of Work                                                                                                        |     |

|      | 1.3 Structure of the Document                                                                                                   |     |

|      |                                                                                                                                 |     |

| 2    | Programming Models                                                                                                              |     |

|      | 2.1 Porting CP2K to Intel Xeon Phi with mixed-mode MPI/OpenMP in native mode                                                    | 7   |

|      | 2.2 Exploiting MPI 3.0 One-sided Communication for enabling Code_Saturne on Multi-<br>petaflop/Exascale systems                 | 8   |

|      | 2.3 Evaluation of the Effectiveness of OpenACC for enabling DL_POLY_4 on the Road to Exa<br>10                                  |     |

|      | 2.4 Enabling CP2K for Exascale with OpenACC/OpenCL                                                                              | 12  |

|      | 2.5 Enabling the Cellular Automata Library for Exascale with OpenACC                                                            | 14  |

|      | 2.6 Preparing Coupled Climate Models for Exascale: OpenACC-enabled EC Earth3 Earth Sy Model                                     |     |

|      | 2.7 A Hybrid Application of OmpSs                                                                                               |     |

|      | 2.8 Application of Accelerator Units to Neural Networks                                                                         | 19  |

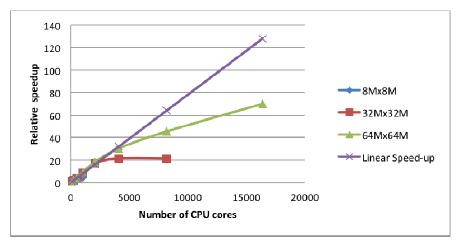

| 3    | Scalable Libraries and Algorithms                                                                                               |     |

|      | 3.1 Enabling the Generation of Massive Unstructured Meshes for OpenFOAM using Netgen                                            | 22  |

|      | 3.2 Enhancing Code_Saturne Capability in the area of Parallel Local Mesh Refinement                                             |     |

|      | 3.3 Exploiting Open Source Codes for Solving Multi-scale Multi-physics Problems                                                 |     |

|      | 3.4 Enabling DL_POLY_4 for Scalable MD Simulations with Non-Periodic Boundary Conditi Accounting for Electrostatic Interactions |     |

|      | 3.5 Enabling OpenFOAM for Bio-medical Flow Simulations                                                                          |     |

|      | 3.6 Towards the Implementation of an Algebraic Multi-Grid Solver for Lattice QCD on Exasc Hardware                              | ale |

|      | 3.7 Parallelisation of Sparse Matrix Kernels for Large-Scale Scientific Applications using the MapReduce Paradigm               |     |

| 4    | Debuggers and Profilers                                                                                                         |     |

| 7    | 4.1 Profiling Code Saturne with TAU and auto-tuning kernels with Orio                                                           |     |

|      | 4.2 Performance Analysis of Alya on Multi-petaflop Systems using Extrae                                                         |     |

| 5    | I/O Management Techniques                                                                                                       |     |

| 5    | 5.1 Exploiting the SIONlib library for Fast, Parallel POSIX I/O in the Bonsai Astrophysics Co                                   |     |

| ,    |                                                                                                                                 |     |

| 6    | Summary                                                                                                                         | 44  |

## List of Figures

| Figure 1: Gantt chart outlying first draft of the PRACE 3IP 17.2 exploitation phase schedule in      |         |

|------------------------------------------------------------------------------------------------------|---------|

| 2013. Taken from PRACE 3IP T7.2 Wiki page                                                            |         |

| Figure 3: CP2K test results for OpenCL and OpenACC (mm_stack_size = 10000)                           |         |

| Figure 4: Weak scaling of FHP on a node with 8 NVIDIA M2090 GPUs                                     | 15      |

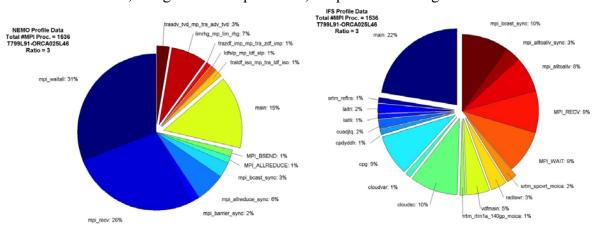

| Figure 5: Profiling of EC-Earth3 (T799L91-ORCA025L46). The simulation was run using 153              |         |

| cores using a 'total processes per NEMO process ratio' of 3. Routines are presented only             |         |

| account for greater than 1% of total run time. Left: NEMO, Right: IFS                                |         |

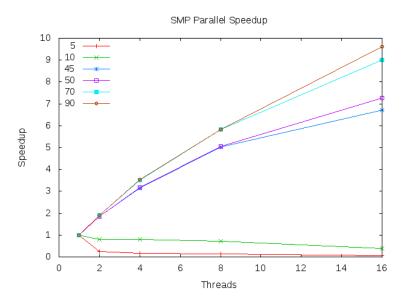

| Figure 6: LULESH Speedup on a 16-core SMP system                                                     |         |

| Figure 7: Adapted program speedup relative to single-threaded execution in native mode on Xe         |         |

|                                                                                                      |         |

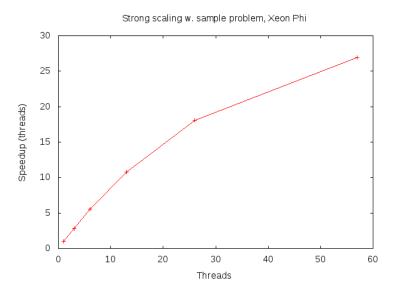

| Figure 8: Parallel mesh generation timings for (a) Onera-M6.stl, (b) shaft.geo, (c) sphere.stl a     |         |

| sphere.geo geometries obtained for various ranges of coarse and fine mesh sizes                      | 23      |

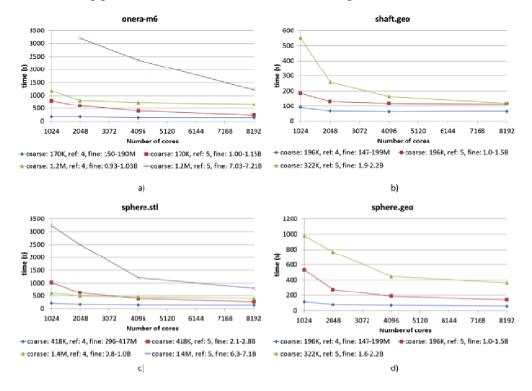

| Figure 9: Strong scalability of the CSM (left) and CFD (right) solvers for a wind turbine simulat    | tion 26 |

| Figure 10: Scaling performance of the Poisson Solver module in DL_POLY_4 (relative to                |         |

| process) vs. number of MPI processes for a single time-step                                          |         |

| Figure 11: The results obtained using OpenAFOAM icoFOAM solver                                       | 30      |

| Figure 12: Scalability of icoFOAM solver on CURIE                                                    | 30      |

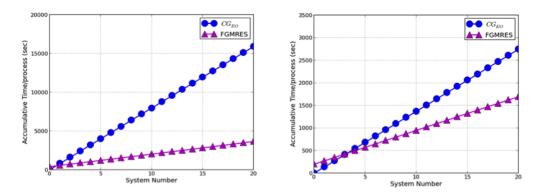

| Figure 13: Accumulative time to solution for each MPI process (sec) for solving 20 linear sy         | ystems. |

| Left: B85.24 lattice on 32 cores. Right: D15.48 lattice on 512 cores.                                |         |

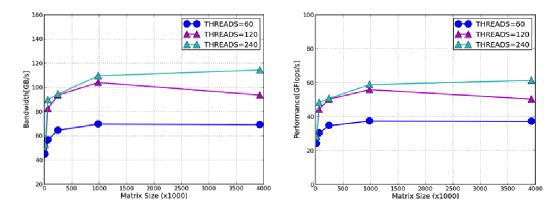

| Figure 14: Performance of the vectorized matrix-vector multiplications on a single Xeon Ph           |         |

| Left: Bandwidth. Right: FLOPs/s                                                                      |         |

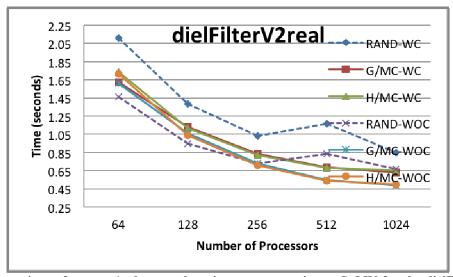

| Figure 15: Comparison of mapper/reducer task assignment strategies on SpMV f dielFilterV2real Matrix |         |

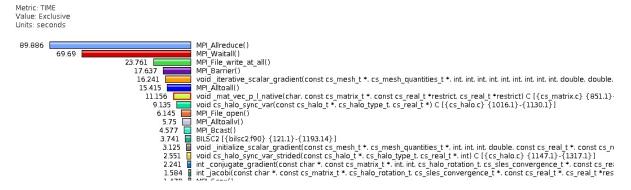

| Figure 16: Profiles of functions (averaged on 4096 cores-256 nodes) from Code Saturne in dec         |         |

| order of exclusive time, 51M case                                                                    | _       |

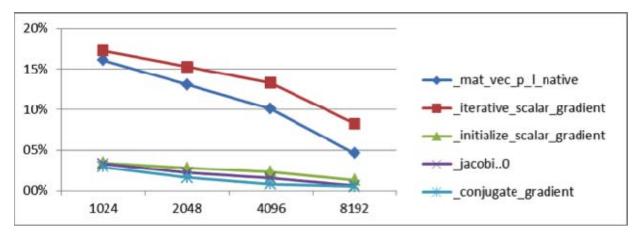

| Figure 17: Visual comparison of hotspot routines for the Tube bundle test case                       |         |

| Figure 18: Orio input file for optimization (loop-unrolling) of _mat_vec_p_l native                  |         |

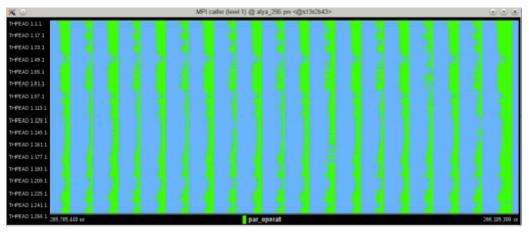

| Figure 19: Profile of the iterative part of Alya on 256 processes (zoomed in)                        |         |

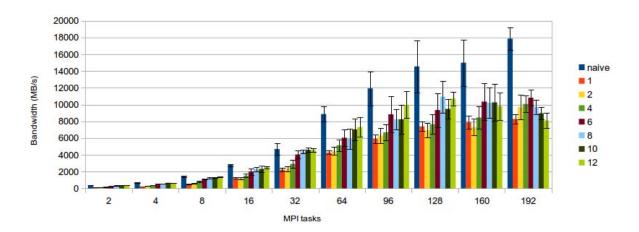

| Figure 20: Bandwidth on Cartesius for the naive approach and SIONlib writing to one file             |         |

| different strip sizes (in MB). All runs with one MPI task per node. Error bars indicate the st       |         |

| deviation from eight measurements                                                                    | 43      |

|                                                                                                      |         |

|                                                                                                      |         |

| List of Tables                                                                                       |         |

| Table 1: HPC Tools and Techniques (Programming Models) exploited along with corresp                  | onding  |

| applications                                                                                         | _       |

| Table 2: Scaling results for 'One Tube' test case runs comparing the original two                    |         |

| communications vs. the new one-sided communication implementation (version 1)                        |         |

| Table 3: Wall-clock time of the main loop in spme forces() for different implementations             |         |

| Table 4: The performance of our implementation of the Cellular Automata Library (FHP) on             |         |

| CUDA-capable devices in GUPS (lattice node updates per second). Higher is better                     | 15      |

| Table 5: Performance of two IFS routines on CPU and GPU. In each case, we compare runtime            |         |

| a single CPU (Xeon X5560) core with no GPUs attached to the same CPU chipset with                    | a GPU   |

| (NVIDIA Tesla M2090) attached                                                                        |         |

| Table 6: HPC Tools and Techniques (Scalable Libraries and Algorithms) exploited alon                 |         |

| corresponding applications                                                                           | 21      |

| Table 7: Adaptive refinement of a cubic cavity from 14 million cells to 16 million                   |         |

| Table 8: Full refinement of a cubic cavity from 14 million cells to 111 million                      |         |

| Table 9: Adaptive refinement of a cubic cavity from 111 million cells to 126 million                 |         |

| Table 10: Parameters of the gauge configurations used in testing the AMG Solver                      | 32      |

|                                                                                                      |         |

vi

### **References and Applicable Documents**

- [1] M. Lysaght, B. Lindi, V. Vondrak, J. Donners, M. Tajchman, PRACE-3IP D7.2.1 A Report on the Survey of HPC Tools and Techniques, pdf: <a href="http://www.prace-project.eu/IMG/pdf/d7.2.1.pdf">http://www.prace-project.eu/IMG/pdf/d7.2.1.pdf</a>

- [2] PRACE Whitepapers can be found at: <a href="http://www.prace-project.eu/white-papers">http://www.prace-project.eu/white-papers</a>

- [3] G. Mozdzynski, A PGAS implementation of the ECMWF Integrated Forecasting System (IFS), CRESTA report, pdf:

http://www.easc2013.org.uk/sites/default/files/Pdfs/InvitedTalks/EASC-Mozdzynski.pdf

- [4] CP2K homepage: <a href="http://www.cp2k.org">http://www.cp2k.org</a>

- [5] J. VandeVondele, M. Krack, F. Mohamed, M. Parrinello, T. Chassaing, J. Hutter, QUICKSTEP: Fast and accurate density functional calculations using a mixed Gaussian and plane waves approach. Comp. Phys. Comm. 167 (2): 103-128 (2005)

- [6] Intel Xeon Phi Specifications; http://www.intel.com/content/www/us/en/processors/xeon/xeon-phi-detail.html

- [7] F. Reid and I. Bethune, Optimising CP2K for the Intel Xeon Phi, PRACE White Paper, 2013, pdf: <a href="http://www.prace-ri.eu/IMG/pdf/wp140.pdf">http://www.prace-ri.eu/IMG/pdf/wp140.pdf</a>

- [8] Code Saturne homepage: http://code-saturne.org/cms/

- [9] MPI 3.0 standard, pdf: <a href="http://www.mpi-forum.org/docs/mpi-3.0/mpi30-report.pdf">http://www.mpi-forum.org/docs/mpi-3.0/mpi30-report.pdf</a>

- [10] ONE\_TUBE test case reference: http://cfd.mace.manchester.ac.uk/cgibin/cfddb/prpage.cgi?78&EXP&&database/cases/case78&cas78\_head.html&cas78\_desc.html&cas78\_meth.html&cas78\_data.html&cas78\_refs.html&cas78\_rsol.html&1&1&1&1&unknown

- [11] DL POLY homepage:

- http://www.stfc.ac.uk/CSE/randd/ccg/software/DL POLY/25526.aspx

- [12] C. Kartsaklis, G. Civario, Porting DL POLY on GPGPU with CUDA, presented at NVIDIA GPU Technology Conference (GTC), San Jose, (2010)

- [13] The OpenACC homepage: http://www.openacc-standard.org/

- [14] I. Bethune, A. Carter, X. Guo, P. Korosoglou, Million Atom KS-DFT with CP2K, PRACE whitepaper, PRACE-1IP, pdf: <a href="http://www.prace-ri.eu/IMG/pdf/Million\_Atom\_KS-DFT\_with\_CP2K.pdf">http://www.prace-ri.eu/IMG/pdf/Million\_Atom\_KS-DFT\_with\_CP2K.pdf</a>

- [15] I. Bethune, "Improving the scalability of CP2K on multi-core systems, dCSE Project, 2010, pdf: <a href="http://www.hector.ac.uk/cse/distributedcse/reports/cp2k02/cp2k02">http://www.hector.ac.uk/cse/distributedcse/reports/cp2k02/cp2k02</a> final report.pdf

- [16] OpenCL Khronos Group homepage, http://www.khronos.org/opencl

- [17] U. Borštnik, J. VandeVondele, V. Weber, J. Hutter, Sparse Matrix Multiplication: The Distributed Block-Compressed Sparse Row Library, Parallel Computing, 40(5-6): 47-58 (2014)

- [18] The OpenACC 2.0a Specification (Corrected), pdf:

- http://www.openacc.org/sites/default/files/OpenACC.2.0a 1.pdf

- [19] The Khronos OpenCL Registry with OpenCL 2.0 specification,

- http://www.khronos.org/registry/cl/

- [20] Portland Group's PGI Accelerator compilers:

- http://www.pgroup.com/resources/accel.htm

- [21] Allinea DDT homepage: http://www.allinea.com/products/ddt/

- [22] PGDBG Graphical Symbolic Debugger: <a href="http://www.pgroup.com/products/pgdbg.htm">http://www.pgroup.com/products/pgdbg.htm</a>

- [23] F. Reid, I. Bethune, Evaluating CP2K on Exascale Hardware: Intel Xeon Phi", PRACE whitepaper (2014) pdf: <a href="http://www.prace-project.eu/IMG/pdf/wp152.pdf">http://www.prace-project.eu/IMG/pdf/wp152.pdf</a>

- [24] U. Frisch, B. Hasslacher, and Y. Pomeau, Lattice gas automata for the Navier-Stokes equation. Phys. Rev. Lett., 56, 1505 (1986)

- [25] G. Kohring, The cellular automata approach to simulating fluid flows in porous media. Physica A, 186, 97–108 (1992)

- [26] Portland Group (2010) PGI Fortran & C Accelerator Programming Model new features ver. 1.3.

- [27] M. G. B. Johnson, D. P. Playne, and K. A. Hawick, Data-parallelism and GPUs for lattice gas fluid simulations. Proc. International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA10), Las Vegas, USA, 12-15 July, pp. 210–216. CSREA. PDP4521 (2010)

- [28] EC-Earth homepage: <a href="http://www.ec-earth.org/">http://www.ec-earth.org/</a>

- [29] http://www.ecmwf.int/research/ifsdocs/CY40r1/

- [30] G. Madec, NEMO ocean engine, Note du Pole de modélisation, Institut Pierre-Simon Laplace (IPSL), France, No 27 ISSN No 1288-1619 (2008) pdf: NEMO book 3 4.pdf

- [31] M Vancoppenolle, S. Bouillon, T. Fichefet, H. Goosse, O. Lecomte, M. A. Morales Maqueda, and G Madec, LIM The Louvain-la-Neuve sea Ice Model. Note du Pole de modélisation, Institut Pierre-Simon Laplace (IPSL), (2012) France, No 31 ISSN No 1288-1619.

- [32] Vancoppenolle, M., T. Fichefet, H. Goosse, S. Bouillon, G. Madec, and M.A. Morales Maqueda, Simulating the mass balance and salinity of Arctic and Antarctic sea ice. 1. Model description and validation. Ocean Modelling, 27, 33-53 (2009)

- [33] S. Valcke, T Craig, L. Coquart, <u>OASIS3-MCT User Guide</u>, OASIS3-MCT 2.0, Technical Report, TR/CMGC/13/17, CERFACS/CNRS SUC URA No 1875, Toulouse, France (2013)

- [34] LULESH webpage: <a href="https://codesign.llnl.gov/lulesh.php">https://codesign.llnl.gov/lulesh.php</a>

- [35] ALE3D webpage: https://wci.llnl.gov/codes/ale3d/

- [36] I. Karlin, A. Bhatele, J. Keasler, Bradford L. Chamberlain, J. Cohen, Z. DeVito, R. Haque, D. Laney, E. Luke, F. Wang, D. Richards, M. Schulz, C. H. Still: *Exploring Traditional and Emerging Parallel Programming Models using a Proxy Application*, proceedings of the 2013 IEEE 27th International Symposium on Parallel and Distributed Processing

- [37] Programming Models at BSC, <a href="http://pm.bsc.es/">http://pm.bsc.es/</a>

- [38] B. Dunn and R. Yasser, Learning and inference in a nonequilibrium Ising model with hidden nodes, Physical Review E, 2013

- [39] J. Bell L Chacon R. Falgout M. Heroux P. Hovland E. Ng C Webster S. Wild J. Dongarra, J Hittinger. Applied mathematics research for exascale computing report (2014) pdf: <a href="http://www.netlib.org/utk/people/JackDongarra/PAPERS/doe-exascale-math-report.pdf">http://www.netlib.org/utk/people/JackDongarra/PAPERS/doe-exascale-math-report.pdf</a>

- [40] OpenFoam homepage: <a href="http://www.openfoam.org/">http://www.openfoam.org/</a>

- [41] NetGen, Mesh Generator hompage: http://www.hpfem.jku.at/netgen/

- [42] Parallel Mesh Multiplication and its Implementation in Code Saturne. A. Ronovsky, P. Kabelikova, V. Vondrak, C. Moulinec, Civil-Comp Proceedings ISSN 1759-3433. (doi:10.4203/ccp.101.11)

- [43] Code Aster homepage: <a href="http://www.code-aster.org/">http://www.code-aster.org/</a>

- [44] Elmer homepage: http://www.csc.fi/english/pages/elmer

- [45] FFLOP homepage: <a href="http://industry.it4i.cz/produkty/fllop/">http://industry.it4i.cz/produkty/fllop/</a>

- [46] PETSc homepage: http://www.mcs.anl.gov/petsc/

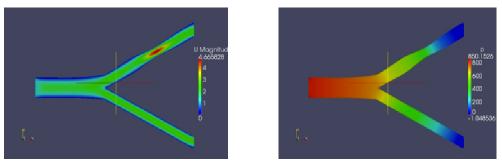

- [47] S. Piskin, M. S. Celebi, Analysis of the effects of different pulsatile inlet profiles on the hemodynamical properties of blood flow in patient specific carotid artery with stenosis,

- Computers in Biology and Medicine, Volume 43, Issue 6, 1 July 2013, Pages 717-728, ISSN 0010-4825, http://dx.doi.org/10.1016/j.compbiomed.2013.02.014

- [48] S. Piskin, M. S. Celebi, "Numerical blood flow simulation with predefined artery movement," Biomedical Engineering and Informatics (BMEI), 2012 5th International Conference, pp.654,658, 16-18 Oct. 2012 doi: 10.1109/BMEI.2012.6513039

- [49] H. Turkeri, S. Piskin, and M. S. Celebi, A comparison between non-Newtonian and Newtonian blood viscosity models, Journal of Biomechanics, 44, Supplement 1, 2011

- [50] S. Piskin and A. Akkus, Biofluid flow applications by open-source software, 17. National Biomedical Engineering Meeting BIYOMUT 2012, Istanbul, Turkey, October 3-5, 2012

- [51] P. Dagna and J. Hertzer, Evaluation of multi-threaded OpenFOAM hybridization for massively parallel architectures, PRACE WP98, Aug. 20, 2013, www.prace-project.eu/IMG/pdf/wp98.pdf

- [52] M. Manguoglu, PRACE WP, Sep. 6, 2012, http://www.prace-project.eu/IMG/pdf/A\_General\_Sparse\_Sparse\_Linear\_System\_Solver\_and\_Its\_Application\_in OpenFOAM-2.pdf

- [53] M. Culpo, PRACE WP, Sep. 6, 2012, http://www.prace-ri.eu/IMG/pdf/Current\_Bottlenecks\_in\_the\_Scalability\_of\_OpenFOAM\_on\_Massively\_Parallel Clusters-2.pdf

- [54] M. Moyles, P. Nash, and Ivan Girotto, PRACE WP, Sep. 6, 2012, http://www.prace-ri.eu/IMG/pdf/Performance\_Analysis\_of\_Fluid-Structure Interactions using OpenFOAM.pdf

- [55] T. Behrens, OpenFOAM's basic solvers for linear systems of equations: Solvers, preconditioners, smoothers, Tech. Rep. DTU, Denmark, Feb. 18, 2009,

- http://www.tfd.chalmers.se/~hani/kurser/OS CFD 2008/TimBehrens/tibeh-report-fin.pdf

- [56] Xiaoye S. Li and James W. Demmel, SuperLU\_DIST: A Scalable Distributed-Memory Sparse Direct Solver for Unsymmetric Linear Systems, ACM Trans. on Math. Software, Vol. 29, No. 2, June 2003, pp. 110-140.

- [57] X. S. Li, J. W. Demmel, J. R. Gilbert, L. Grigori, M. Shao, and I. Yamazaki, SuperLU Users' Guide, Tech. Report UCB, Computer Science Division, University of California, Berkeley, CA, 1999, update: 2011

- [58] A. Duran, M.S. Celebi, M. Tuncel and B. Akaydın, Design and implementation of new hybrid algorithm and solver on CPU for large sparse linear systems, PRACE-2IP white paper, Libraries, WP 43, July 13, 2012, http://www.prace-ri.eu/IMG/pdf/wp43-newhybridalgorithmfo lsls.pdf

- [59] A. Duran, M.S. Celebi, M. Tuncel, and F. Oztoprak. Structural analysis of large sparse matrices for scalable direct solvers. PRACE-2IP white paper, Scalable algorithms, WP 82, August 20, 2013, http://www.prace-project.eu/IMG/pdf/wp82.pdf

- [60] Andreas Frommer, et. al., "Adaptive aggregation based domain decomposition multigrid for the lattice Wilson Dirac operator", arXiv: 1303.1377[hep-lat].

- [61] K. Jansen and C. Urbach, "tmLQCD: A Program suite to simulate Wilson Twisted mass Lattice QCD", Comput. Phys. Com. 180(2009)2717-2738 (arXiv: 0905.3331).

- [62] tmLQCD homepage: https://github.com/etmc/tmLQCD.

- [63] <a href="https://confluence.csc.fi/display/HPCproto/HPC+Prototypes">https://confluence.csc.fi/display/HPCproto/HPC+Prototypes</a>.

- [64] J Cohen, Graph twiddling in a mapreduce world. Computing in Science & Engineering, 11(4), 29-41 (2009)

- [65] Ekanayake, J., & Fox, G. (2010). High performance parallel computing with clouds and cloud technologies. In Cloud Computing (pp. 20-38). Springer Berlin Heidelberg.

- [66] Kang, U., Tsourakakis, C. E., & Faloutsos, C. (2009, December). Pegasus: A peta-scale graph mining system implementation and observations. In Data Mining, 2009. ICDM'09. Ninth IEEE International Conference on (pp. 229-238). IEEE.

- [67] Tu, T., Rendleman, C. A., Borhani, D. W., Dror, R. O., Gullingsrud, J., Jensen, M. O., and Shaw, D. E. (2008, November). A scalable parallel framework for analyzing terascale molecular dynamics simulation trajectories. In High Performance Computing, Networking, Storage and Analysis, 2008. SC 2008. International Conference for (pp. 1-12). IEEE. [68] Plimpton, S. J., & Devine, K. D. (2011). MapReduce in MPI for large-scale graph algorithms. Parallel Computing, 37(9), 610-632.

- [69] Hoefler, T., Lumsdaine, A., & Dongarra, J. (2009). Towards efficient mapreduce using mpi. In Recent Advances in Parallel Virtual Machine and Message Passing Interface (pp. 240-249). Springer Berlin Heidelberg.

- [70] Karypis, G., & Kumar, V. (1998). A fast and high quality multilevel scheme for partitioning irregular graphs. SIAM Journal on scientific Computing, 20(1), 359-392.

- [71] Catalyurek, U. V., & Aykanat, C. (1999). Hypergraph-partitioning-based decomposition for parallel sparse-matrix vector multiplication. Parallel and Distributed Systems, IEEE Transactions on, 10(7), 673-693.

- [72] Davis, T. A., & Hu, Y. (2011). The University of Florida sparse matrix collection. ACM Transactions on Mathematical Software (TOMS), 38(1), 1.

- [73] TAU homepage: <a href="http://www.cs.uoregon.edu/research/tau/home.php">http://www.cs.uoregon.edu/research/tau/home.php</a>

- [74] HPCToolKit homepage: <a href="http://hpctoolkit.org/">http://hpctoolkit.org/</a>

- [75] Orio homepage: http://brnorris03.github.io/Orio/

- [76] Moulinec, C., Sunderland, A. G., Kabelikova, P., Ronovsky, A., Vondrak, V., Turk, A., Aykanat, C., and Theodosiou, C., 2012, Optimization of Code\_Saturne for Petascale Simulations, PRACE white paper (2012), pdf: <a href="http://www.prace-project.eu/IMG/pdf/Optimisation">http://www.prace-project.eu/IMG/pdf/Optimisation</a> of Code Saturne for Petascale Simulations.pdf

- [77] Alya System homepage: http://www.bsc.es/computer-applications/alya-system

- [78] PRACE UEABS, Unified European Applications Benchmark Suite, <a href="http://www.prace-ri.eu/ueabs?lang=en">http://www.prace-ri.eu/ueabs?lang=en</a>

- [79] Extrae, http://www.bsc.es/computer-sciences/extrae

- [80] Paraver, http://www.bsc.es/computer-sciences/performance-tools/paraver

- [81] Wautelet, P., Kestener, P., 2012, Parallel IO performance and scalability study on the CURIE supercomputer, PRACE white paper, pdf: <a href="http://www.prace-ri.eu/IMG/pdf/Parallel\_IO\_performance\_and\_scalability\_study\_on\_the\_PRACE\_CURIE\_supercomputer-2.pdf">http://www.prace-ri.eu/IMG/pdf/Parallel\_IO\_performance\_and\_scalability\_study\_on\_the\_PRACE\_CURIE\_supercomputer-2.pdf</a>

- [82] J. Bédorf, E. Gaburov, S. Portegies Zwart, A sparse octree gravitational N-body code that runs entirely on the GPU processor, J. Comp. Pys., 231, 2825–2839 (2011)

- [83] W. Frings, F. Wolf, V. Petkov, Scalable Massively Parallel I/O to Task-Local File, Proceedings of the Conference on High Performance Computing Networking, Storage and Analysis, 17:1-11 (2009)

#### **List of Acronyms and Abbreviations**

AAA Authorization, Authentication, Accounting.

ACF Advanced Computing Facility

ADP Average Dissipated Power

AISBL Association sans but lucrative (legal form of the PRACE RI)

AMD Advanced Micro Devices

APGAS Asynchronous PGAS (language)

API Application Programming Interface

APML Advanced Platform Management Link (AMD)

ASIC Application-Specific Integrated Circuit

ATI Array Technologies Incorporated (AMD)

BAdW Bayerischen Akademie der Wissenschaften (Germany)

BCO Benchmark Code Owner

BLAS Basic Linear Algebra Subprograms

BSC Barcelona Supercomputing Center (Spain)

CAF Co-Array Fortran

CAL Compute Abstraction Layer

CCE Cray Compiler Environment

ccNUMA cache coherent NUMA

CEA Commissariat à l'énergie atomique et aux énergies alternatives

CGS Classical Gram-Schmidt

CGSr Classical Gram-Schmidt with re-orthogonalisation

CINECA Consorzio Interuniversitario, the largest Italian computing centre (Italy)

CINES Centre Informatique National de l'Enseignement Supérieur (represented

in PRACE by GENCI, France)

CLE Cray Linux Environment CPU Central Processing Unit

CSC Finnish IT Centre for Science (Finland)

CSCS The Swiss National Supercomputing Centre (represented in PRACE by

ETHZ, Switzerland)

CSR Compressed Sparse Row (for a sparse matrix)

CUDA Compute Unified Device Architecture (NVIDIA)

DARPA Defense Advanced Research Projects Agency

DDN DataDirect Networks

DDR Double Data Rate

DEISA Distributed European Infrastructure for Supercomputing Applications.

EU project by leading national HPC centres.

DFT Density Functional Theory

DGEMM Double precision General Matrix Multiply

DIMM Dual Inline Memory Module

DMA Direct Memory Access

DNA DeoxyriboNucleic Acid

DOE Department of Energy (USA)

DP Double Precision, usually 64-bit floating point numbers

DRAM Dynamic Random Access memory

EC European Commission

EESI European Exascale Software Initiative

Eol Expression of Interest

EP Efficient Performance, e.g., Nehalem-EP (Intel)

EPCC Edinburg Parallel Computing Centre (represented in PRACE by

EPSRC, United Kingdom)

EPSRC The Engineering and Physical Sciences Research Council (United

Kingdom)

eQPACE extended QPACE, name of the FZJ WP8 prototype

ETHZ Eidgenössische Technische Hochschule Zuerich, ETH Zurich

(Switzerland)

ESFRI European Strategy Forum on Research Infrastructures; created

roadmap for pan-European Research Infrastructure.

EX Expandable, e.g., Nehalem-EX (Intel)

FC Fiber Channel

FFT Fast Fourier Transform

FHPCA FPGA HPC Alliance

FP Floating-Point

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FZJ Forschungszentrum Jülich (Germany)

GASNet Global Address Space Networking

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GCS Gauss Centre for Supercomputing (Germany)

GDDR Graphic Double Data Rate memory

GÉANT Collaboration between National Research and Education Networks to

build a multi-gigabit pan-European network, managed by DANTE.

GÉANT2 is the follow-up as of 2004.

GENCI Grand Equipment National de Calcul Intensif (France)

GFlop/s Giga (= 10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also GF/s

GHz Giga (= 10<sup>9</sup>) Hertz, frequency =10<sup>9</sup> periods or clock cycles per second

GigE Gigabit Ethernet, also GbE

GLSL OpenGL Shading Language

GNU GNU's not Unix, a free OS

GPGPU General Purpose GPU

GPU Graphic Processing Unit

GS Gram-Schmidt

GWU George Washington University, Washington, D.C. (USA)

HBA Host Bus Adapter

HCA Host Channel Adapter

HCE Harwest Compiling Environment (Ylichron)

HDD Hard Disk Drive HE High Efficiency

HET High Performance Computing in Europe Taskforce. Taskforce by

representatives from European HPC community to shape the European HPC Research Infrastructure. Produced the scientific case and valuable

groundwork for the PRACE project.

HMM Hidden Markov Model

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hewlett-Packard

HPC High Performance Computing; Computing at a high performance level

at any given time; often used synonym with Supercomputing

HPCC HPC Challenge benchmark, <a href="http://icl.cs.utk.edu/hpcc/">http://icl.cs.utk.edu/hpcc/</a>

HPCS High Productivity Computing System (a DARPA program)

HPL High Performance LINPACK

HT HyperTransport channel (AMD)

HWA HardWare accelerator

IB InfiniBand

IBA IB Architecture

IBM Formerly known as International Business Machines

ICE (SGI)

IDRIS Institut du Développement et des Ressources en Informatique

Scientifique (represented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IESP International Exascale Project

IL Intermediate Language IMB Intel MPI Benchmark

I/O Input/Output

IOR Interleaved Or Random

IPMI Intelligent Platform Management Interface

ISC International Supercomputing Conference; European equivalent to the

US based SCxx conference. Held annually in Germany.

IWC Inbound Write Controller

JSC Jülich Supercomputing Centre (FZJ, Germany) KB Kilo (=  $2^{10} \sim 10^3$ ) Bytes (= 8 bits), also KByte

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC,

Sweden)

LBE Lattice Boltzmann Equation

LINPACK Software library for Linear Algebra

LLNL Laurence Livermore National Laboratory, Livermore, California (USA)

LQCD Lattice QCD

LRZ Leibniz Supercomputing Centre (Garching, Germany)

LS Local Store memory (in a Cell processor) MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (= 10<sup>6</sup>) Bytes (= 8 bits) per second, also MByte/s

MDT MetaData Target

MFC Memory Flow Controller

MFlop/s Mega (=  $10^6$ ) Floating point operations (usually in 64-bit, i.e. DP) per

second, also MF/s

MGS Modified Gram-Schmidt

MHz Mega (= 10<sup>6</sup>) Hertz, frequency =10<sup>6</sup> periods or clock cycles per second MIPS Originally Microprocessor without Interlocked Pipeline Stages; a RISC

processor architecture developed by MIPS Technology

MKL Math Kernel Library (Intel)

ML Maximum Likelihood

Mop/s Mega (=  $10^6$ ) operations per second (usually integer or logic operations)

MoU Memorandum of Understanding.

MPI Message Passing Interface

MPP Massively Parallel Processing (or Processor)

MPT Message Passing Toolkit MRAM Magnetoresistive RAM

MTAP Multi-Threaded Array Processor (ClearSpead-Petapath)

mxm DP matrix-by-matrix multiplication mod2am of the EuroBen kernels

OST

NAS Network-Attached Storage

NCF Netherlands Computing Facilities (Netherlands)

NDA Non-Disclosure Agreement. Typically signed between vendors and

customers working together on products prior to their general

availability or announcement.

NoC Network-on-a-Chip NFS Network File System

NIC Network Interface Controller

NUMA Non-Uniform Memory Access or Architecture

OpenCL Open Computing Language

OpenGL Open Graphic Library

Open MP Open Multi-Processing

OS Operating System

OSS Object Storage Server

PCIe Peripheral Component Interconnect express, also PCI-Express

PCI-X Peripheral Component Interconnect eXtended

PGAS Partitioned Global Address Space

Object Storage Target

PGI Portland Group, Inc.

pNFS Parallel Network File System

POSIX Portable OS Interface for Unix

PPE PowerPC Processor Element (in a Cell processor)

PRACE Partnership for Advanced Computing in Europe PRACE-PP PRACE

Preparatory Phase; Project Acronym

PSNC Poznan Supercomputing and Networking Centre (Poland)

QCD Quantum Chromodynamics

QCDOC Quantum Chromodynamics On a Chip

QDR Quad Data Rate

QPACE QCD Parallel Computing on the Cell

QR — QR method or algorithm: a procedure in linear algebra to compute the

eigenvalues and eigenvectors of a matrix

RAM Random Access Memory

RDMA Remote Direct Memory Access

RI Research Infrastructure

RISC Reduce Instruction Set Computer RNG Random Number Generator

RPM Revolution per Minute SAN Storage Area Network

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SAS Serial Attached SCSI

SATA Serial Advanced Technology Attachment (bus)

SDK Software Development Kit

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SHMEM Share Memory access library (Cray)

SIMD Single Instruction Multiple Data

SM Streaming Multiprocessor, also Subnet Manager

SMP Symmetric MultiProcessing

SNIC Swedish National Infrastructure for Computing (Sweden)

SP Single Precision, usually 32-bit floating point numbers

SPE Synergistic Processing Element (core of Cell processor)

SPH Smoothed Particle Hydrodynamics

SPU Synergistic Processor Unit (in each SPE)

SSD Solid State Disk or Drive

STFC Science and Technology Facilities Council (represented in PRACE by

EPSRC, United Kingdom)

STRATOS PRACE advisory group for STRAtegic TechnOlogieS

STT Spin-Torque-Transfer

SURFsara Dutch national High Performance Computing & e-Science Support

Center

TARA Traffic Aware Routing Algorithm

TB Tera (= 240 ~ 1012) Bytes (= 8 bits), also TByte

TCO Total Cost of Ownership. Includes the costs (personnel, power, cooling,

maintenance, ...) in addition to the purchase cost of a system.

TDP Thermal Design Power

TFlop/s Tera (= 1012) Floating-point operations (usually in 64-bit, i.e. DP) per

second, also TF/s

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the Tier-0 systems; national or topical HPC centres would constitute Tier-1

UFM Unified Fabric Manager (Voltaire)

UNICORE Uniform Interface to Computing Resources. Grid software for seamless

access to distributed resources.

UPC Unified Parallel C UV Ultra Violet (SGI)

VHDL VHSIC (Very-High Speed Integrated Circuit) Hardware Description

Language

#### **Executive Summary**

The objective of PRACE-3IP Work Package 7 (WP7) 'Application Enabling and Support' is to provide applications enabling support for HPC applications codes which are important for European researchers to ensure that these applications can effectively exploit multi-petaflop systems. This applications enabling activity uses the most promising tools, algorithms and standards for optimisation and parallel scaling that have recently been developed through research and experience in PRACE and other projects.

In this deliverable, we report on the exploitation of new HPC tools and algorithms on different codes that are of interest to the European scientific and engineering research community. In this sense, the report here follows on naturally from the T7.2 deliverable D7.2.1, 'A Report on the Survey of HPC Tools and Techniques', which represented the first phase of activity in T7.2. Indeed, much of the exploitation work reported on here, was inspired by the comprehensive and in-depth analysis of state-of-the-art HPC tools and techniques as reported in D7.2.1.

The report on the exploitation of state-of-the-art HPC tools and techniques presented here represents the second phase of activity in T7.2. In this report we summarise how selected state-of-the-art HPC tools and techniques fared on real-world applications during the exploitation phase of T7.2, where we focus on four separate topics that we have identified as being important to enable applications within WP7 on the road to exascale, and which mirror the four topics reported on in the survey of HPC Tools and Techniques in D7.2.1. These are: (1) Programming Models, (2) Scalable Libraries and Algorithms, (3) Debuggers and Profilers and finally, (4) I/O Management Techniques. For a more detailed description of each of the exploitation projects summarised here, we refer the reader to the PRACE-3IP whitepaper associated with each of the 17 projects.

#### Programming Models

During the second phase of T7.2, we have exploited several different programming models that were reported on in D7.2.1 as having genuine potential on the road to exascale. In this deliverable we provide summary reports on the effectiveness of each of these HPC tools when enabling real applications with future exascale challenges in mind. In particular we have focused on probing new (as well as under-exploited) features in mature programming models, such as the Message Passing Interface (MPI), the new features of which are now starting to confront the challenges of exascale computing.

We have also exploited programming models targeting many-core architectures (where many-core typically implies > 50 cores), which are likely to continue to feature as part of future large-scale systems as we move into the deep petascale era. As pointed out in the first phase of T7.2, the entry of new competitors to the many-core space has increased the relevance of open standards on the road to exascale and we have therefore placed a particular focus on both mature and emerging open standards during the exploitation phase. In terms of more novel approaches to exploiting multi-petascale systems, we have also continued to be inspired by experimental programming models featuring in European exascale projects, which offer experimental task-based models for programming multi-/many-core architectures. We feel that it is worth also noting that, although possibilities for exploiting Partitioned Global Address Space (PGAS) languages on real applications were genuinely explored during the exploitation phase, no real opportunities arose for doing so, possibly reflecting the continuing challenge for exploiting these powerful tools on existing large-scale codes on the road to exascale.

#### Scalable Libraries and Algorithms

During the exploitation phase we have undertaken six separate enablement projects that have each focused on exploiting scalable libraries and algorithms. In terms of challenges on the road to exascale, global communications, in particular, are known to be a severe barrier when trying to scale across large core counts and many open questions still exist on how, for example, Fast Fourier Transform (FFT) libraries will perform on future exascale systems. With this challenge in mind, we are happy to report on the successful implementation of alternative methods to FFT libraries in a real molecular dynamics application, which has the potential to significantly improve scalability (and functionality) of the code on large node counts for certain problem types. As well as global communications, mesh generation and refinement have also been identified as posing major challenges on the road to exascale and as a result, we have also focused our efforts on both exploiting and improving state-of-the-art mesh tools for enabling Computational Fluid Dynamics (CFD) codes, which we report on here. We also report on the successful implementation of an Alegbraic Multi-Grid (AMG) algorithm within a lattice Quantum Chromo-Dynamics (QCD) code, which has been shown to outperform existing techniques and shows real potential for enabling OCD applications on the road to exascale.

#### Debuggers and Profilers

In the survey of state-of-the-art HPC tools and techniques as reported in D7.2.1 we found that all of the European exascale projects are concentrating effort on tools for debugging and performance analyses. This is deemed a necessity for efficient use of multi-petascale and future exascale systems: If we are to enable applications on such systems, then we need to have as clear a view as possible of the barriers to achieving performance. At the same time, we noted in D7.2.2, that very little effort had gone into documenting the experience of using such tools on real applications within PRACE to date. Here, we try to rectify this by reporting on how state-of-the art profiling tools fared with respect to real large scale CFD and Computational Structural Mechanics (CSM) codes. We also report on how such tools can potentially be employed in combination with auto-tuning tools, which are becoming of increasing interest on the road to exascale.

#### I/O Management Techniques

During our surveying in the first phase of T7.2 and as reported on in D7.2.2, we found that users within PRACE have in general not been able to squeeze as much performance from existing parallel file systems as they have from computational hardware, particularly for the case of high-level I/O libraries. With this challenge in mind, we have carried out deeper investigations into extracting performance from file systems using state-of-the-art high-level libraries, work that we are happy to report has improved the I/O performance of an astrophysics application on Tier-0 systems and shows real promise on the road to exascale.

#### 1 Introduction

#### 1.1 The Purpose of the document

The objective of PRACE-3IP Work Package 7 (WP7) 'Application Enabling and Support' is to provide applications enabling support for HPC applications codes which are important for European researchers to ensure that these applications can effectively exploit multi-petaflop systems. This applications enabling activity used the most promising tools, algorithms and standards for optimisation and parallel scaling that have recently been developed through research and experience in PRACE and other projects.

There has been significant research activity undertaken both within PRACE and outside PRACE investigating novel techniques to enable applications on petascale and future exascale systems. Such activities include, for example, PRACE Work Packages [WP6 ('Software Enabling for Petaflop/s Systems') in PRACE-PP, WP7 ('Enabling Petascale Applications: Efficent Use of Tier-0 Systems') and WP9 ('Future Technologies') in PRACE-1IP, WP7 ('Scaling Applications for Tier-0 and Tier-1 Users'), WP8 ('Community Codes'), and WP12 ('Novel Programming Techniques') in PRACE-2IP], other EU-funded projects (European Exascale Software Initiative (EESI), Towards Exaflop applications (TEXT), Collaborative Research into Exascale Systemware, Tools and Applications (CRESTA), Dynamical Exascale Entry Platform (DEEP), Mont-Blanc and international collaborations such as the International Exascale Software Project (IESP).

As stated in the Description of Work (DoW), the objective of this deliverable, D7.2.2, is to report on the exploitation of new HPC tools and algorithms on different codes. In this sense, the report here follows on naturally from the T7.2 deliverable D7.2.1, 'A Report on the Survey of HPC Tools and Techniques' [1] which represented the first phase of activity in T7.2. Indeed, much of the exploitation work reported on here, was inspired by the comprehensive and in-depth analysis of state-of-the-art HPC tools and techniques as provided in D7.2.1.

The report on the exploitation of HPC tools and techniques presented here represents the second phase of activity in T7.2. Here, we report on four separate topics that are important to enabling applications within WP7, and which mirror the four topics reported on in the survey of HPC Tools and Techniques in D7.2.1. These are: (1) Programming Models, (2) Scalable Libraries and Algorithms, (3) Debuggers and Profilers and finally, (4) I/O Management Techniques. In this report we summarise how selected HPC tools and techniques fared on real-world applications during the exploitation phase of T7.2. In this way, we hope to provide, primarily PRACE partners, with information that should hopefully stimulate further interest when considering the tools and techniques for furthering enabling projects. We also hope that the report will be of interest to European HPC users and more generally.

#### 1.2 Organisation of Work

Much of the work during the exploitation phase ("phase 2") of T7.2 followed on naturally from phase 1 and was organized in four subtasks:

- Subtask 7.2.A 'Debuggers and Profilers' (lead by Bjorn Lindi, SIGMA-NTNU)

- Subtask 7.2.B: 'Programming Languages and Standards' (lead by Marc Tajchman, GENCI)

- Subtask 7.2.C: 'Scalable Libraries and Algorithms' (lead by Vit Vondrak, VSB)

- Subtask 7.2.D: 'I/O Management Techniques' (lead by John Donners, SURFSARA)

#### PRACE-3IP Face-to-Face Meeting, Warsaw, Poland

Following the submission of deliverable, D7.2.1 'A Report on the Survey of HPC Tools and Techniques' in M11 (April 2013), a PRACE 3IP WP7 Face-to-Face Meeting was held in Warsaw, Poland in April 2013, where the conclusions of D7.2.1 were analysed in detail and where T7.2 partners were tasked with the following actions:

- Select a promising HPC tool(s)/technique(s) from the Survey

- Identify an application that has potential to scale on large compute systems and which also has relevance to the European scientific and engineering research community

- Produce a Description of Work for the exploitation project

- Produce a working title and abstract for the PRACE-3IP whitepaper associated with the project.

At the Face-to-Face meeting in Warsaw it was agreed that the exploitation projects should be inspired by the conclusions drawn from the analysis of state-of-the-art HPC tools and techniques as reported on in D7.2.1 and that the project should continue to be inspired by work taking place outside PRACE, particularly in the area of exascale research.

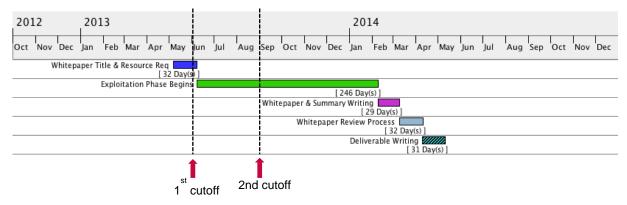

During the meeting in Warsaw, a new PRACE 3IP D7.2.2 page was set up on the PRACE wiki in order for monthly project progress reports to be uploaded. The D7.2.2 wiki page also contains an overall workplan and logistical information for the exploitation, including a "phase 2" schedule which was agreed on in Warsaw and which can be seen in Figure 1.

Figure 1: Gantt chart outlying first draft of the PRACE 3IP T7.2 exploitation phase schedule in April 2013. Taken from PRACE 3IP T7.2 Wiki page.

#### PRACE-3IP Face-to-Face Meeting, Dublin, Ireland

The second Face-to-Face Meeting during "phase 2" of T7.2 was held in Dublin, Ireland in December 2013. During the meeting progress reports were presented for each of the projects and each of the partners was tasked with the following actions:

Produce final title and abstract for the PRACE-3IP whitepaper associated with the exploitation project.

The final list of 17 whitepaper titles along with author lists were sent to PRACE PMO in February 2014.

All whitepapers were completed and submitted for internal T7.2 review on April 4<sup>th</sup> 2014 and subsequently for final PRACE-3IP review on April 11<sup>th</sup> 2014.

#### 1.3 Structure of the Document

The document presents four subsections which are aligned with the four subtasks within T7.2, and which mirror the four sections in deliverable D7.2.1. These are: Programming Models, Debuggers and Profilers, Scalable Libraries and Algorithms and I/O Management Techniques. Within each section, a short introduction is provided which further details the structure of the individual section, which is then followed by a collection of reports summarising the work and findings of each of the T7.2 projects during the exploitation phase.

#### 1.4 Intended Audience

Our objective in preparing this report is to exploit the most promising HPC tools and techniques that may have applicability for petascaling applications within WP7. Targeted primarily at PRACE partners who are involved in enabling applications, it provides an overview of how a selection of state-of-the-art HPC tools and techniques fared when enabling real applications targeting petascale systems/future exascale systems. We also hope that the report here will be of interest to European HPC users and more generally.

#### 2 Programming Models

In this section, we report on eight projects that have each focused on exploiting state-of-theart programming languages, techniques and standards (hereafter referred to as programming models) in order to enable applications for multi-petaflop/future exascale systems. Each subsection provides a summary of the project along with a reference to the PRACE-3IP whitepaper associated with the project. We recommend that the reader also refers to the associated whitepaper for each project [2], which provides a more detailed report on the projects than is provided here. The list of programming models as well the applications that were enabled can be seen in Table 1

| HPC Tool/Technique                 | Application                       |  |  |

|------------------------------------|-----------------------------------|--|--|

| MPI/OpenMP hybrid                  | CP2K                              |  |  |

| MPI 2/3.0 One-sided communications | Code_Saturne                      |  |  |

| OpenACC/OpenCL                     | CP2K                              |  |  |

| OpenACC/CUDA                       | Cellular Automata Library for CFD |  |  |

| OpenACC/CUDA                       | DL_POLY_4                         |  |  |

| OpenMP                             | Neural Networks application       |  |  |

| OmpSs                              | LULESH                            |  |  |

| OpenACC                            | EC-Earth3                         |  |  |

|                                    | 1                                 |  |  |

Table 1: HPC Tools and Techniques (Programming Models) exploited along with corresponding applications

As highlighted in D7.2.1 [1], currently, one programming model still dominates PRACE application codes more than any other, namely, Single Program Multiple Data (SPMD) message passing using MPI for internode communication, increasingly employed alongside OpenMP for intra-node parallelism. MPI and OpenMP are mature standards and widespread expertise on their use can be found within PRACE. However, both standards are evolving and version 3.0 of MPI and version 4.0 of OpenMP have recently been ratified, with partial

5

implementations for both now being offered by several tool developers. The reporting on new features of both standards in D7.2.1, as well as on how both programming models have been employed inside and outside PRACE to date has not only inspired us to investigate the opportunities for exploiting new features of the standards, but has also motivated us to further investigate features that already existed in previous versions of the standards and have so far been under-exploited in PRACE to date. An interesting example case of the latter is the exploitation of one-sided communication features offered through MPI 2.0/3.0 as described in detail in the whitepaper 'Enabling Code\_Saturne for Multi-petaflop/Exascale with MPI 3.0 One Sided Communications', and which is summarised later in this section.

While combining MPI and OpenMP is still considered to be the hybrid programming method of choice, the recent advent and rapid adoption of many-core coprocessors/accelerators in the design of multi-petaflop systems must increasingly be considered in order to exploit the full potential of the compute hardware space on emerging European multi-petascale/future exascale systems. To date, the challenge of exploiting such heterogeneous systems has typically been met within PRACE by augmenting the MPI/OpenMP hybrid model with an additional third model that targets the Single Instruction Multiple Thread (SIMT) architecture of GPUs thereby forcing the further extraction of hierarchical levels of parallelism in current PRACE applications.

In D7.2.1, it was found that, by far the most popular programming model for programming GPU architectures, both within and outside PRACE, is still NVIDIA's CUDA framework. While concerns are often voiced around the proprietary nature of CUDA, its ease of use and surrounding ecosystem is continually being improved upon and the language itself offers many elegant features for achieving performance on NVIDIA GPUs. There is, however, anecdotal evidence of concerns around the portability, programmability and maintainability of large-scale CUDA-based applications on the road to exascale. One possible solution to these issues is an open standard directive-based approach of which OpenACC represents the strongest offering to date. Interest in OpenACC is growing rapidly both inside and outside PRACE where this has been somewhat reinforced by the recent purchase of the Portland Group by NVIDIA in 2013. (Somewhat less clear at the time of writing is the much talked about roadmap for merging OpenACC and OpenMP into a single open standard). While the standard is still young, and in many cases does not result in the same level of performance as equivalent CUDA implementations, we have been stimulated by recent success stories, as reported on in D7.2.1, (including in DOE exascale projects) to further explore the technology and report here on how it has been exploited to enable four separate applications, namely, DL POLY, CP2K, EC-Earth and a CFD application during phase 2 of T7.2. A particularly interesting potential discussed in the whitepaper 'An Analysis of State of the Art Tools for Preparing DL POLY 4 for Exascale', as summarised in this section, is the capability to use OpenACC with CUDA in an interoperable way, possibly having implications for performance and maintainability of large-scale applications on the road to exascale.

The subject of open standards for programming heterogeneous systems has become quite a hot topic now that GPUs are not the only accelerator/many-core offering in town, since the arrival of Intel's Many Integrated Core (MIC) coprocessor (Xeon Phi) to the market in 2013. The Intel Xeon Phi is an x86-based architecture and so familiar open standards such as OpenMP and MPI can be used to program the device. This is currently not the case for GPUs. However, the OpenMP 4.0 standard does now support the targeting of accelerators in general and so, in theory, there is currently nothing to stop compiler support for programming GPUs via OpenMP. While both MPI and OpenMP can be used to program the Intel Xeon Phi, it is still unclear which is the best model for extracting performance and whether different models are better for different problem cases. One noteworthy fact that is emerging from the many Xeon Phi enablement projects in PRACE is that, in many cases, as much programming effort

is needed to obtain performance on the Xeon Phi as is required for programming GPUs. Three separate projects within T7.2 have focused on exploiting OpenMP 4.0 for enabling applications on the Intel Xeon Phi, including CP2K and a QCD application.

With regards to the MPI plus X paradigm for programming heterogeneous systems, we also report here on the exploitation of OmpSs, which is a programming model being developed at Barcelona Supercomputing Center (BSC) and is used in both the Mont-Blanc and DEEP exascale projects and in essence represents an effort to extend the OpenMP model with new directives to support asynchronous parallelism and heterogeneity. However, it can also be understood as new directives extending other accelerator based APIs, like CUDA or OpenCL. With regards to the latter standard, we still find it difficult to gauge whether OpenCL will be more aggressively exploited on the road to exascale. It is a standard that offers a lot in terms of the architectures it can target (including FPGAs as of 2013), but it still lacks a groundswell of support for its ecosystem and as such lags behind CUDA in terms of programmability. Perhaps this will change if Intel puts more support behind the standard as a tool for targeting its Xeon Phi hardware.

Finally, although not exploited during phase 2 of T7.2, we feel it is worth mentioning PGAS languages once again. As mentioned in D7.2.2, investigations into PGAS models have typically been exploratory in nature with no evidence of real applications being enabled with such models to date. (We have, however, found some exceptions to this within several of the exascale projects, e.g., ECMWF's IFS enablement with Co-Array Fortran [3]). Although possibilities for exploiting Partitioned Global Address Space (PGAS) languages on real applications were genuinely explored during the exploitation phase, no real opportunities arose for doing so, possibly reflecting the continuing challenge for exploiting these powerful tools on existing large-scale codes on the road to exascale. However, the benefit of a single language that can be used to efficiently target multi-petascale and future exascale heterogeneous systems in the entirety of their compute hardware space is quite obviously still a welcome prospect.

## 2.1 Porting CP2K to Intel Xeon Phi with mixed-mode MPI/OpenMP in native mode

**WP152:** Evaluating CP2K on Exascale Hardware: Intel Xeon Phi

**Authors:** I Bethune (EPCC) and Fiona Reid (EPCC)

**Application:** CP2K

**HPC Tool/Technique:** MPI, OpenMP, FFTW

**Person Months: 4**

CP2K [4] is a popular, open-source program for atomistic simulation. It provides many levels of theory ranging from classical potential models, DFT using a mixed Gaussian and plane waves approach known as QUICKSTEP [5], to hybrid DFT and post-HF methods (MP2, RPA). In addition, many simulation methods are supported including, molecular dynamics, Monte Carlo, path integrals, nudged elastic band and free energy calculations. These features have made CP2K an increasingly popular tool across the fields of materials science, computational chemistry, solid-state physics and biochemistry. It is widely used throughout Europe, including on the current PRACE RI systems, as well as national and local-scale HPC systems.

As a result, it is of interest to evaluate the performance of CP2K on potential future HPC architectures to ensure the continued viability of the code as HPC providers start looking towards Exascale. One such new architecture is the Intel Xeon Phi [6] (Many Integrated Core,

or MIC) platform, which combines the high performance and low power of e.g. GPUs, with the ease of use of standard x86 CPUs.

Intel supports several standard programming models on the Xeon Phi including the widely used MPI, OpenMP and OpenCL, as well as proprietary interfaces like Intel Thread Building Blocks and Cilk+. Since CP2K already has a mixed-mode MPI and OpenMP parallelisation strategy, we ported the code to the Xeon Phi Platform, and investigated the performance and scalability that could be achieved without significant code modification or tuning.

Since this work was carried out in Q2 2013, shortly after the public release of the Xeon Phi, the PRACE cluster EURORA was not available, and we used a smaller cluster 'Dommic' at CSCS, consisting of 6 nodes each with a Xeon E5-2670 processor and 2 Xeon Phi 5110P coprocessors.

As reported in our PRACE whitepaper, we uncovered and fixed a number of important bugs in the CP2K code, in the Intel Compiler and in Intel's MKL (all of which are now resolved with the Intel Composer XE 2013 SP1 release). We successfully ported CP2K to the Xeon Phi, running in native mode i.e. directly using the Xeon Phi as a many-core computing system, rather than as an accelerator. We evaluated several alternative Fast Fourier Transform libraries (FFTW 3.3.3 compiled for MIC, a pre-release FFTW 3.3.4 with MIC vectorisation support, and Intel MKL). FFTW 3.3.4 and MKL both gave up to a factor of 6 faster performance than the unoptimised FFTW 3.3.3, showing that effective use of the MIC-specific vector instruction set is critical.

When running in mixed-mode MPI/OpenMP mode on the Xeon Phi, the placement of MPI processes and OpenMP threads was found to be very important in achieving maximum performance. A 'balanced' approach where threads are kept close to the parent process while maintaining an even load balance over the Xeon Phi's virtual cores performed best, and this arrangement had to be constructed manually using the MKL\_AFFINITY environment variable.

Finally, we carried out benchmarking using the H2O-64 ab-initio molecular dynamics test case. The best performance obtained on the Xeon Phi used 16 MPI processes each with 15 OpenMP threads, generating a total of 240 threads - fully utilising the Xeon Phi. However, using the host CPU with 16 MPI processes was still around 4x faster.

As a result we have shown that while porting an existing code to the Xeon Phi is relatively straightforward, further effort is needed to extract good performance from the MIC architecture. Analysis of individual routines in CP2K gave us a good understanding of what further development was needed, and work to implement these recommendations was undertaken in the PRACE-1IP Extension and is reported in White Paper 140 [7]

## 2.2 Exploiting MPI 3.0 One-sided Communication for enabling Code\_Saturne on Multi-petaflop/Exascale systems

**WP153:** Enabling Code\_Saturne for Multi-petaflop/Exascale with MPI 3.0 One Sided Communications

**Authors:** C Basu (SNIC-LiU), Soon-Heum Ko (SNIC LiU), C Moulinec (STFC) and Y Fournier (EDF)

**Application:** Code Saturne

**HPC Tool/Technique:** MPI 3.0

**Person Months: 2**

Code\_Saturne [8] is a well-known open-source code for solving Navier-Stokes equations in 2D, 2D-axisymmetric and 3D flows. It can handle steady or unsteady, laminar or turbulent, incompressible, compressible or weakly dilatable, isothermal or non-isothermal cases.

Code\_Saturne is an MPI parallelized code, where its scalability naturally depends on efficient MPI communications. The newly released MPI 3.0 standard [9] has introduced improved Remote Memory Access (RMA) one-sided communication. The lower overhead associated with one-sided communication as compared to two-sided communication has the potential to increase the performance at peta/exascale by increasing the effective network bandwidth and reducing synchronization overheads. As part of this project, we have investigated the impacts of MPI one-sided communication on the Code Saturne.

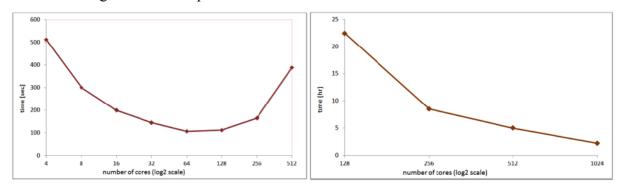

Substantial communication overhead of Code\_Saturne comes from a halo exchange routine named <code>cs\_halo\_sync\_var()</code>. Halo exchange in this routine is implemented by MPI point-to-point routines <code>MPI\_Isend</code>, <code>MPI\_Irecv</code> followed by <code>MPI\_Wait</code>. In this project we have modified the <code>cs\_halo\_sync\_var()</code> routine to replace MPI point-to-point communication with MPI one sided communications. We have implemented two versions of the modified routine using MVAPICH2 implementation of MPI, which has support for both MPI 2.0 and MPI 3.0. The first version (version 1) of our modified routine uses MPI-2.0 one-sided communication routines. For our tests we have taken a test case called "One Tube". The configuration corresponds to the flow in a staggered bundle of tubes [10]. All our tests were carried out on the Triolith cluster, which is an Intel Sandybridge cluster with an Infiniband network interconnect. Timing results for our modified version 1 routine are shown in Table 2.

| MPI<br>processes | Total run time (s) |        | cs_halo_sync_var time(s) |           |

|------------------|--------------------|--------|--------------------------|-----------|

|                  | original version 1 |        | original                 | version 1 |

| 64               | 264.41             | 264.12 | 6.6                      | 6.1       |

| 128              | 152.49 152.11      |        | 7.3                      | 6.8       |

| 256              | 105.89             | 105.96 | 9.2                      | 8.5       |

| 512              | 91.04              | 91.03  | 11.3                     | 10.2      |

Table 2: Scaling results for 'One Tube' test case runs comparing the original two-sided communications vs. the new one-sided communication implementation (version 1)

The modified version 1 of cs\_halo\_sync\_var() shows some performance improvement with respect to the original version. The modified cs\_halo\_sync\_var() subroutine is around 10% faster than the original routine for 512 core runs. However weightage of this routine in the overall runtime is around 10 - 12%. Hence we do not see a proportional reduction in runtime. The version 1 subroutine also has 1-2% less memory overhead compared to the original version. The effects of both timing improvement and less memory consumption are expected to be more prominent when running the code on much larger core/node counts on the road to exascale.

The modified version 2 of cs\_halo\_sync\_var() routine uses the MPI 3.0 one-sided communication routines from the MVAPICH2 MPI implementation. We were not able to run this version as the run crashes with MPI 3.0 routines, indicating that the MPI 3.0 implementation employed is still not very robust. However, we conclude from this project, that it seems adopting MPI one-sided communication in Code\_Saturne can improve its scalability further on the road to exascale when optimized and a stable implementation of MPI 3.0 becomes available.

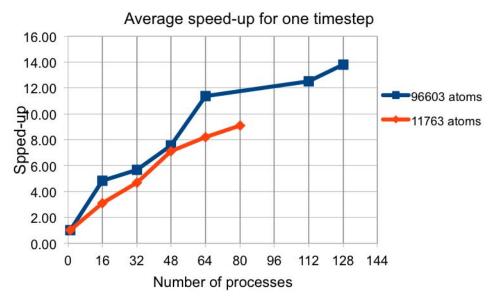

## 2.3 Evaluation of the Effectiveness of OpenACC for enabling DL\_POLY\_4 on the Road to Exascale

**WP156:** An Analysis of State-of-the-art Tools for Preparing DL POLY 4 for Exascale

**Authors:** B B Gursoy (ICHEC) and H Nagel (NTNU)

**Application: DL POLY 4**

HPC Tools/Techniques: OpenACC, CUDA

**Person Months: 2**

DL\_POLY is a well-known parallel large-scale molecular dynamics simulations package developed by I.T. Todorov and W. Smith at the STFC Daresbury Laboratory [11]. The DL\_POLY\_3 package was ported to GPUs, using the CUDA framework by the Irish Centre for High-End Computing (ICHEC) in collaboration with Daresbury Laboratory [12]. Recently, DL\_POLY v4.05.1 has been released with a number of modifications in the source code. Although CUDA provides a significant performance improvement, it is hard to maintain the code in order to keep up with the changes of the vanilla MPI code. This has inspired us to consider OpenACC as an alternative tool that is more easily maintainable on the road to exascale compared to the CUDA framework.