# SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

# INFRA-2010-2.3.1 – First Implementation Phase of the European High Performance Computing (HPC) service PRACE

# PRACE-1IP

# **PRACE First Implementation Project**

**Grant Agreement Number: RI-261557**

# D9.3.4 Final Report on Prototype Evaluation

## **Final**

Version: 1.0

Author(s): Lennart Johnsson, Gilbert Netzer, SNIC/KTH

Date: 19.12.2013

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-261557                                                               |                     |  |  |  |

|---------------|-----------------------------------------------------------------------------------------|---------------------|--|--|--|

|               | Project Title: PRACE First Implementation Project                                       |                     |  |  |  |

|               | Project Web Site: <a href="http://www.prace-project.eu">http://www.prace-project.eu</a> |                     |  |  |  |

|               | Deliverable ID: D9.3.4                                                                  |                     |  |  |  |

|               | Deliverable Nature: Report                                                              |                     |  |  |  |

|               | Deliverable Level: Contractual Date of Delivery:                                        |                     |  |  |  |

|               | PU 31 / December / 2013                                                                 |                     |  |  |  |

|               | Actual Date of Delivery:                                                                |                     |  |  |  |

|               | 30 / December / 2013                                                                    |                     |  |  |  |

|               | EC Project Officer: Leon                                                                | nardo Flores Añover |  |  |  |

<sup>\* -</sup> The dissemination level is indicated as follows: **PU** – Public, **PP** – Restricted to other participants (including the Commission Services), **RE** – Restricted to a group specified by the consortium (including the Commission Services). **CO** – Confidential, only for members of the consortium (including the Commission Services).

## **Document Control Sheet**

|            | Title: Final Report on Prototype Evaluation   |                                            |  |  |

|------------|-----------------------------------------------|--------------------------------------------|--|--|

| Document   | ID: D9.3.4                                    |                                            |  |  |

|            | Version: 1.0                                  | Status: Final                              |  |  |

|            | Available at: <a href="http://w">http://w</a> | ww.prace-project.eu                        |  |  |

|            | <b>Software Tool:</b> Micros                  | oft Word 2007                              |  |  |

|            | <b>File(s):</b> D9.3.4.                       | doc                                        |  |  |

|            | Written by:                                   | Lennart Johnsson, Gilbert Netzer, SNIC/KTH |  |  |

| Authorship | <b>Contributors:</b>                          | Eric Boyer, CINES                          |  |  |

|            |                                               | Paul Carpenter, BSC                        |  |  |

|            |                                               | Radosław Januszewski, PSNC                 |  |  |

|            |                                               | Giannis Koutsou, CaSToRC                   |  |  |

|            |                                               | Ole Widar Saastad, SIGMA/UiO               |  |  |

|            |                                               | Giannos Stylianou, CaSToRC                 |  |  |

|            |                                               | Torsten Wilde, LRZ                         |  |  |

|            | Reviewed by:                                  | Alan Simpson, EPCC                         |  |  |

|            |                                               | Florian Berberich, JUELICH                 |  |  |

|            | Approved by:                                  | MB/TB                                      |  |  |

## **Document Status Sheet**

| Version | Date              | Status        | Comments   |

|---------|-------------------|---------------|------------|

| 0.1     | 13/September/2013 | Draft         | Skeleton   |

| 0.2     | 25/November/2013  | Draft         |            |

| 0.3     | 06/December/2013  | Draft         | For review |

| 1.0     | 19/December/2013  | Final version |            |

# **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure; Prototype Evaluation |

|------------------|-----------------------------------------------------------|

|                  |                                                           |

#### Disclaimer

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° RI-261557. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2013 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-261557 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

# **Table of Contents**

| Pro | oject : | and Deliverable Information Sheet                                             | ii  |

|-----|---------|-------------------------------------------------------------------------------|-----|

| Do  | cume    | nt Control Sheet                                                              | ii  |

| Do  | cume    | nt Status Sheet                                                               | ii  |

| Do  | cume    | nt Keywords                                                                   | iii |

|     |         | Contents                                                                      |     |

|     |         |                                                                               |     |

|     |         | igures                                                                        |     |

|     |         | ables                                                                         |     |

| Re  | feren   | ces and Applicable Documents                                                  | ix  |

| Lis | t of A  | cronyms and Abbreviations                                                     | X   |

|     |         | ve Summary                                                                    |     |

| 1   |         | oduction                                                                      |     |

|     |         |                                                                               |     |

| 2   |         | npute Node Architecture PrototypesAn NVidia Tegra3 SoC with GPU HPC Node, BSC |     |

|     | 2.1     | 2.1.1 Hardware                                                                |     |

|     |         | 2.1.2 Software                                                                |     |

|     |         | 2.1.3 Node architecture prototype measurement setups                          |     |

|     |         | 2.1.4 Measurement results.                                                    |     |

|     |         | 2.1.5 Conclusions                                                             |     |

|     | 2.2     | GPU-GPU communication over PCIe and IB, CaSToRC                               |     |

|     |         | 2.2.1 Experiences with SLURM on scheduling GPUs                               |     |

|     |         | 2.2.2 Power Measurement Characterisation                                      |     |

|     |         | 2.2.3 Energy Efficiency Estimation for Matrix Multiplication                  |     |

|     |         | 2.2.4 HPL Benchmark Performance                                               |     |

|     |         | 2.2.5 Conclusion.                                                             |     |

|     | 2.3     | On die integrated CPU and GPU, PSNC                                           | 18  |

|     |         | 2.3.1 Hardware Description                                                    |     |

|     |         | 2.3.2 Power Measurement Instrumentation                                       |     |

|     |         | 2.3.3 HPL Benchmark Results                                                   | 21  |

|     |         | 2.3.4 Conclusions                                                             | 21  |

|     | 2.4     | DSP based node for HPC, SNIC                                                  | 22  |

|     |         | 2.4.1 Node Instrumentation Update                                             | 22  |

|     |         | 2.4.2 STREAM Benchmark Update                                                 | 23  |

|     |         | 2.4.3 Conclusion                                                              | 24  |

| 3   | Sha     | red memory through a cache-coherency add-in card (NUMA-CIC), UiO              | 26  |

|     | 3.1     | Benchmark Results                                                             |     |

|     |         | 3.1.1 STREAM Shared Memory (OpenMP) Benchmarks                                |     |

|     |         | 3.1.2 MPI Benchmarks                                                          |     |

|     | 3.2     | Experiences with the Prototype                                                |     |

|     |         | 3.2.1 Hardware                                                                |     |

|     |         | 3.2.2 <i>Software</i>                                                         | 31  |

|     |         | 3.2.3 Performance                                                             |     |

|     |         | 3.2.4 Ease of Programming NUMA Systems                                        |     |

|     |         | 3.2.5 Developments tools                                                      | 31  |

|     |         | 3.2.6 Threading libraries, NUMA control and binding                           |     |

|     |         | 3.2.7 Message Passing Interface, MPI                                          | 32  |

|     |         |                                                                               |     |

| 4 | STI         | REAM Benchmark Results Summary                                         | 33 |

|---|-------------|------------------------------------------------------------------------|----|

| 5 | Hol         | istic Approach to Energy Efficiency, LRZ                               | 34 |

|   | 5.1         | Background                                                             |    |

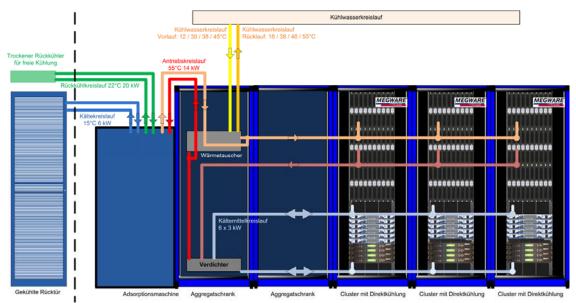

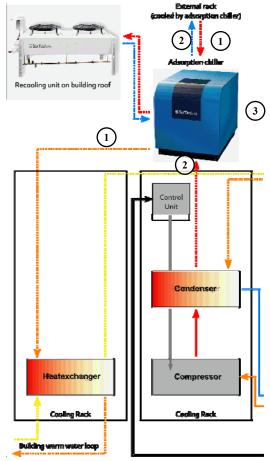

|   | 5.2         | Prototype: Basic Description                                           | 35 |

|   | 5.3         | Internal Infrastructure changes for enhanced monitoring and assessment | 36 |

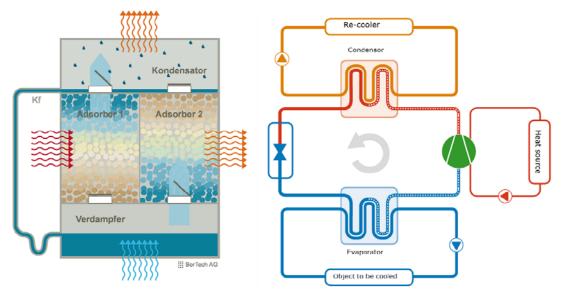

|   | 5.4         | Adsorption                                                             | 37 |

|   | 5.5         | Measurement Setup Adsorption                                           | 38 |

|   | 5.6         | Measurement Results                                                    | 40 |

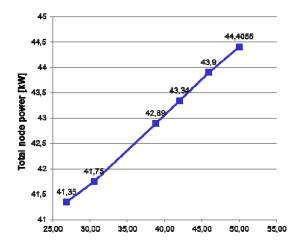

|   |             | 5.6.1 Power consumption vs. cooling water inlet temperature            | 40 |

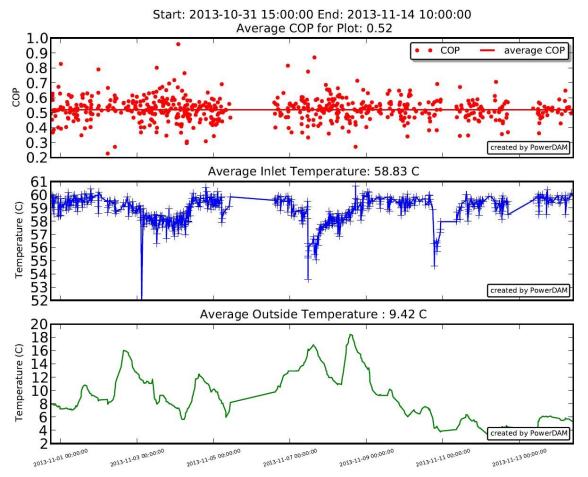

|   |             | 5.6.2 Adsorption chiller COP                                           | 40 |

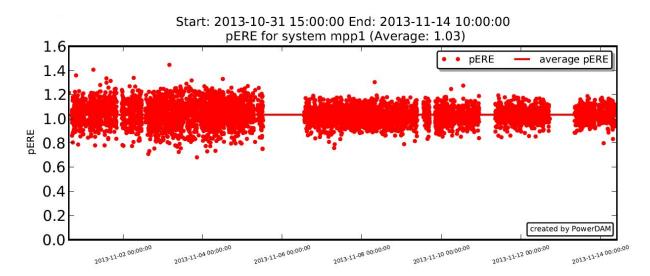

|   |             | 5.6.4 ERE and pERE                                                     | 44 |

|   | <b>5.</b> 7 | Conclusion                                                             | 46 |

|   | 5.8         | Lessons learned                                                        | 47 |

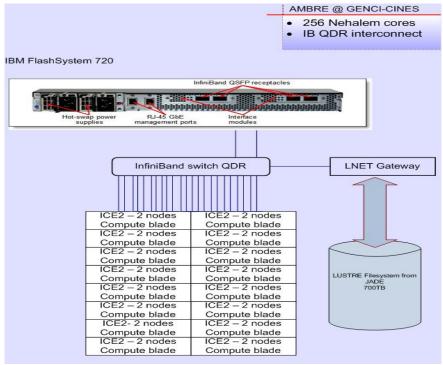

| 6 | Adv         | vanced Multilevel Fault Tolerance (AMFT)                               | 48 |

|   | 6.1         | Key Objectives                                                         | 48 |

|   | 6.2         | Prototype Description                                                  | 48 |

|   |             | 6.2.1 Hardware Description                                             | 48 |

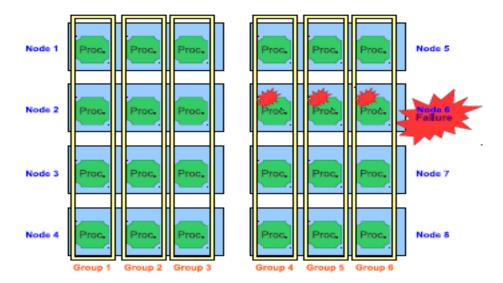

|   | 6.3         | The FTI library                                                        | 51 |

|   | 6.4         | Application impact assessment                                          | 52 |

|   |             | 6.4.1 Hydro results on Curie                                           | 53 |

|   |             | 6.4.2 Gysela5D                                                         | 55 |

|   |             | 6.4.3 SSD assessment                                                   |    |

|   |             | 6.4.4 Conclusion and future directions                                 | 56 |

| 7 | Cor         | nclusion                                                               | 58 |

# **List of Figures**

| Figure 1 Hardware in each BSC-2 node                                                                   | 5                   |

|--------------------------------------------------------------------------------------------------------|---------------------|

| Figure 2 Layout of Pedraforca (BSC-2) racks, each 3U enclosure contains two nodes                      | 5                   |

| Figure 3 InfiniBand network topology for the BSC-2 cluster.                                            | 6                   |

| Figure 4 Node power measurements of the BSC-2 cluster.                                                 | 7                   |

| Figure 5 Bandwidth and energy efficiency of the STREAM benchmark on the BSC-2 prototype                | 9                   |

| Figure 6 Per-node dense matrix-matrix multiplication on the BSC-2 prototype                            |                     |

| Figure 7 Power measurement results on the BSC-2 prototype                                              |                     |

| Figure 8 Power measurements around the end of the 2 GPU matrix-multiply benchmark or                   |                     |

| CaSToRC prototype.                                                                                     |                     |

| Figure 9 Power profile of repeated matrix-matrix multiplication on the CaSToRC prototype               | 14                  |

| Figure 10 Temperature profile captured during 1 GPU benchmark run shown in Figure 9.                   |                     |

| Figure 11 Temperature profiles captured during 2 GPU benchmark run shown in Figure 9                   |                     |

| Figure 12 Power measured during a HPL run using N=34 756 equations on 2 GPUs                           |                     |

| Figure 13 Performance of the HPL benchmark on the CaSToRC prototype.                                   |                     |

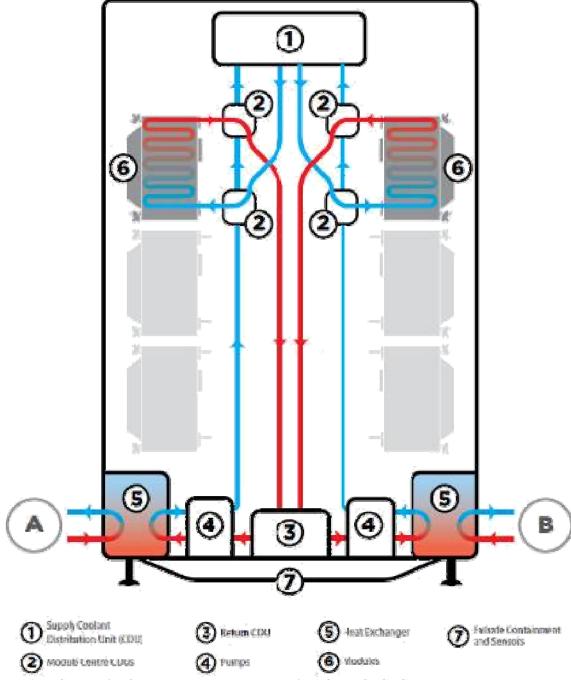

| Figure 14 Illustration of the immersion cooled Iceotope modules of the PSNC-ICE prototype              |                     |

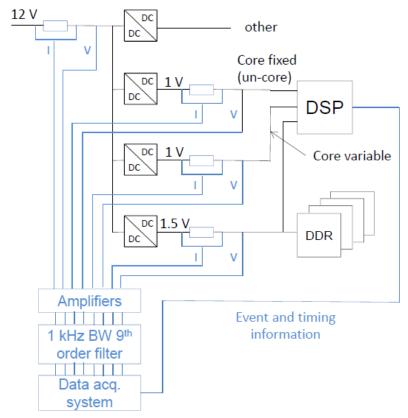

| Figure 15 Schematic of the Iceotope rack water-cooling of the PSNC-ICE prototype                       |                     |

| Figure 16 Schematic of the building water-cooling loop for the PSNC-ICE prototype                      |                     |

| Figure 17 The Lumel P43 3-phase power meter used by the PSNC-ICE prototype                             |                     |

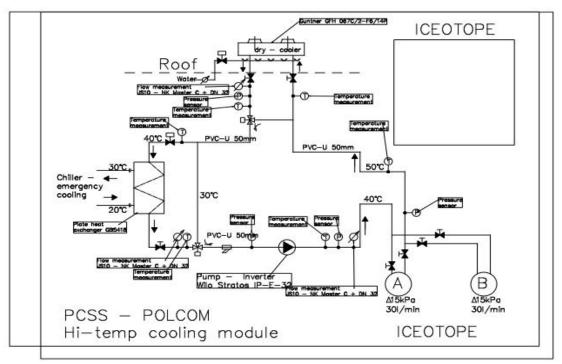

| Figure 18 The power measurement instrumentation of the DSP EVM prototype.                              |                     |

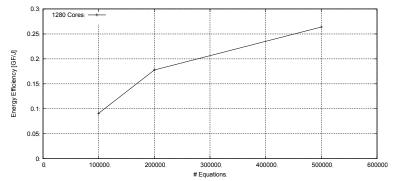

| Figure 19 Bandwidth and Efficiency of the STREAM copy benchmark on the DSP node                        |                     |

| Figure 20 Energy efficiency for the STREAM copy benchmark on the DSP node.                             |                     |

| Figure 21 Performance and efficiency of the STREAM copy benchmark on the UiO prototype                 |                     |

| Figure 22 Bandwidth and energy efficiency for the STREAM benchmarks on the UiO prototype u             |                     |

| 70 nodes                                                                                               | _                   |

| Figure 23 Performance of the Euroben FFT (mod2f) benchmark on the UiO prototype                        |                     |

| Figure 24 MPI Performance for point-to-point operations.                                               |                     |

| Figure 25 MPI performance for all-to-all collective operations.                                        |                     |

| Figure 26 Performance (left) and efficiency (right) of the HPL benchmark on the UiO prototype          |                     |

| Figure 27 Energy efficiency of the HPL benchmark on the UiO prototype                                  |                     |

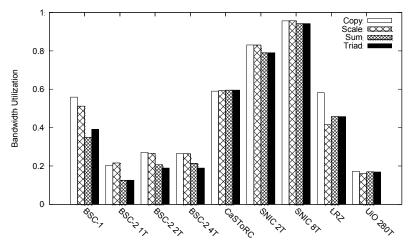

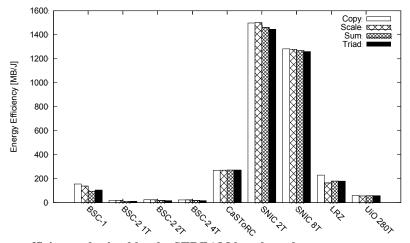

| Figure 28 Bandwidth utilisation for the STREAM benchmark across prototypes                             |                     |

| Figure 29 Energy efficiency obtained by the STREAM benchmark across prototypes                         |                     |

| Figure 30 The CooLMUC experimentation cluster at LRZ.                                                  |                     |

| Figure 31 Schematic of the CooLMUC cooling loops.                                                      |                     |

| Figure 32 Internal view of the SorTech ACS-08 adsorption chiller                                       |                     |

| Figure 33 Schematic of the adsorption chiller.                                                         |                     |

| Figure 34 CooLMUC adsorption measurement points, see also Table 12.                                    |                     |

| Figure 35 CooLMUC node power consumption under max load in relation to water inlet temperat            |                     |

| inguic 33 Coolivioc node power consumption under max load in relation to water infect emperations.     |                     |

| Figure 36 Adsorption chiller Coefficient of Performance (COP), Average inlet temperature,              |                     |

| Average outside air temperature plot.                                                                  |                     |

| Figure 37 SorTech Adsoprtion Chiller Data Sheet.                                                       |                     |

| Figure 38 Heat removed by the adsorption chiller and power consumed by the additional rack (1)         |                     |

| 5)                                                                                                     |                     |

| Figure 39 Partial PUE (pPUE) of the CooLMUC system.                                                    |                     |

| Figure 40 PUE, ERE, and Data Centre Boundary as defined by the Green Grid [GRGRID11]                   | <del>77</del><br>45 |

| Figure 41 Partial ERE, pERE, for the CooLMUC.                                                          | 15                  |

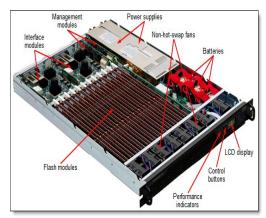

| Figure 42 Illustration of the components of the IBM FlashSystem 720                                    |                     |

| Figure 42 Intustration of the Components of the IBM FlashSystem 720 into the Ambre cluster IB network. | 50<br>50            |

| Figure 44 Grouping of processes into redundancy groups to sustain node failure in FTI                  |                     |

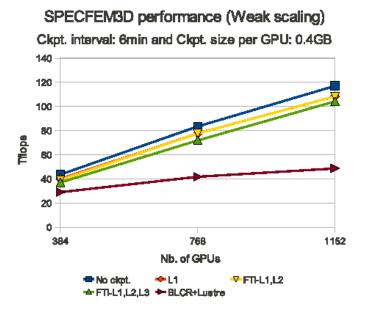

| Figure 45 Weak scaling of SPECFEM3D using no checkpoint (in blue), FTI (in yellow and green)           |                     |

| remote checkpoint on Lustre using BLCR.                                                                |                     |

| Temote eneckpoint on Lustre using DLCK.                                                                | 55                  |

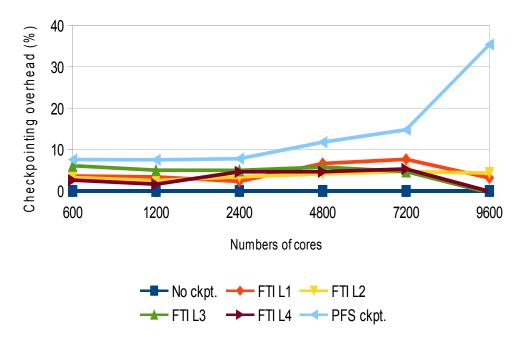

| Figure 46 Overhead of the AMFT approach using the FTI library for various checkpointing lev | ⁄els 54 |

|---------------------------------------------------------------------------------------------|---------|

| Figure 47 Modifications to Hydro to declare the data to be saved by FTI                     | 55      |

| Figure 48 Modification to Hydro to enable FTI based checkpoint/restart.                     | 55      |

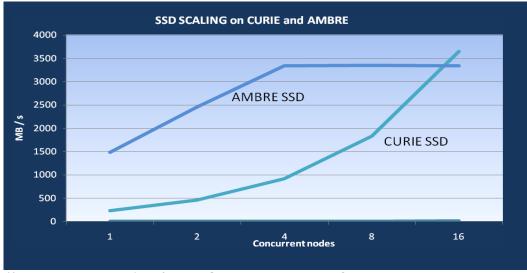

| Figure 49 Measured bandwidth for the IOR benchmark on the QDR IB connected Flashsys         | tem 720 |

| and aggregate bandwidth for Curie nodes with single SATA SSDs.                              | 56      |

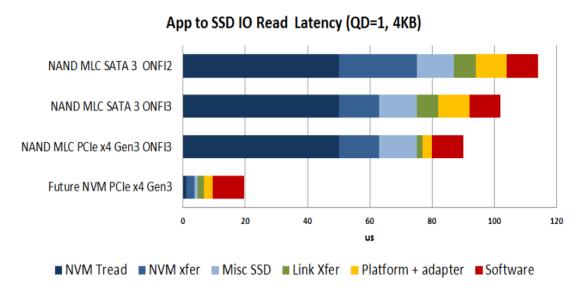

| Figure 50 Estimated performances of future non-volatile memory technologies.                | 57      |

# **List of Tables**

| Table 1 Abbreviations for the prototypes used in the graphs and this report                     | 3    |

|-------------------------------------------------------------------------------------------------|------|

| Table 2 BSC-2 prototype measurement equipment characteristics.                                  | 7    |

| Table 3 STREAM results for the BSC-2 cluster node.                                              | 8    |

| Table 4 STREAM results for the desktop node (same as cluster node exclusive of fan and IB card) | 8    |

| Table 5 Matrix multiplication performance on the CPU and GPU respectively for the cluster node. | 9    |

| Table 6 Performance and energy efficiency for matrix-matrix multiplication on the CaST          | oRC  |

| prototype                                                                                       | 16   |

| Table 7 Performance of the HPL benchmark for varying sizes on 4 GPUs (2 nodes).                 | 17   |

| Table 8 Weak scaling performance for the HPL benchmark on the CaSToRC prototype                 | 17   |

| Table 9 Performance and energy efficiency of the HPL benchmark on the PSNC-ICE prototype        | 21   |

| Table 10 Performance, power and energy efficiency of the STREAM benchmark on the DSP            | 25   |

| Table 11 Bandwidth obtained by the STREAM copy benchmark on the UiO prototype                   | 27   |

| Table 12 CooLMUC adsorption chiller sensors details, see also Figure 34                         | 39   |

| Table 13 Specifications for the IBM FlashSystem 720.                                            | 50   |

| Table 14 Grid sizes and corresponding core counts used for the AMFT assessment for the H        | ydro |

| benchmark                                                                                       | 53   |

**References and Applicable Documents**

[D933] L. Johnsson, G. Netzer. D9.3.3 Report on Prototypes Evaluation. PRACE-

1IP, March 2013.

[FTI] Fault Tolerance Interface. December 2013.

https://gforge.inria.fr/plugins/mediawiki/wiki/fti/images/4/47/FTI-v0.9.1-

DevDoc.pdf

[GREEN500-13] The Green500 List – November 2013.

http://www.green500.org/lists/green201311

[GRGRID] The Green Grid. Homepage, December 2013. http://www.thegreengrid.org

[GRGRID11] D. Azevedo, J. Cooley, M. Patterson, M. Blackburn. Data Center

Efficiency Metrics: mPUE<sup>TM</sup>, Partial PUE, ERE. The Green Grid, 2011. http://www.thegreengrid.org/Global/Content/TechnicalForumPresentation/

2011TechForumDataCenterEfficiencyMetrics

[GRGRID12] V. Avelar, D. Azevedo, A. French. PUE<sup>TM</sup> A Comprehensive Examination

of the Metric. White Paper #49, The Green Grid, 2012.

http://www.thegreengrid.org/sitecore/content/Global/Content/white-papers/WP49-PUEAComprehensiveExaminationoftheMetric.aspx

[GOM11] Leonardo Bautista-Gomez, Seiji Tsuboi, Dimitri Komatitsch, Franck

Cappello, Naoya Maruyama, and Satoshi Matsuoka. FTI: high

performance fault tolerance interface for hybrid systems. In *Proceedings* of 2011 International Conference for High Performance Computing, Networking, Storage and Analysis (SC '11). ACM, New York, NY, USA,

Article 32, 32 pages, 2011. DOI=10.1145/2063384.2063427

http://doi.acm.org/10.1145/2063384.2063427

[GYS5D] Gysela5D: a 5D Gyrokinetic Semi-Lagrangian code. December 2013.

http://gyseladoc.gforge.inria.fr/

[NWE] The New World Encyclopaedia – Adsorption. December 2013.

http://www.newworldencyclopedia.org/entry/Adsorption

[RAJ13] N. Rajovic, A. Rico, J. Vipond, I. Gelado, N. Puzovic, and A. Ramirez.

Experiences With Mobile Processors for Energy Efficient HPC. In Design, Automation & Test in Europe Conference & Exhibition (DATE), pages

464-468, 2013.

[SORTECH] System Chiller Aggregate – Functional Principle. Sortech AG,

December 2013.

http://www.sortech.de/en/architects-designer/functional-principle/system-

chiller-aggregate/

[TACONOVA] TacoSetter Tronic. Taconova, December 2013.

http://www.taconova.com/en/products/pv/hydronic-balancing/1/tacosetter-

tronic/13/

# **List of Acronyms and Abbreviations**

AAA Authorization, Authentication, Accounting.

ACF Advanced Computing Facility

ADP Average Dissipated Power

AMD Advanced Micro Devices

AMFT Advanced Multi-level Fault Tolerant prototype

APGAS Asynchronous PGAS (language)

API Application Programming Interface

APML Advanced Platform Management Link (AMD)

APU Accelerated Processing Unit ARM Advanced RISC Machines

ASIC Application-Specific Integrated Circuit

ATI Array Technologies Incorporated (AMD)

ATLAS Automatically Tuned Linear Algebra Software

BAdW Bayerischen Akademie der Wissenschaften (Germany)

BCO Benchmark Code Owner BCS Bull Coherent Switch

BLAS Basic Linear Algebra Subprograms

BSC Barcelona Supercomputing Centre (Spain)

b/s bits per second

BTL Byte Transfer Layer (OpenMPI)

C3 Cluster Command & Control tools

CAF Co-Array Fortran

CAL Compute Abstraction Layer

CCE Cray Compiler Environment

ccNUMA cache coherent NUMA

CEA Commissariat à l'Energie Atomique (represented in PRACE by GENCI,

France)

CGS Classical Gram-Schmidt

CGSr Classical Gram-Schmidt with re-orthogonalisation

CIC Cache-coherent InterConnect

CINECA Consorzio Interuniversitario, the largest Italian computing centre (Italy)

CINES Centre Informatique National de l'Enseignement Supérieur (represented

in PRACE by GENCI, France)

CLE Cray Linux Environment

COP Coefficient Of Performance

CPU Central Processing Unit

CRAC Computer Room Air-Conditioning

CSC Finnish IT Centre for Science (Finland)

CSCS The Swiss National Supercomputing Centre (represented in PRACE by

ETHZ, Switzerland)

CSR Compressed Sparse Row (for a sparse matrix)

cuBLAS CUDA BLAS library by NVidia

CUDA Compute Unified Device Architecture (NVIDIA)

DAQ Data AcQuisition system

DARPA Defense Advanced Research Projects Agency

DAS Direct Attached Storage

DDN DataDirect Networks

DDR Double Data Rate

DDR3 DDR version 3 DDR3L DDR3 Low voltage

DEISA Distributed European Infrastructure for Supercomputing Applications.

EU project by leading national HPC centres.

DGEMM Double precision General Matrix Multiply DHCP Dynamic Host Configuration Protocol

DIMM Dual Inline Memory Module

DMA Direct Memory Access

DMF Data Migration Facility (SGI)

DNA DeoxyriboNucleic Acid

DP Double Precision, usually 64-bit floating point numbers

DRAM Dynamic Random Access memory

DSP Digital Signal Processor EC European Community ECC Error Correcting Code

EESI European Exascale Software Initiative

Eol Expression of Interest

EP Efficient Performance, e.g., Nehalem-EP (Intel)

EPCC Edinburg Parallel Computing Centre (represented in PRACE by

EPSRC, United Kingdom)

EPSRC The Engineering and Physical Sciences Research Council (United

Kingdom)

eQPACE extended QPACE, name of the FZJ WP8 prototype

ERE Energy Reuse Effectiveness

ESFRI European Strategy Forum on Research Infrastructures; created

roadmap for pan-European Research Infrastructure.

ETHZ Eidgenössische Technische Hochschule Zürich, ETH Zürich

(Switzerland)

EVM EValuation Module (hardware)

EX Expandable, e.g., Nehalem-EX (Intel)

FC Fibre Channel

FFT Fast Fourier Transform

FFTW Fastest Fourier Transform in the West

FHPCA FPGA HPC Alliance FMA Fused Multiply Add FP Floating-Point

FPGA Field Programmable Gate Array

FPU Floating-Point Unit FTI Fault Tolerant Interface

FZJ Forschungszentrum Jülich (Germany)

GASNet Global Address Space Networking

GbE Giga (=  $2^{30} \sim 10^9$ ) bit per second Ethernet GB Giga ( $10^9$ ) Bytes (= 8 bits), also GByte Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GCS Gauss Centre for Supercomputing (Germany)

GDDR Graphic Double Data Rate memory

GDDR5 GDDR version 5

GÉANT Collaboration between National Research and Education Networks to

build a multi-gigabit pan-European network, managed by DANTE.

GÉANT2 is the follow-up as of 2004.

Gen Generation

GENCI Grand Equipement National de Calcul Intensif (France)

GFlop/s Giga (= 10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also GF/s

GHz Giga (= 10<sup>9</sup>) Hertz, frequency =10<sup>9</sup> periods or clock cycles per second

GiB 2<sup>30</sup> bytes

GigE Gigabit Ethernet, also GbE GLSL OpenGL Shading Language GNU GNU's not Unix, a free OS

GPFS General Parallel File System (IBM)

GPGPU General Purpose GPU

GPIO General Purpose I/O (hardware)

GPU Graphic Processing Unit GRES Generic RESource

GROMACS GROenigen MAchine for Chemical Simulations

GS Gram-Schmidt

GWU George Washington University, Washington, D.C. (USA)

HBA Host Bus Adapter HCA Host Channel Adapter

HCE Harwest Compiling Environment (Ylichron)

HDD Hard Disk Drive HE High Efficiency

HET High Performance Computing in Europe Taskforce. Taskforce by

representatives from European HPC community to shape the European HPC Research Infrastructure. Produced the scientific case and valuable

groundwork for the PRACE project.

HMM Hidden Markov Model

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hewlett-Packard

HPC High Performance Computing; Computing at a high performance level

at any given time; often-used synonym with Supercomputing

HPCC HPC Challenge benchmark, http://icl.cs.utk.edu/hpcc/ HPCS High Productivity Computing System (a DARPA program)

HPL High Performance Linpack

HT HyperTransport channel (AMD)

HTX HyperTransport Expansion

HWA HardWare Accelerator

IB InfiniBand IBA IB Architecture

IBM Formerly known as International Business Machines

ICE (SGI)

IDRIS Institut du Développement et des Ressources en Informatique

Scientifique (represented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IESP International Exascale Project

IL Intermediate Language IMB Intel MPI Benchmark

I/O Input/Output

IOR Interleaved Or Random

IP Internet Protocol

IPMI Intelligent Platform Management Interface

IPoIB IP over IB

ISC International Supercomputing Conference; European equivalent to the

US based SC0x conference. Held annually in Germany.

iWARP Internet Wide Area RDMA Protocol

IWC Inbound Write ControllerJBOD Just a Bunch of DisksJKU Johannes Kepler University

JSC Jülich Supercomputing Centre (FZJ, Germany) KB Kilo (=  $2^{10} \sim 10^{3}$ ) Bytes (= 8 bits), also KByte

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC,

Sweden)

LBE Lattice Boltzmann Equation

Linpack Software library for Linear Algebra

LLNL Laurence Livermore National Laboratory, Livermore, California (USA)

LQCD Lattice QCD

LRZ Leibniz Supercomputing Centre (Garching, Germany)

LS Local Store memory (in a Cell processor)

LU Lower times Upper triangular (factorization)

MAID Massive Array of Idle Disks

MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (= 10<sup>6</sup>) Bytes (= 8 bits) per second, also MByte/s

MDT MetaData Target

MFC Memory Flow Controller

MFlop/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also MF/s

MGS Modified Gram-Schmidt

MHz Mega (= 10<sup>6</sup>) Hertz, frequency =10<sup>6</sup> periods or clock cycles per second

MiB 2<sup>30</sup> bytes

MIPS Originally Microprocessor without Interlocked Pipeline Stages; a RISC

processor architecture developed by MIPS Technology

MJ Mega (=  $10^6$ ) Joule

MKL Math Kernel Library (Intel)

ML Maximum Likelihood

MLC Multi-Level Cell

Mop/s Mega (=  $10^6$ ) operations per second (usually integer or logic operations)

MoU Memorandum of Understanding.

MPI Message Passing Interface

MPP Massively Parallel Processing (or Processor)

MPT Message Passing Toolkit MRAM Magnetoresistive RAM

MTAP Multi-Threaded Array Processor (ClearSpead-Petapath)

MUNGE MUNGE Uid 'N' Gid Emporium (SLURM plugin)

MySQL Open source relational database

mxm DP matrix-by-matrix multiplication mod2am of the EuroBen kernels

NAMD Not (just) Another Molecular Dynamics program

NAND Negated AND (gate)

NAS Network-Attached Storage

NB Block size (for matrices)

NC-BTL NumaConnect Byte Transfer Layer (see BTL, OpenMPI)

NCF Netherlands Computing Facilities (Netherlands)

NDA Non-Disclosure Agreement. Typically signed between vendors and

customers working together on products prior to their general

availability or announcement.

nm nano (= 10-9) meter NoC Network-on-a-Chip NFS Network File System

NIC Network Interface Controller

NIS Network Information Service

NSD Network Shared Disk (IBM/GPFS)

NUMA Non-Uniform Memory Access or Architecture

NVRAM Non-Volatile RAM

OFED OpenFabrics Enterprise Distribution

OmpSs OpenMP StarSs programming model

OpenCL Open Computing Language

OpenGL Open Graphic Library

Open MP Open Multi-Processing

OS Operating System

OSS Object Storage Server

OST Object Storage Target

PAM Pluggable Authentication Module

PB Peta (=2<sup>50</sup>) Bytes

PCI peripheral Component Interconnect

PCIe Peripheral Component Interconnect express, also PCI-Express

PCI-X Peripheral Component Interconnect eXtended

PCM Phase Change Memory

pERE Partial ERE

PFS Parallel File System

PGAS Partitioned Global Address Space

PGI Portland Group, Inc.

pNFS Parallel Network File System

POSIX Portable OS Interface for Unix

PPE PowerPC Processor Element (in a Cell processor)

pPUE Partial PUE

PRACE Partnership for Advanced Computing in Europe: Project Acronym

PRACE-1IP PRACE 1<sup>st</sup> Implementation Phase

PSCC Poznanskie Centrum Superkomputerowo - Sieciowe

PSNC Poznan Supercomputing and Networking Centre (Poland)

PSNC-BR PSNC AMD Brazos prototype

PSNC-IB PSNC Intel Ivy Bridge prototype

PSNC-ICE PSNC Iceotope protoype

PSNC-LL PSNC AMD Llano prototype

PSNC-SB PSNC Intel Sandy Bridge prototype

PSNC-TR PSNC AMD Trinity prototype

PSU Power Supply Unit

PUE Power Usage Effectiveness QCD Quantum Chromodynamics

QCDOC Quantum Chromodynamics On a Chip

QDR Quad Data Rate

QPACE QCD Parallel Computing on the Cell

QR — QR method or algorithm: a procedure in linear algebra to compute the

eigenvalues and eigenvectors of a matrix

RAID Redundant Array of Inexpensive Disks

RAM Random Access Memory

RCUDA Remote CUDA

RDMA Remote Data Memory Access

RISC Reduce Instruction Set Computer

RNG Random Number Generator

ROI Return On Investment RPM Revolution per Minute

RS-232 Radio Sector 232 standard by the Electronic Industries Association

RTM Reverse Time Migration SAN Storage Area Network

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SAS Serial Attached SCSI

SATA Serial Advanced Technology Attachment (bus)

SCS SuperComputing Solutions (a CINECA company)

SDK Software Development Kit

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SHMEM Share Memory access library (Cray)

SHOC Scalable HeterOgeneous Computing

SIMD Single Instruction Multiple Data

SLC Single Level Cell

SLURM Simple Linux Utility for Resource Management SM Streaming Multiprocessor, also Subnet Manager

SM-BTL Shared Memory Byte Transfer Layer (see BTL, OpenMPI)

SMP Symmetric MultiProcessing

SMX Streaming Multiprocessor (see also SM)

SNIC Swedish National Infrastructure for Computing (Sweden)

SoC System-on-a-Chip

SP Single Precision, usually 32-bit floating point numbers

SPE Synergistic Processing Element (core of Cell processor)

SPH Smoothed Particle Hydrodynamics

SPU Synergistic Processor Unit (in each SPE)

SSD Solid State Disk or Drive

SSU Scalable Storage Unit (Xyratex)

STFC Science and Technology Facilities Council (represented in PRACE by

EPSRC, United Kingdom)

STRATOS PRACE advisory group for STRAtegic TechnOlogieS

STREAM Streaming memory benchmark

STT Spin-Torque-Transfer

TARA Traffic Aware Routing Algorithm

TB Tera (= 240 ~ 1012) Bytes (= 8 bits), also TByte

TCO Total Cost of Ownership. Includes the costs (personnel, power, cooling,

maintenance, ...) in addition to the purchase cost of a system.

TDP Thermal Design Power

TFlop/s Tera (= 10<sup>12</sup>) Floating-point operations (usually in 64-bit, i.e. DP) per

second, also TF/s

TGCC Tres Grand Centre de Calcul

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the Tier-0 systems; national or topical HPC centres would constitute Tier-1

TMS Texas Memory System

U Rack unit = 1.75 inches = 44.45 mm

UEABS Unified European Application Benchmark Suite

UFM Unified Fabric Manager (Voltaire)

UiO University in Oslo, Norway

UNICORE Uniform Interface to Computing Resources. Grid software for seamless

access to distributed resources.

UPC Unified Parallel C UV Ultra Violet (SGI)

UVA Unified Virtual Addressing (NVIDIA)

μSD Micro Secure Digital

VHDL VHSIC (Very-High Speed Integrated Circuit) Hardware Description

Language

VTL Virtual Tape Library

X86 Instruction set architectures backward compatible with the Intel 8086

CPU

X86-64 x86 64-bit instruction set architectures

xCAT EXtreme Cloud Administration Toolkit (IBM)

# **Executive Summary**

This report supplements deliverable D9.3.3 [D933] and covers future technology prototype efforts from March 2013. Three prototype efforts not reported on in D9.3.3 are fully reported here: the ARM based NVidia Tegra3 with NVidia Kepler GPU acceleration prototype at BSC; the energy recovery prototype using immersive cooling techniques at PSNC; and the results from the Advanced Multi-level Fault Tolerant prototype. Additional results are provided for the x86+GPU prototype at CaSToRC, the DSP prototype at SNIC/KTH, and the energy recovery prototype at LRZ.

The DSP results show that for the benchmarks that were well optimised the observed energy efficiency for the DSP was in line with the nominal energy efficiency that can be derived from specifications. Thus, the energy efficiency is comparable to that of GPUs and better than that of x86 CPUs. Furthermore, the DSP does not require a host processor. In fact, the 40 nm DSP used is, for the optimised benchmarks, more energy efficient than correspondingly optimised codes for the 22 nm Intel Ivy Bridge. ARM Coretx-A9 CPUs are not energy efficient for HPC workloads, but nodes using powerful and energy efficient acceleration, such as the NVidia Kepler, can form part of a viable HPC node. Due to late delivery of the relevant prototype only preliminary results are available at this time.

The shared memory prototype is based on standard x86 servers and a node add-in card for cache coherency. This prototype clearly demonstrated that, though a very large shared memory address space is supported, it is a NUMA architecture and paying proper attention to the memory architecture is necessary for good performance.

One of the lessons learnt in the project is that delivering energy efficiency advantages for architectures different from x86 architectures requires well-optimised codes also for the non-x86 architectures, i.e. for significant energy efficiency gains at the application level resource use needs to be at a level comparable to that for x86 architectures. High resource utilization requires detailed understanding of the alternative architectures as well as developing or inventing new programming methodologies and techniques in a less-rich software ecosystem than that available for x86 architectures today. It also became apparent that quality energy efficiency assessment adds significant complexity to benchmarking, in that instrumentation and measurement technologies as well a good understanding of applications and system behaviours are all necessary.

For the energy recovery approach assessed by the LRZ prototype it was demonstrated that a 20% energy recovery could be achieved even for the partially hot-water liquid cooled system Valuable insights were also gained into how the approach used can be improved for increased energy recovery. The immersive cooling prototype at PSNC exposed some of the many engineering issues in integrating new cooling technologies in a data centre setting.

The Advanced Multi-level Fault Tolerant approach to checkpoint/restart was demonstrated to have good scalability and sufficiently low overhead to allow for frequent checkpointing even at a large scale.

#### 1 Introduction

This deliverable is a supplement to deliverable D9.3.3 covering the period March – December 2013. Deliverable D9.3.3 provides the background for the Future Technologies prototype efforts within the PRACE-1IP Work-Package 9 (WP9) and is still valid and so is not repeated in this deliverable. [D933] The main focus of the PRACE-1IP WP9 efforts was on technologies for energy efficient HPC systems, especially large-scale systems. High energyefficiency does require high efficiency in resource utilization. With current technologies for power management and system architectures poor efficiency in utilizing system resources result in unnecessary (high) energy consumption. Therefore the WP9 efforts have had a strong emphasis on assessing the ability and efforts to achieve high efficiency and scalability, in addition to a focus on architectures with low power design objective, such as architectures for mobile and embedded markets. Also, high efficiency and energy efficiency require highly reliable or fault tolerant systems in order for computations not to need to be attempted time and again from the start for a successful outcome. This latter issue is addressed by the Advanced Multi-level Fault Tolerance (AMFT) prototype, a prototype effort that was not reported on in D9.3.3. Another prototype effort that was not covered in D9.3.3 is the assessment of achievable energy efficiency of clusters based on nodes using ARM CPUs with NVidia GPU accelerators and high-performance interconnect. A third prototype, PSNC-ICE, exploring immersive cooling technologies for energy recovery is also reported on here for the first time. For all three prototypes delayed delivery and/or engineering issues associated with new technologies are the reasons for results not being included in D9.3.3. Stability problems with the shared-memory system, based on the use of a cache-coherency add-in card that prevented other than highly preliminary information in D9.3.3, have been resolved; this allowed for STREAM, HPL and MPI benchmark results to be reported here together with a report on experiences in using the large core-count NUMA shared-memory system. This deliverable also reports on additional results and insights gained from the DSP, the x86+GPU and energy recovery prototypes.

Table 1 lists the various prototypes in PRACE-1IP WP9 and indicates which prototype efforts are reported for the first time here (added) and for which this deliverable provides supplementary information (updated).

The organization of this deliverable follows that of D9.3.3 with architectural prototype efforts reported first, followed by a report of new results and insights related to energy recovery from HPC system cooling systems. The report from the AMFT prototype is reported last.

| Abbreviation | Prototype Name                                                     |                                      | Site            | Reported<br>in |

|--------------|--------------------------------------------------------------------|--------------------------------------|-----------------|----------------|

| BSC-1        | An NVidia Tegra 2 mobile SoC based HPC cluster                     |                                      | BSC             | D 9.3.3        |

| BSC-2        | An NVidia Tegra 3 SoC w                                            | ith GPU HPC Node                     | BSC             | D 9.3.4        |

| CaSToRC      | GPU-GPU communicatio                                               | n over PCIe and IB                   | CaSToRC         | Both           |

| CEA          | Exascale I/O                                                       |                                      | CEA/CINES       | D 9.3.3        |

| FZJ          | Exascale integrated I/O s                                          | ubsystem                             | FZJ             | D 9.3.3        |

| JKU          | FPGA matrix computatio                                             | FPGA matrix computation acceleration |                 | D 9.3.3        |

| LRZ          | Holistic approach to energy efficiency                             |                                      | LRZ             | Both           |

| PSNC-BR      | On die integrated CPU                                              | AMD E-350                            | PSNC            | D 9.3.3        |

| PSNC-IB      | and GPU                                                            | Intel i7-3770                        |                 | D 9.3.3        |

| PSNC-LL      |                                                                    | AMD A8-3870                          |                 | D 9.3.3        |

| PSNC-SB      |                                                                    | Intel i7-2600                        |                 | D 9.3.3        |

| PSNC-TR      | _                                                                  | AMD A10-5800K                        | _               | D 9.3.3        |

| PSNC-ICE     |                                                                    | Intel Xeon E5-<br>2620               |                 | D 9.3.4        |

| SNIC         | DSP based node for HPC                                             |                                      | SNIC/KTH        | Both           |

| UiO          | Shared memory through a cache-<br>coherency add-in card (NUMA-CIC) |                                      | UiO             | Both           |

| AMFT         | Advanced Multi-level Fau                                           | ult Tolerance                        | GENCI/CEA/CINES | D 9.3.4        |

Table 1 Abbreviations for the prototypes used in the graphs and this report.

# 2 Compute Node Architecture Prototypes

Results on the ARM based prototype with GPU acceleration are reported first, followed by an update on the GPU to GPU communication prototype, some very preliminary first results from the immersion cooling prototype and updated results from the DSP HPC node prototype. This is the same order as in the original D9.3.3 deliverable.

### 2.1 An NVidia Tegra3 SoC with GPU HPC Node, BSC

The BSC-2 prototype is a hybrid accelerator prototype based on ARM SoCs, NVidia Tesla K20 GPUs and an QDR InfiniBand (40 Gb/s) interconnect. It has considerably higher compute performance and network bandwidth than the previous BSC-1 prototype. This prototype is currently being used to test the portability and scalability of scientific applications that previously executed on GPU-accelerated x86-64 multicore clusters. Of special interest are the impact of the host's low (CPU) performance, memory capacity and memory bandwidth, and the benefits of its low power consumption.

Results for this prototype are reported for the first time in this deliverable.

#### 2.1.1 Hardware

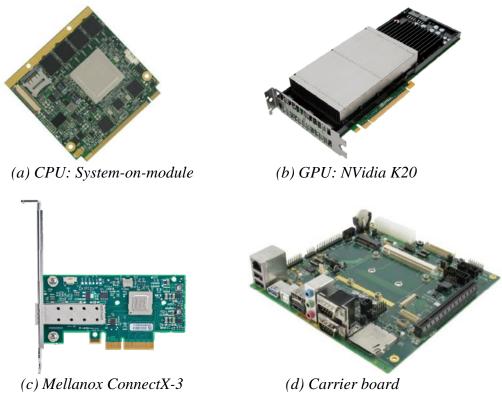

The prototype is composed of 72 compute nodes, each of which contains the components shown in Figure 1(a-d). The system-on-module (a) has one NVidia Tegra 3 SoC with four ARM Cortex-A9 cores clocked at 1.3 GHz, a single 32-bit memory channel and 2 GiB 1500 MHz DDR3L DRAM. The peak floating-point performance is 5.2 GF/s (double precision, 10.4 GF/s single precision) and the peak memory bandwidth 6 GB/s. The prototype nodes support 4 lanes¹ of PCIe Gen 2.0. The NVidia Tesla K20 GPU (b) has one GK110 GPU containing 2,496 cores in 13 Streaming Multiprocessors (SMX) and 5 GiB of GDDR5 memory, giving a compute performance of 1.17 TF/s (double precision, 3.53 TF/s single precision). The Mellanox ConnectX-3 (c) connects the node to the QDR InfiniBand interconnect at 40 Gb/s. A PCIe riser card (not shown) allows the GPU and InfiniBand card to share a single PCIe connector. The carrier board (d) holds the system-on-module daughter board, has one PCI connector, and provides all external interface connectors except InfiniBand. A 256 GB Samsung SSD provides node local storage.

All components for two nodes are contained in a 3U chassis. The prototype hardware also includes a single node in a desktop form factor. The latter configuration does not include the PCIe riser and the InfiniBand card, but is otherwise the same.

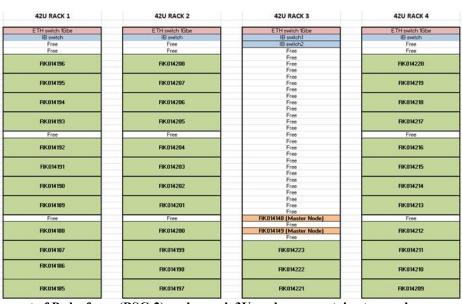

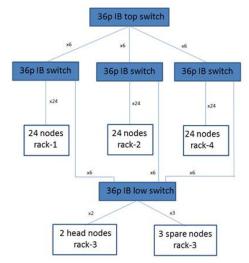

The full system is assembled into four Bull bullx 1200 (42U) racks, as shown in Figure 2. In addition to the 72 compute nodes, there are six spare nodes, two login nodes, four 1GbE switches for storage, five 36-port QDR InfiniBand switches for the MPI interconnect, and space reserved for an NFS server. Each login node has two processor sockets, each containing an Intel Xeon E5-2620, as well as 32 GiB 1600 MHz DDR3 DRAM, two 500 GB SATA disks in a RAID 1 configuration, four 1GbE ports and one QDR InfiniBand ConnectX-3 interface.

The complete prototype provides a peak nominal performance of 84.2 TF/s (double precision)

<sup>&</sup>lt;sup>1</sup> Tegra 3 supports up to six lanes of PCIe, but only with three devices, each with 2 lanes, which is not the configuration used in this prototype.

at 18.7 kW² power consumption resulting in a peak energy efficiency of 4.5 GF/J based on the nominal peak performance, measured peak power consumption and maximum specified power for the switches. This nominal energy efficiency shows potential for competitive realised energy efficiency compared to current systems, if a good fraction of the peak performance is achieved in applications. For comparison, the highest HPL (High-Performance Linpack) energy efficiency in the November 2013 Green 500 list is 4.5 GF/J (TSUBAME-KFC, Tokyo Institute of Technology), also using NVidia K20 accelerator technology.

Figure 1 Hardware in each BSC-2 node.

Figure 2 Layout of Pedraforca (BSC-2) racks, each 3U enclosure contains two nodes.

\_

<sup>&</sup>lt;sup>2</sup> Total double precision performance: 72 nodes, each at 1.17 TF/s. Total power consumption including InfiniBand and Ethernet switches: 72 nodes, measured at 250 W each, plus five InfiniBand 36-port InfiniScale IV QDR, each 122 W, plus 4 four 26-port SMC8126L2 Ethernet switches, each at 38 W The total power consumption is equivalent to 260 W per node.

The prototype has two independent physical networks. The MPI interconnect, as shown in Figure 3, uses QDR InfiniBand (40 Gb/s) with a two-level tree topology. The storage network connects to the outside world and storage via 1GbE.

Figure 3 InfiniBand network topology for the BSC-2 cluster.

#### 2.1.2 Software

Login node 1 is focused on user activities. It includes the SLURM (Simple Linux Utility for Resource Management) resource and queue manager and the NFS server for the cluster. Login node 2 is focused on administrative tasks. It runs the NIS (Network Information Service) user management, the Ganglia monitor and the DHCP (Dynamic Host Control Protocol) server for the cluster. Both login nodes have the C3 (Cluster Command & Control) parallel shell installed.

The prototype supports native compilation on the nodes, including C, C++ and Fortran, as well as CUDA 5.5 and OpenCL. The Mercurium-based compiler has been installed for OmpSs (multi-core only, excluding GPU). Library support includes OpenMPI, OpenMP and BLAS, as well as other libraries developed for the prototype effort.

Target applications for the prototype, which have already been ported to x86 + GPU, include:

- RTM (Kaleidoscope project with Repsol), ELIAUS (Pegase project with PROMES)

- NAMD, GROMACS (both part of the PRACE benchmark suite)

- HPL

- GPU offloading using RCUDA

# 2.1.3 Node architecture prototype measurement setups

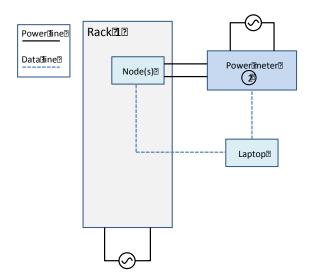

For energy-to-solution assessment, the power measurement setup summarised in Table 2 was used. Voltage and current at the 220 V AC input to the node(s) was measured using a Yokogawa WT230 power meter, as illustrated in Figure 4. The power measurements include losses in the PSU (Power Supply Unit), as well as the power consumption of the forced aircooling.

19.12.2013

| No. | Device   | Scope/Purpose        | Measurand        | Error       | Sampling |

|-----|----------|----------------------|------------------|-------------|----------|

| 1   | Yokogawa | Power measurement    | Active power (W) | $\pm 0.2\%$ | 4/sec    |

|     | WT230    | of a subset of nodes | Voltage (V)      |             |          |

|     |          |                      | Current (A)      |             |          |

Table 2 BSC-2 prototype measurement equipment characteristics.

Results are reported for one or two nodes. Although two nodes share a 3U chassis, the power consumption of a single node can be isolated, since the two nodes have separate AC inputs. The measurements are scaled with the number of nodes that were included in the benchmark. We verified that the per-node load does not vary significantly among the nodes within a run, so that measuring a single node's power and scaling it to the whole system does not introduce a significant error. The power consumption of the various nodes inside a rack is expected to depend only on the workload, and to be independent of the node's location inside the rack. Since all fans are always running at full speed, we do not expect the nodes in less well-ventilated parts of the rack to incur higher power consumption from the fans. The power consumption of the networking equipment has not yet been measured.

Figure 4 Node power measurements of the BSC-2 cluster.

During power measurements, due to the problems with SLURM mentioned in the conclusions, the job scheduler was bypassed and jobs directly mapped to nodes using the mpiexec command. The power meter was connected to a laptop using a serial cable. A driver script was used to fully automate the process of collecting data; the laptop was instructed to collect power measurements while the benchmark was running.

#### 2.1.4 Measurement results

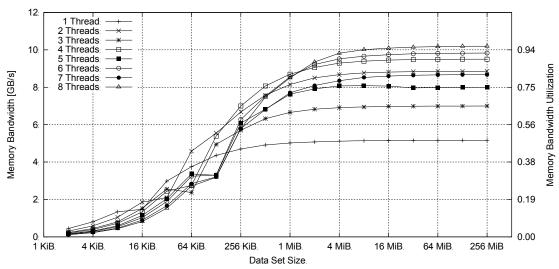

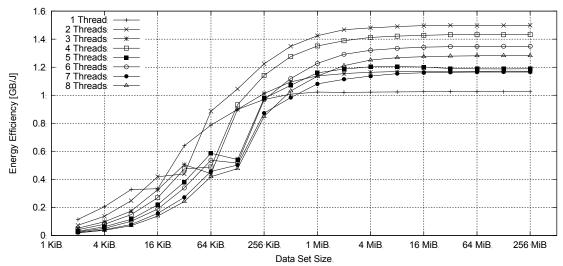

#### STREAM

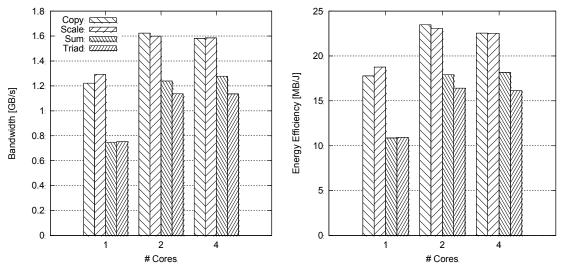

Version 5.10 of the STREAM benchmark was used out of the box with no hand optimisation. The only changes made were to allow for separate power measurement of each operation: copy, scale, sum and triad. STREAM was compiled using GCC 4.6.3 and the flags "-Ofast-mcpu=cortex-a9 -mtune=cortex-a9 -mfloat-abi=hard -vfpu=vfpv3-d16". These flags were found to create the best results; since the ARM Cortex-A9 Neon unit has scalar double-precision support, there was no benefit from "-fpu=neon -ftree-vectorise". The throughput results are shown in Table 3 for the cluster node and Table 4 for the desktop node. OpenMP

was used for multi-threaded benchmarks. Figure 5 shows the results for the cluster node.

It is likely that the performance results could be considerably improved by hand-optimising the implementation of the STREAM benchmark, but that has not yet been done. Though the efficiency at best reaches about 27%, it appears that practically the peak efficiency is reached for two threads, and that the energy efficiency is reduced for four threads, i.e. when all cores are used. From an energy-efficiency perspective two threads are optimal with the current STREAM benchmark implementation. It is also interesting to observe that two threads (with increased memory activity and two active cores) increased the power consumption with 0.3 - 0.4 W for copy and scale compared to a single thread. Adding two additional threads/cores increased the power consumption with about 1.1 - 1.2 W (or about 0.6 W/core) for the two added active cores, without a significant increase in performance or memory activity.

| Op.   | Threads | Perf.  | Power | Eff. | E.Eff. |

|-------|---------|--------|-------|------|--------|

|       |         | [MB/s] | W     | %    | [MB/J] |

| Сору  | 1       | 1229   | 68.8  | 20.5 | 17.86  |

|       | 2       | 1633   | 69.2  | 27.2 | 23.60  |

|       | 4       | 1633   | 70.3  | 27.2 | 23.23  |

| Scale | 1       | 1299   | 69.0  | 21.7 | 18.83  |

|       | 2       | 1610   | 69.4  | 26.8 | 23.20  |

|       | 4       | 1591   | 70.5  | 26.5 | 22.57  |

| Sum   | 1       | 750    | 68.9  | 12.5 | 10.89  |

|       | 2       | 1247   | 69.2  | 20.8 | 18.02  |

|       | 4       | 1281   | 70.4  | 21.4 | 18.20  |

| Triad | 1       | 755    | 68.9  | 12.6 | 10.96  |

|       | 2       | 1140   | 69.3  | 19.0 | 16.45  |

|       | 4       | 1154   | 70.4  | 19.2 | 16.39  |

Table 3 STREAM results for the BSC-2 cluster node.

| Op.   | Threads | Perf.  | Power | Eff. | E.Eff. |

|-------|---------|--------|-------|------|--------|

|       |         | [MB/s] | W     | %    | [MB/J] |

| Сору  | 1       | 1229   | 32.3  | 20.5 | 38.05  |

|       | 2       | 1633   | 32.7  | 27.2 | 49.94  |

|       | 4       | 1633   | 33.9  | 27.2 | 48.17  |

| Scale | 1       | 1299   | 32.3  | 21.7 | 40.22  |

|       | 2       | 1610   | 32.9  | 26.8 | 48.94  |

|       | 4       | 1591   | 34.1  | 26.5 | 46.66  |

| Sum   | 1       | 750    | 32.4  | 12.5 | 23.15  |

|       | 2       | 1247   | 32.7  | 20.8 | 38.13  |

|       | 4       | 1281   | 33.9  | 21.4 | 37.79  |

| Triad | 1       | 755    | 32.7  | 12.6 | 23.09  |

|       | 2       | 1140   | 32.8  | 19.0 | 34.76  |

|       | 4       | 1154   | 34.1  | 19.2 | 33.84  |

Table 4 STREAM results for the desktop node (same as cluster node exclusive of fan and IB card).

Figure 5 Bandwidth and energy efficiency of the STREAM benchmark on the BSC-2 prototype.

## Dense matrix multiply benchmark

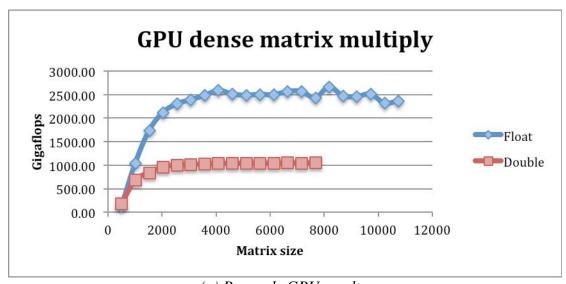

The dense matrix multiply code from the Mont-Blanc kernel benchmarks [RAJ13] was used together with the auto-tuned ATLAS 3.11.14 library for the ARM CPUs and with the CUBLAS 5.5.22 library from CUDA-5.5 for the GPUs. The GPU results are 2.5 TF/s single precision (71.0% efficiency) and 1.04 TF/s double precision (88.9% efficiency). The corresponding energy efficiencies are 10.16 GF/J for single precision at a node power consumption of 246 W and 4.19 GF/J for double precision at a node power consumption of 248 W. The former is achieved for matrices of size 3584 and above, which is 51 MB per matrix, and the latter is achieved for matrices of size 2048 or above, which is about 34 MB per matrix. The results are shown in Table 5 and Figure 6.

The peak observed dense matrix multiplication performance of a single ARM Cortex-A9 core was 1.6 GF/s in single precision (61.5% efficiency) and 0.9 GF/s in double precision (69.2% efficiency). With OpenMP, the performance with four threads increased to 5.16 GF/s in single precision (49.6% efficiency) and 2.43 GF/s double precision (46.7% efficiency). Unfortunately, large power overheads mean that the CPU-only results achieve poor energy efficiency. As described on page 10, the CPU, memories and other active components account for less than 25% of the power consumption; the rest is consumed by the inactive GPU and fans. However, it is interesting to note that; for single precision, adding three cores increased the power consumption with 2.7 W (or on average 0.9 W/core), and, for double precision, the power increase is 2.1 W, or 0.7 W/core. Though more careful analysis is needed the results indicate that the ARM Cortex-A9 cores may have an energy efficiency of close to 2 GF/J in single precision and about 1 GF/J in double precision.

| Op.         | Precision | Matrix | Perf.  | Power | Eff. | E.Eff. |

|-------------|-----------|--------|--------|-------|------|--------|

|             |           | Size   | [GF/s] | W     | %    | [GF/J] |

| GPU         | SP        | 4096   | 2500   | 245.7 | 71.0 | 10.18  |

|             | DP        | 4096   | 1050   | 247.2 | 89.4 | 4.25   |

| CPU 1-core  | SP        | 2560   | 1.60   | 68.7  | 61.5 | 0.023  |

|             | DP        | 512    | 0.90   | 68.7  | 69.2 | 0.013  |

| CPU 4-cores | SP        | 5120   | 5.16   | 71.4  | 49.6 | 0.072  |

|             | DP        | 4608   | 2.43   | 70.8  | 46.7 | 0.034  |

Table 5 Matrix multiplication performance on the CPU and GPU respectively for the cluster node.

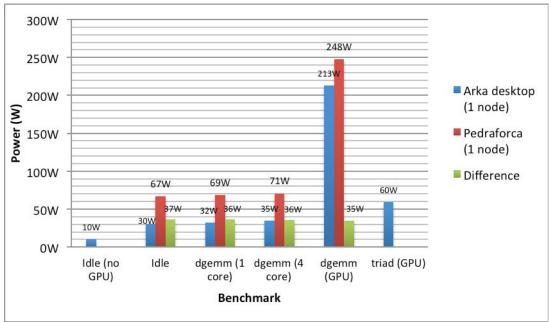

#### Analysis of power consumption

The power measurement results for the BSC-2 cluster are summarised in Figure 7. The blue bars give the power consumption of the single-node Arka desktop unit and the red bars the power consumption of a Pedraforca cluster node. The green bars give the difference between the two. The only differences between the cluster and desktop nodes are the PCIe riser card, the InfiniBand card, and the fans. The total difference was almost constant, at about 36 W, and the largest contribution, at least 25 W, based on the fan's specification and informal measurements at E4 Computer Systems, is certainly from the inefficient fans. Work is ongoing to lower the power consumption and noise level of the fans.

(a) Per-node GPU results.

Figure 6 Per-node dense matrix-matrix multiplication on the BSC-2 prototype.

The power consumption of the Arka desktop node, with CPU and GPU idle, is 30 W. The power consumption of a single idle Pedraforca node, for the reasons discussed above, is 67 W. In both cases, executing DGEMM on a single CPU core increases power consumption by about 2 W, and executing it on all four cores increases power consumption by 4-5 W. In order to determine how much of this is due to the K20 GPU, we removed the GPU from the Arka desktop node, and measured a power consumption of 10 W. Hence, for CPU-only workloads, a power consumption of about 15 W, for all components on the SECO system-on-

module and carrier board, is inflated by 373% to 71 W.

For GPU workloads, the power consumption overheads are less significant. For DGEMM on the GPU, the total power consumption for a Pedraforca node was measured to be 248 W. Of this, the fans, idle CPU and other components outside the GPU account for about 40 W. The overhead of all components except the GPU is therefore low, at about 20%. Finally, we measured the power consumption of the SHOC (Scalable HeterOgeneous Computing) triad benchmark, which is a GPU triad operation, similar to that of STREAM, operating from host memory. This shows the power consumption of the PCIe traffic that was about 350 MB/s.

Figure 7 Power measurement results on the BSC-2 prototype.

#### 2.1.5 Conclusions

Due to delays in the delivery of the Pedraforca prototype and several technical issues it has only been possible to collect results for a subset of the benchmark suite. Work is ongoing on resolving the problems outlined below in order to be able to operate the system using a wider range of full applications.

The most critical outstanding technical problem is that the InfiniBand network is not working. The Mellanox InfiniBand drivers do currently not support RDMA on our system, due to the lack of coherency between the CPUs and PCIe. This limitation was not known until installation time. In order to use InfiniBand, albeit at lower performance, InfiniBand was configured to use IPoIB (IP over InfiniBand). However, the throughput was less than 25 MB/s, i.e. much lower than that of Ethernet (100 MB/s, observed for benchmarks on Pedraforca). As a result, we can only use the Ethernet network, giving a peak network throughput of 1 Gb/s rather than the expected 40 Gb/s, and there is no support for GPUDirect. Currently, Mellanox has provided no timeframe for the resolution of this problem.

A second problem is that the idle power consumption is much higher than expected. Details are given in the results section. The fans, running constantly at full speed, consume about 25 W per node and they generate a lot of noise. Work to fix this problem is ongoing. In addition, the K20 GPU at idle consumes about 20 W per node. For CPU-only workloads, therefore the total per node power consumption is inflated to almost 70 W, although the SECO system on module and carrier board on their own require only about 15 W.

Various other niggles were encountered. When the prototype was first installed, a bug in the Ethernet driver caused the Ethernet network to be unstable, so that nodes sometimes became inaccessible, frustrating development work. This problem was resolved in mid-November 2013, by changing the PCIe Ethernet NIC. In addition, the SLURM job scheduler could not be used because it expects the core count reported by the Linux kernel to include all cores, whereas the kernel excludes cores in power-saving mode. This problem may soon be fixed.

Despite the above problems, certain aspects of the prototype have been a success. Firstly, the system has excellent energy efficiency for matrix multiply: double precision at 4.2 GF/J (1.04 TF/s in 248 W) and single precision at 10.2 GF/J (2.50 TF/s in 246 W), even including the current inefficient fans. If the network problems can be resolved, this result shows that GPU-dominated workloads can potentially achieve very high energy-efficiency.

The Pedraforca prototype also has high impact, beyond the performance of the actual machine. Firstly, the prototype is contributing to the maturity of the software stack for ARM-based HPC systems. Although the Mellanox InfiniBand drivers do not yet support RDMA, InfiniBand on ARM is only under development through the efforts of the Pedraforca cluster. Once the stability problems are resolved and BSC-internal benchmarking is complete, the 72-node cluster will be made available to the partners of the PRACE and Mont-Blanc projects and other researchers who wish to begin porting large-scale CUDA applications to ARM systems.

The second real impact of the Pedraforca prototype is its commercialization by E4 Computer Engineering. The prototype system architecture corresponds exactly to the Arka Extreme platforms, in the company's Arka series of ARM-based platforms. Arka EK002 is the 3U chassis used in Pedraforca, which features NVidia Tegra 3 and K20 GPU and QDR InfiniBand, and is targeted at applications such as seismic processing, signal and image processing, video analytics and traffic analysis. Arka EK001 is a single-node version, without InfiniBand, in a desktop form factor.

12

#### 2.2 GPU-GPU communication over PCIe and IB, CaSToRC

Work on the CaSToRC prototype consisted of two tasks. First the SLURM resource manager was installed to gain experience with scheduling accelerator (GPU) resources. Second the scaling behaviour of the prototype was studied using the HPL benchmark.

Earlier results for this prototype are reported in D9.3.3 [D933 p. 39ff].

### 2.2.1 Experiences with SLURM on scheduling GPUs

The main goal was to set up the SLURM utility as the main scheduler on the eight-node "Prometheus" cluster, a phase-1 PRACE-1IP WP9 prototype. Each node has two GPU accelerators and two CPUs. Details of the cluster are presented in deliverable D9.3.3. For the installation it was necessary to configure PAM (Pluggable Authentication Module) to prevent locked memory limit propagation to the compute nodes, and declaring the generic resources (GRES) to be managed. Within this context, a generic resource is any computation unit that co-operates with the CPU, such as GPUs, accelerators, etc. With SLURM, the user allocates a generic resource by using the "gres" parameter during job submission. However, in the default configuration, GPUs are not pinned to the user, meaning a user can use a GPU of an allocated node, if it exists, whether the option is specified or not. There are two situations in which this may be problematic: 1) in a shared system for which GPU resources are accounted for separately from CPU resources, this setup will not allow reliable accumulation of GPU time used; 2) on systems where multiple jobs are allowed to run on the same node, this setup does not exclude undesirable situations where multiple users will compete on the same GPU. The first attempt to solve this issue was setting the default value for the CUDA ENABLE DEVICES environment variable to a null value and making it read-only for all users. The SLURM controller, which runs with root privileges, would then set this variable according to the user's "gres" requirements. It was found that placing the configuration files under the same directory tree as the SLURM installation solved the issue.

SLURM authentication requires an external mechanism for which MUNGE is recommended by the SLURM developers. With MUNGE, which interfaces to SLURM as a plugin, authentication services can be configured such that, e.g. users are granted access to compute nodes only through the submission of jobs through the head node. Additionally, for accounting purposes a MySQL database was set up for recording and accounting of resource usage. The HPL power efficiency measurements also served as a use case to test the SLURM installation.

#### 2.2.2 Power Measurement Characterisation

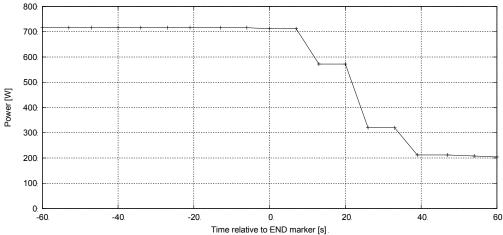

Blade level power measurements were taken using the *rvitals* utility included in the IBM Extreme Cloud Administration Toolkit (xCat). Unfortunately two effects distorts the power measurements: the power readings seem to be averaged over a period of about 40 seconds, comparable to the time of some of the benchmarks, and the system temperature needs about 10 minutes to stabilise causing about a 50 W increase in power consumption, probably due to increased fan speed.

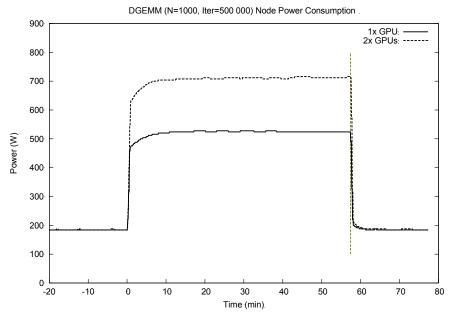

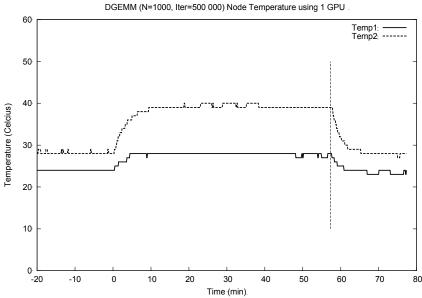

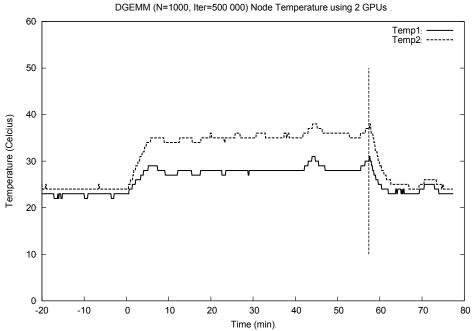

Both effects can be seen when using repeated execution of matrix-matrix multiplication (DGEMM) to simulate a step load change. The short-term averaging can best be seen at the tail end of the benchmark shown in Figure 8. The long-term temperature effects are visible in the power profile over the whole benchmark execution shown in Figure 9, which correlates

well with the temperature measurements shown in Figure 10 and Figure 11.

Figure 8 Power measurements around the end of the 2 GPU matrix-multiply benchmark on the CaSToRC prototype.

Figure 9 Power profile of repeated matrix-matrix multiplication on the CaSToRC prototype.

Figure 10 Temperature profile captured during 1 GPU benchmark run shown in Figure 9.

Figure 11 Temperature profiles captured during 2 GPU benchmark run shown in Figure 9.

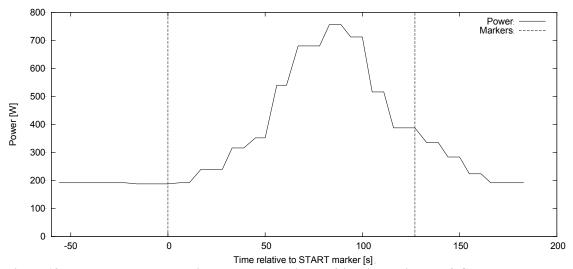

Figure 12 illustrates the averaging effect on the power data gathered during execution of the HPL benchmark. In this example, the reported run time was 127 seconds and the start and end of the benchmark execution is shown in the graph compared to the power values. Clearly visible is the tail of elevated power readings after end of the benchmark. Furthermore, since the NVidia HPL code could not be instrumented the markers include initialization and verification time, which are much less compute intensive. Based on the reported performance of 544.9 GF/s, the actual LU decomposition took only about 51 s. This calculated run-time roughly corresponds to the high power values between 50 and 100 s in Figure 12. Comparing to the timescales in Figure 9, the longest HPL runs took less than 4 minutes. Thus, the energy measurements for HPL are dominated by measurement errors due to the averaging effect.

Figure 12 Power measured during a HPL run using N=34 756 equations on 2 GPUs.

#### 2.2.3 Energy Efficiency Estimation for Matrix Multiplication

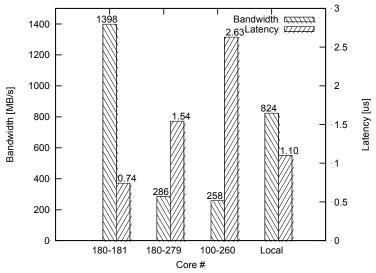

Based on the data gathered from the repeated execution of the matrix-matrix multiplication of two 1000x1000 element matrices, we calculated the energy efficiency for a single node of the cluster. The power values for this calculation were averaged from the steady state, flat-top,

part of Figure 9 using samples, beginning 20 minutes after benchmark start until 10 minutes before benchmark end to eliminate the influence of the averaging. The selected time window contained 246 respective 249 samples with a standard deviation below 1%, better than the estimated accuracy of the power measurement equipment. As a comparison, the leading system equipped with NVidia 2070 accelerators on the November 2013 Green500 list (rank 98, CINECA/SCS) reached 0.892 GF/J, comparable to the two GPU case. The results are shown in Table 6.

| GPUs | Perf.  | Eff. | Avg. Power | Energy Eff. |

|------|--------|------|------------|-------------|

|      | [GF/s] |      | [W]        | [GF/J]      |

| 1    | 290.6  | 0.56 | 525        | 0.55        |

| 2    | 580.4  | 0.56 | 711        | 0.82        |

Table 6 Performance and energy efficiency for matrix-matrix multiplication on the CaSToRC prototype.

#### 2.2.4 HPL Benchmark Performance

The NVidia enhanced HPL benchmark written in C/CUDA that runs on both CPUs and GPUs was executed for different configurations to assess the scalability. As a preliminary step the problem size was varied in order to find the optimal value in regards to performance (N, the local problem size) as well as the block size (NB). Power consumption data were collected using xCat's rvitals utility reading blade-level power data every 5 seconds. Idle power consumption was measured during a 60 second time interval preceding every HPL run.

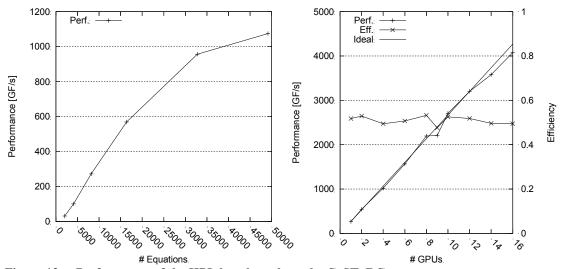

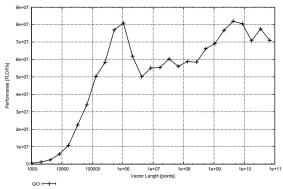

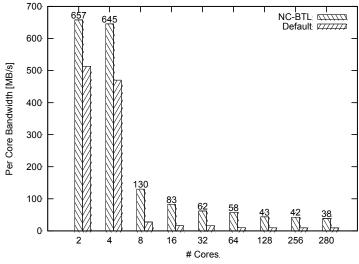

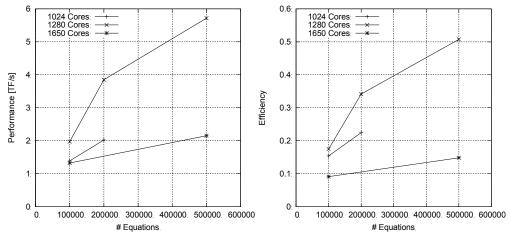

The results are shown in Figure 13. On the left graph the performance of the HPL benchmark running on four GPUs (two nodes) is shown for varying problem sizes. Details, including computational efficiency, are listed in Table 7. The right graph shows the scalability using weak scaling. Details are shown in Table 8. As is typical for this generation of GPUs, efficiency is limited to slightly above 50% due to architecture restrictions. The scaling is almost perfect; the efficiency over all runs varies only by 5%. Interestingly the intuitively optimal square numbers of GPUs cases exhibit slightly worse performance than non-square number of GPUs perhaps due to the fact that two GPUs share a node.

Figure 13 Performance of the HPL benchmark on the CaSToRC prototype.

| <b>GPUs</b> | Size   | Perf. [GF/s] | Efficiency |

|-------------|--------|--------------|------------|

| 4           | 2 048  | 31           | 0.02       |

| 4           | 4 096  | 101          | 0.05       |

| 4           | 8 192  | 272          | 0.13       |

| 4           | 16 384 | 569          | 0.27       |

| 4           | 32 768 | 957          | 0.46       |

| 4           | 49 152 | 1074         | 0.52       |

Table 7 Performance of the HPL benchmark for varying sizes on 4 GPUs (2 nodes).

| GPUs | Size   | Perf. [GF/s] | Efficiency | Speedup |

|------|--------|--------------|------------|---------|

| 1    | 24 576 | 266          | 0.52       | 1.0     |

| 2    | 34 756 | 545          | 0.53       | 2.0     |

| 4    | 49 152 | 1018         | 0.49       | 3.8     |

| 6    | 60 199 | 1566         | 0.51       | 5.9     |

| 8    | 69 511 | 2194         | 0.53       | 8.2     |

| 9    | 73 728 | 2207         | 0.48       | 8.3     |

| 10   | 77 716 | 2707         | 0.53       | 10.1    |

| 12   | 85 134 | 3202         | 0.52       | 12.0    |

| 14   | 91 955 | 3578         | 0.50       | 13.4    |

| 16   | 98 304 | 4077         | 0.49       | 15.3    |

Table 8 Weak scaling performance for the HPL benchmark on the CaSToRC prototype.

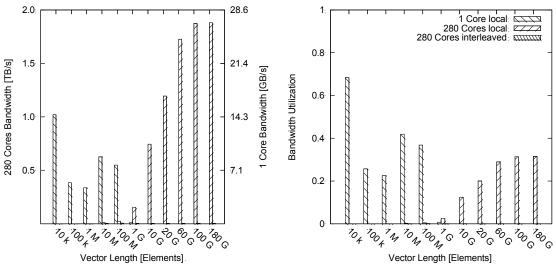

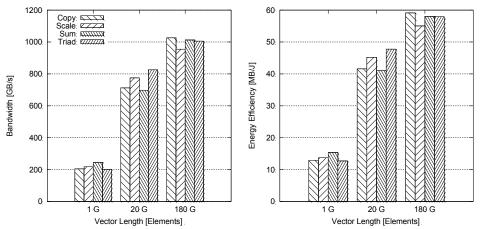

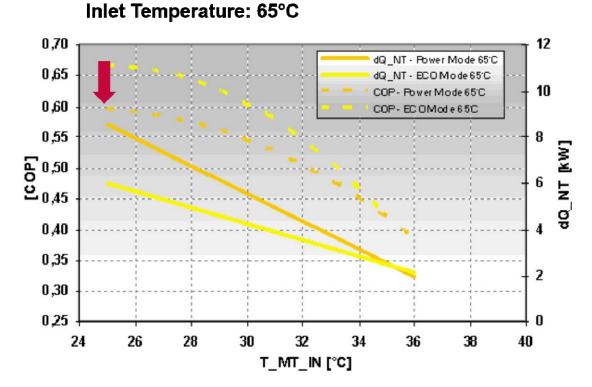

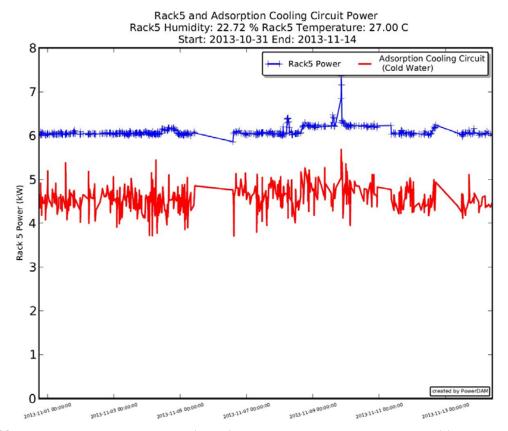

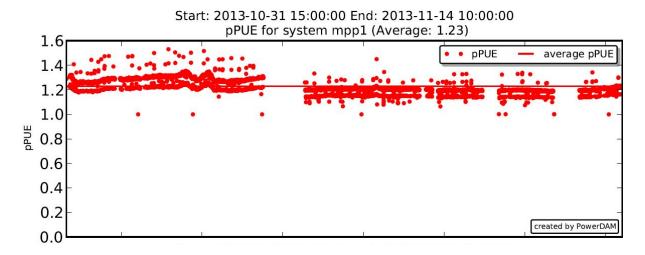

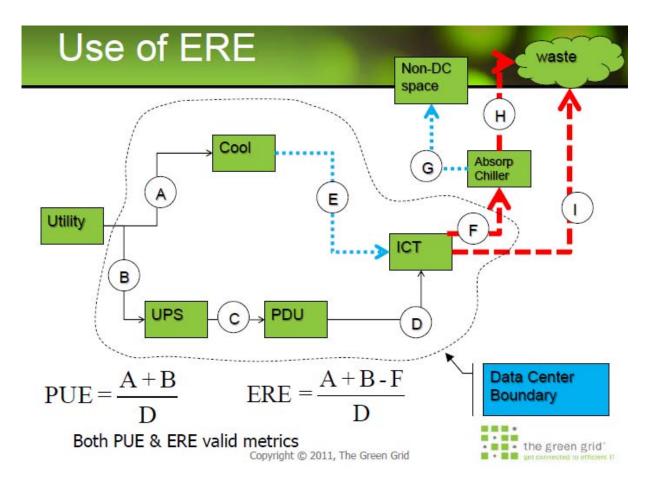

#### 2.2.5 Conclusion