# SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

# INFRA-2010-2.3.1 – First Implementation Phase of the European High Performance Computing (HPC) service PRACE

## **PRACE-1IP**

# **PRACE First Implementation Project**

**Grant Agreement Number: RI-261557**

# D9.2.1 First Report on Multi-Petascale to Exascale Software

## **Final**

Version: 1.1

Author(s): Volker Strumpen, JKU

Iris Christadler, LRZ

Guillaume Colin de Verdiere, CEA

Matthieu Hautreux, CEA

Date: 21.04.2011

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-261557                                                                                                                  |                   |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|--|

|               | Project Title: PRACE First Implementation Project  Project Web Site: <a href="http://www.prace-project.eu">http://www.prace-project.eu</a> |                   |  |  |  |  |  |

|               |                                                                                                                                            |                   |  |  |  |  |  |

|               | Deliverable ID: D9.2.121  Deliverable Nature: <doc_type: other="" report="">  Deliverable Level: Contractual Date of Delivery:</doc_type:> |                   |  |  |  |  |  |

|               |                                                                                                                                            |                   |  |  |  |  |  |

|               |                                                                                                                                            |                   |  |  |  |  |  |

|               | PU / PP / RE / CO *                                                                                                                        | 30 / April / 2011 |  |  |  |  |  |

|               | Actual Date of Delivery:                                                                                                                   |                   |  |  |  |  |  |

|               |                                                                                                                                            | 30 / April / 2011 |  |  |  |  |  |

|               | EC Project Officer: Bernhard Fabianek                                                                                                      |                   |  |  |  |  |  |

<sup>\*</sup> - The dissemination level are indicated as follows: **PU** - Public, **PP** - Restricted to other participants (including the Commission Services), **RE** - Restricted to a group specified by the consortium (including the Commission Services). **CO** - Confidential, only for members of the consortium (including the Commission Services).

## **Document Control Sheet**

|          | Title: First Report on Multi-Petascale to Exascale Software |                      |  |  |  |  |

|----------|-------------------------------------------------------------|----------------------|--|--|--|--|

| Document | ID: <d9.2.1></d9.2.1>                                       |                      |  |  |  |  |

|          | Version: <1.1 > Status: Final                               |                      |  |  |  |  |

|          | Available at: http://www.prace-project.eu                   |                      |  |  |  |  |

|          | Software Tool: Microsoft Word 2007                          |                      |  |  |  |  |

|          | <b>File(s):</b> D9.2.1.docx                                 |                      |  |  |  |  |

|          | Written by:                                                 | Volker Strumpen, JKU |  |  |  |  |

| Authorship | Contributors: | Computer Systems:                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |               | Riccardo Brunino (CINECA), Carlo Cavazzoni (CINECA), Willy Homberg (FZJ), Herbert Huber (LRZ), Radek Januszewski (PSNC), Jochen Kreutz (FZJ), Jacques-Charles Lafoucriere (CEA), , Stephan Michael (FZJ), Stefan Riha (JKU), Alam Sadaf Roohi (CSCS), Ramnath Sai Sagar (BSC), Michael Schliephake (KTH)                                                                                                                                                                      |

|            |               | Programming Languages:                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|            |               | Ricardo Brunino (CINECA), Iris Christadler (LRZ), Tiziano Diamanti (CINECA), Okan Dogru (UYBHM), Federico Ficarelli (CINECA), Ivan Girotto (ICHEC), Jose Gracia (HLRS), Giannis Koutsou (CaSTORC), Agnieszka Kwiecien (PSNC/WCNS), Pierre-François Lavallée (IDRIS), Ioannis Liabotis (GRNET), Murat Manguoglu (UYBHM), Martin Polak (JKU), Mariusz Uchronski (PSNC/WCNS), Alam Sadaf Roohi (CSCS), Ramnath Sai Sagar (BSC), Philippe Wautelet (IDRIS), Volker Weinberg (LRZ) |

|            |               | System Software:                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |               | Axel Auweter (LRZ), Daniela Galetti (CINECA), Matthieu Hautreux (CEA), Herbert Huber (LRZ), Can Ozturan (UYBHM), Alam Sadaf Roohi (CSCS), Andrea Vanni (CINECA)                                                                                                                                                                                                                                                                                                               |

|            | Reviewed by:  | Tim Robinson (CSCS), Dietmar Erwin (JSC)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | Approved by:  | MB/TB                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **Document Status Sheet**

| Version | Date          | Status        | Comments |

|---------|---------------|---------------|----------|

| 1.0     | 11/April/2011 | Draft version |          |

| 1.1     | 21/April/2011 | Final version |          |

# **Document Keywords**

| Keywords: | PRACE, HPC, Research Infrastructure |

|-----------|-------------------------------------|

|           |                                     |

|           |                                     |

## **Copyright notices**

© 2011 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-261557 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

# **Table of Contents**

| Pr  | oject a | and Deliverable Information Sheet                | i   |

|-----|---------|--------------------------------------------------|-----|

| Do  | cume    | ent Control Sheet                                | i   |

| Do  | cume    | ent Status Sheet                                 | ii  |

| Do  | cume    | ent Keywords                                     | iii |

| Ta  | ble of  | Contents                                         | iv  |

| Lis | t of F  | igures                                           | vi  |

|     |         | ables                                            |     |

| Re  | feren   | ces and Applicable Documents                     | ix  |

|     |         | Acronyms and Abbreviations                       |     |

|     |         | ve Summary                                       |     |

| 1   |         | roduction                                        |     |

| 2   |         | mputer Architectures                             |     |

| 2   | 2.1     | Hardware Implications on Software for Exascale   |     |

|     | 2.1     | Promising Hardware Technologies for Exascale HPC |     |

|     | 2.2     | 2.2.1 Intel SandyBridge                          |     |

|     |         | 2.2.2 IBM Power 7                                |     |

|     |         | 2.2.3 IBM BG/Q                                   |     |

|     |         | 2.2.4 AMD Fusion                                 |     |

|     |         | 2.2.5 NVIDIA Tegra                               |     |

|     |         | 2.2.6 NVIDIA Tesla                               |     |

|     |         | 2.2.7 INTEL MIC                                  |     |

|     |         | 2.2.8 FPGA                                       |     |

|     |         | 2.2.9 DSP: Texas Instruments C6000 Multicore     |     |

|     |         | 2.2.10 Tilera TilePro64                          |     |

|     | 2.3     | Analysis of the Hardware Survey                  |     |

|     |         | 2.3.1 Scalability                                |     |

|     |         | 2.3.2 Performance                                |     |

|     |         | 2.3.3 Productivity                               | 21  |

|     |         | 2.3.4 Sustainability                             | 22  |

|     |         | 2.3.5 Portability                                | 22  |

|     |         | 2.3.6 Availability                               |     |

|     |         | 2.3.7 Resilience                                 |     |

|     | 2.4     | Trends to Watch in the Coming Year               | 24  |

| 3   | Pro     | gramming Languages                               | 26  |

|     | 3.1     | Description & Results for Each Language          | 26  |

|     |         | 3.1.1 <i>CUDA</i>                                | 26  |

|     |         | 3.1.2 <i>CUDA+MPI</i>                            |     |

|     |         | 3.1.3 OpenCL                                     | 32  |

|   |     | 3.1.4 <i>Hy</i> | brid Multicore Parallel Programming workbench (HMPP)        |    |

|---|-----|-----------------|-------------------------------------------------------------|----|

|   |     | 3.1.5 Po        | ortland Group (PGI) Fortran and C compiler for accelerators | 37 |

|   |     | 3.1.6 <i>Op</i> | penMP+MPI                                                   | 38 |

|   |     | 3.1.7 Co        | parray Fortran (CAF)                                        | 40 |

|   |     | 3.1.8 <i>Un</i> | nified Parallel C (UPC)                                     | 42 |

|   |     | 3.1.9 <i>Ch</i> | apel                                                        | 44 |

|   |     | 3.1.10          | StarSuperscalar (StarSs) Programming Model                  | 46 |

|   |     | 3.1.11          | Cilk                                                        | 47 |

|   |     | 3.1.12          | Intel Array Building Blocks (ArBB)                          | 50 |

|   |     | 3.1.13          | Intel Threading Building Blocks (TBB)                       | 52 |

|   |     | 3.1.14          | Hierarchically Tiled Array (HTA)                            | 54 |

|   | 3.2 | Summa           | ry of new Programming Languages and Paradigms               | 56 |

|   |     | 3.2.1 Bri       | ief Overview and Classification                             | 56 |

|   |     | 3.2.2 Av        | vailability and Sustainability                              | 58 |

| 4 | Sys | tem Soft        | ware                                                        | 60 |

|   | 4.1 | Operati         | ng System                                                   | 60 |

|   |     | 4.1.1 Su        | rvey                                                        | 60 |

|   |     | 4.1.2 <i>An</i> | alysis                                                      | 61 |

|   |     | 4.1.3 <i>Co</i> | onclusions                                                  | 61 |

|   | 4.2 | System          | Management                                                  | 62 |

|   |     | 4.2.1 Su        | rvey                                                        | 62 |

|   |     | 4.2.2 <i>An</i> | alysis                                                      | 64 |

|   |     | 4.2.3 <i>Co</i> | onclusions                                                  | 65 |

|   | 4.3 | Data Ma         | anagement                                                   | 65 |

|   |     | 4.3.1 Su        | rvey                                                        | 65 |

|   |     | 4.3.2 <i>An</i> | alysis                                                      | 66 |

|   |     | 4.3.3 <i>Co</i> | onclusions                                                  | 67 |

|   | 4.4 | MPI and         | d Communication Libraries                                   | 67 |

|   |     | 4.4.1 Su        | rvey                                                        | 67 |

|   |     | 4.4.2 An        | alysis                                                      | 68 |

|   |     | 4.4.3 <i>Co</i> | onclusions                                                  | 69 |

|   | 4.5 | Resourc         | ce Management                                               | 69 |

|   |     | 4.5.1 Su        | rvey                                                        | 69 |

|   |     | 4.5.2 An        | alysis                                                      |    |

|   |     | 4.5.3 Co        | onclusions                                                  | 73 |

# **List of Figures**

| Figure 1                 | Simple CUDA kernel                                                                                                                                                                                                   |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2                 | CUDA host code                                                                                                                                                                                                       |

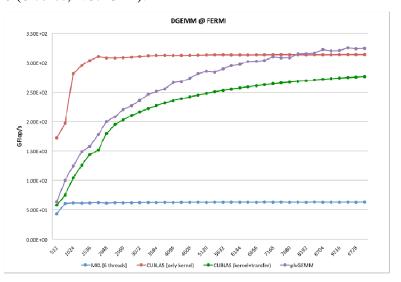

| Figure 3                 | Comparison between CUBLAS, MKL and phiGEMM (DGEMM)                                                                                                                                                                   |

| Figure 4 used)           | Comparison between CUBLAS, MKL and phiGEMM (DGEMM, PINNED memory 28                                                                                                                                                  |

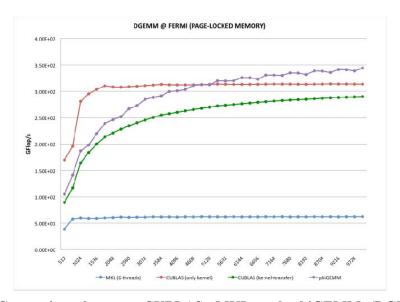

| Figure 5                 | Weak scaling plot of Quda BiCGstab inverter performance                                                                                                                                                              |

| Figure 6                 | Strong scaling plot of Quda BiCGstab inverter performance                                                                                                                                                            |

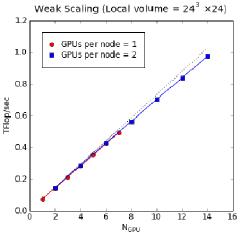

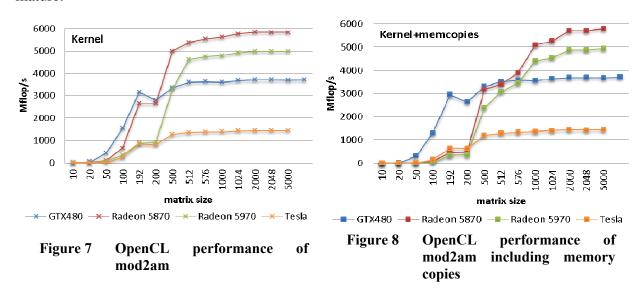

| Figure 7                 | OpenCL performance of mod2am                                                                                                                                                                                         |

| Figure 8                 | OpenCL performance of mod2am including memory copies                                                                                                                                                                 |

| Figure 9                 | HMPP callsite example                                                                                                                                                                                                |

| Figure 10                | HMPP codelet example                                                                                                                                                                                                 |

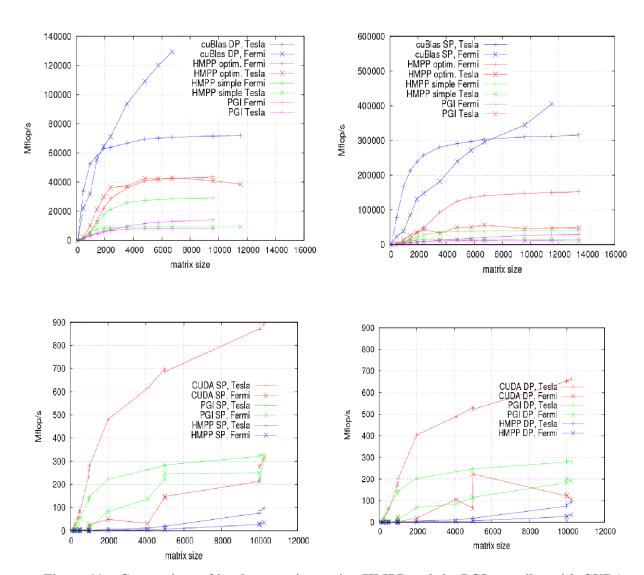

|                          | Comparison of implementations using HMPP and the PGI compiler with CUDA versions. row shows the performance for mod2am, the lower row the performance for mod2as, both left) and double precision (right)            |

| Figure 12                | PGI C code example                                                                                                                                                                                                   |

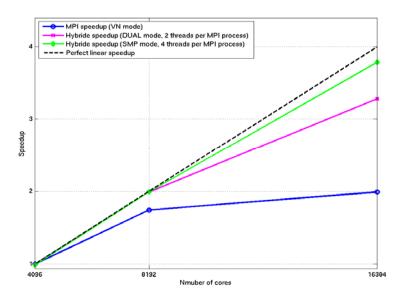

| Figure 13                | OpenMP+MPI speedup of HYDRO on BG/P                                                                                                                                                                                  |

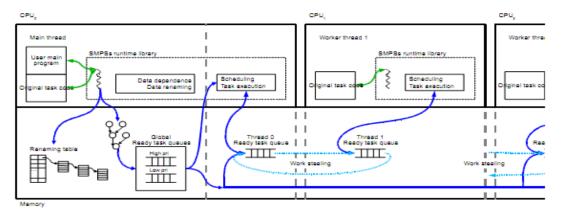

| Figure 14                | SMPSs Implementation                                                                                                                                                                                                 |

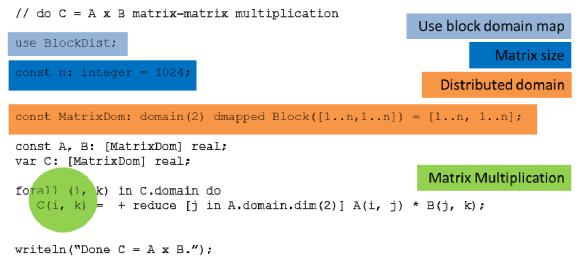

| Figure 15                | StarSs blocked main routine with function call                                                                                                                                                                       |

| Figure 16                | StarSs function with pragma                                                                                                                                                                                          |

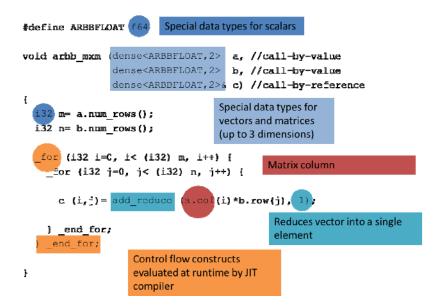

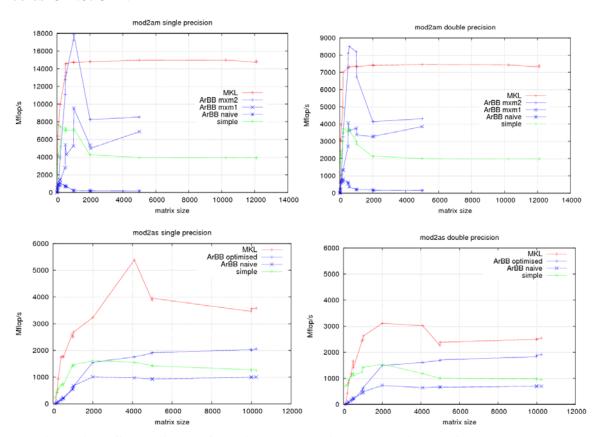

| * *                      | Comparison of various ArBB implementations with MKL and a naïve implementation. row shows the performance for mod2am/MxM, the lower row the performance for MV, both for single (left) and double (right) precision. |

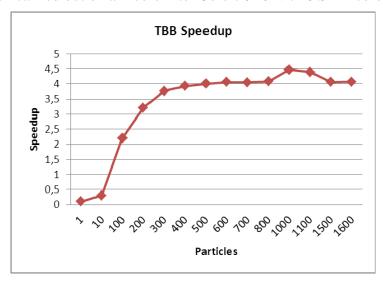

| Figure 18                | TBB speedup of molecular dynamics code                                                                                                                                                                               |

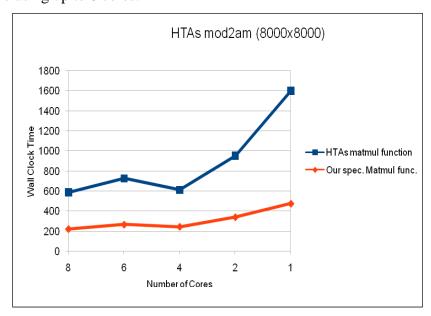

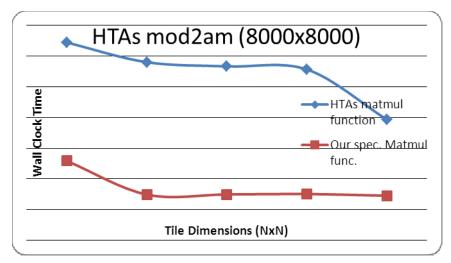

| Figure 19<br>built-in ma | Wall clock time (in seconds) as the number of cores increase for our implementation and trix-matrix multiplication routine. Tile size is the same for both implementation and fixed. 55                              |

| Figure 20                | Wall clock time (in seconds) as we increase tile size for our implementation and build-in                                                                                                                            |

# **List of Tables**

| Table I  | Contributing PRACE sites                                                          | 4      |

|----------|-----------------------------------------------------------------------------------|--------|

| Table 2  | INTEL Sandy Bridge pros and cons                                                  | 6      |

| Table 3  | IBM Power 7 pros and cons                                                         | 8      |

| Table 4  | IBM BG/Q pros and cons                                                            | 8      |

| Table 5  | AMD Fusion pros and cons                                                          | 10     |

| Table 6  | NVIDIA Tegra pros and cons                                                        | 12     |

| Table 7  | NVIDIA Tesla series GPUs pros and cons                                            | 14     |

| Table 8  | INTEL MIC pros and cons                                                           | 15     |

| Table 9  | FPGA pros and cons                                                                | 16     |

| Table 10 | TI C6000 pros and cons                                                            | 18     |

| Table 11 | Tilera TilePro64 pros and cons                                                    | 19     |

| Table 12 | CUDA pros and cons                                                                | 29     |

| Table 13 | CUDA+MPI pros and cons                                                            | 31     |

| Table 14 | OpenCL pros and cons                                                              | 34     |

| Table 15 | HMPP pros and cons                                                                | 37     |

| Table 16 | PGI compiler pros and cons                                                        | 38     |

| Table 17 | OpenMP+MPI pros and cons                                                          | 39     |

| Table 18 | CAF performance of mod2am/MxM in MFlop/s for 400 x 400 matrices                   | 41     |

| Table 19 | CAF performance of mod2f/FFT in MFlop/s (bits=16 and length=65536)                | 41     |

| Table 20 | CAF pros and cons                                                                 | 42     |

| Table 21 | UPC performance of mod2am/MxM in MFlop/s for 800 x 800 matrices                   | 43     |

| Table 22 | UPC performance of mod2as/SpMV in MFlop/s for 10000 x 10000 matrices (3.5% fi     | l1) 43 |

| Table 23 | UPC performance of mod2f/FFT in MFlop/s (bits=16 and length=65536)                | 43     |

| Table 24 | UPC pros and cons                                                                 | 44     |

| Table 25 | Chapel pros and cons                                                              | 46     |

| Table 26 | StarSs pros and cons                                                              | 47     |

| Table 27 | MIT Cilk results on an SGI Altix 4700, using 256 Itanium2 cores @1.6GHz           | 49     |

| Table 28 | Intel CilkPlus results on an Altix ICE 8200 node, using 8 Nehalem-EP cores @2.8Gh | z. 49  |

| Table 29 | Cilk pros and cons                                                                | 50     |

| Table 30 | ArBB pros and cons                                                                | 52     |

| Table 31 | TBB pros and cons                                                                 | 54     |

| Table 32 | HTA pros and cons                                                                 | 56     |

| Table 33 | Parallel programming languages and environments                                   | 57     |

| Table 34 | Language classification by method for expression parallelism.                     | 58     |

| Table 35 | Availability and indicators for sustainability of programming languages           | 59     |

| Table 36 | Operating systems used at PRACE sites                                             | 61     |

| Table 37 | System management software used at PRACE sites, Part I                            | 63     |

|          |                                                                                   |        |

## Multi-Petascale to Exascale Software

| Table 38 | System management software used at PRACE sites, Part II | 64 |

|----------|---------------------------------------------------------|----|

| Table 39 | Data management systems used at PRACE sites             | 66 |

D9.2.1

Table 40 Table 41

# **References and Applicable Documents**

- [1] P. Andrews, P. Kovatch, V. Hazlewood, T.Baer, *Scheduling a 100,000 Core Supercomputer for Maximum Utilization and Capability*, 39th International Conference on Parallel Processing Workshops (ICPPW), 2010.

- [2] Berkley UPC project <a href="http://upc.lbl.gov">http://upc.lbl.gov</a>.

- [3] F. Cappello, Resilience: *One of the main challenges for Exascale Computing*, EESI 2010.

- [4] M. Clark, R. Babich and B.Joo, *Parallelizing the QUDA Library for Multi-GPU Calculations in Lattice Quantum Chromodynamics*, arXiv:1011.0024[hep-lat].

- [5] M. Clark, R. Babich, K. Barros, R. Brower, and C. Rebbi, *Solving Lattice QCD systems of equations using mixed precision solvers on GPUs*, Comp. Phys. Comm. 181, 1517 (2010).

- [6] Co-Array Fortran, <a href="http://www.co-array.org/">http://www.co-array.org/</a>

- [7] Condor High Throughput Computing, http://www.cs.wisc.edu/condor/

- [8] Cray Compiler Environment for CAF and UPC (details available at: <a href="http://docs.cray.com/">http://docs.cray.com/</a>).

- [9] CUDA zone, http://www.NVIDIA.com/object/cuda\_home\_new.html

- [10] Jack Dongarra et al., *International Exascale Software Project Roadmap*, work in progress, www.exascale.org/iesp

- [11] M. Fatica, Accelerating LINPACK with CUDA on heterogeneous clusters. GPGPU-2: Proceedings of 2nd Workshop on General Purpose Processing on Graphics Processing Units (New York, NY, USA), ACM, 2009, pp. 46–51.

- [12] Faq on Fault-tolerance for parallel MPI jobs, <a href="http://www.open-mpi.org/faq/?category=ft">http://www.open-mpi.org/faq/?category=ft</a>

- [13] Y. Georgiou, *Resource and Job Management in High Performance Computing*, PhD Thesis, Joseph Fourier University, France, 2010.

- [14] GASNet communication system <a href="http://gasnet.cs.berkeley.edu/">http://gasnet.cs.berkeley.edu/</a>

- [15] General-Purpose Computation on Graphics Hardware, http://gpgpu.org/

- [16] NVIDIA, *High Performance Computing Supercomputing with Tesla GPUs*, http://www.NVIDIA.com/object/tesla computing solutions.html

- [17] http://computing.ornl.gov/HMC/documents/HMC\_AppsBreakout\_day2.pdf

- [18] http://polaris.cs.uiuc.edu/hta/

- [19] <a href="http://software.intel.com/en-us/articles/intel-cilk-plus">http://software.intel.com/en-us/articles/intel-cilk-plus</a>

- [20] http://www.anandtech.com/show/4023/the-brazos-performance-preview-amd-e350-benchmarked

- [21] http://www.conveycomputer.com/, Convey Computer

- [22] http://www.heise.de/newsticker/meldung/SC-2010-IBM-zeigt-BlueGene-Q-mit-17-Kernen-1138226.html

- [23] http://www.hpcwire.com/features/Argonne-Orders-10-Petaflop-Blue-GeneQ-Super-115593779.html

- [24] http://www.hpcwire.com/features/Lawrence-Livermore-Prepares-for-20-Petaflop-Blue-GeneQ-38948594.html

ix

- [25] http://www.intel.com/technology/architecture-silicon/index.htm

- [26] http://www.khronos.org/registry/cl/

- [27] http://www.maxeler.com/, Maxeler Technologies

- [28] http://www.prace-project.eu

- [29] <a href="http://www-03.ibm.com/systems/deepcomputing/solutions/bluegene/index.html">http://www-03.ibm.com/systems/deepcomputing/solutions/bluegene/index.html</a>

- [30] IBM OpenCL Development Kit for Linux on Power and IBM XL C for OpenCL compiler (OpenCL 1.0) <a href="http://www.alphaworks.ibm.com/tech/opencl">http://www.alphaworks.ibm.com/tech/opencl</a>

- [31] Intel Parallel Studio XE CAF (details available at: http://software.intel.com).

- [32] Java Bindings to OpenCL (JOCL, enables applications running on the JVM to use OpenCL 1.1), http://jogamp.org/jocl/www/

- [33] Ian Kuon, Jonathan Rose: *Measuring the Gap Between FPGAs and ASICs*, http://www.eecg.toronto.edu/~ikuon/pubs/fpga2006\_kuon.pdf.

- [34] Peter Kogge at el., ExaScale Computing Study: Technology Challenges in Achieving Exascale Systems, 2008, <a href="http://www.er.doe.gov/ascr/Research/CS/DARPA">http://www.er.doe.gov/ascr/Research/CS/DARPA</a> exascale hardware (2008).pdf

- [35] K. Kandalla, H. Subramoni, A. Vishnu, D.K. Panda, *Designing Topology-Aware Collective Communication Algorithms for Large-Scale Infiniband Clusters: Case Studies with Scatter and Gather*, IPDPS, 2010.

- [36] Charles E. Leiserson, *The Cilk++ concurrency platform*, in proceedings DAC'09, p.522.

- [37] Olav Lindtjørn, Robert G. Clapp, Oliver Pell, Oskar Mencer, Michael J Flynn *Surviving the End of Scaling of Traditional Micro Processors in HPC*. http://www.hotchips.org/uploads/archive22/HC22.23.120-1-Lindtjorn-End-Scaling.pdf

- [38] LoadLeveler Scheduler, IBM, http://www-03.ibm.com/systems/software/loadleveler/

- [39] Lustre Scalability, Sun Microsystems, 2009, www.nccs.gov/wp-content/uploads/2009/03/lustrescalabilitywp\_updated.pdf

- [40] Netlib web-page; <a href="http://www.netlib.org/">http://www.netlib.org/</a>

- [41] NVIDIA CUDA C Programming Guide Version 3.2. 11 September 2010, <a href="http://developer.download.NVIDIA.com/compute/cuda/3\_2\_prod/toolkit/docs/CUDA\_C\_Programming\_Guide.pdf">http://developer.download.NVIDIA.com/compute/cuda/3\_2\_prod/toolkit/docs/CUDA\_C\_Programming\_Guide.pdf</a>

- [42] NVIDIA CUDA ZONE; http://NVIDIA.com/cuda

- [43] Oar Resource Manager, http://oar.imag.fr/

- [44] OpenCL The open standard for parallel programming of heterogeneous systems, http://www.khronos.org/opencl/

- [45] Oracle Grid Engine, http://www.oracle.com/us/products/tools/oracle-grid-engine-075549.html

- [46] PBS Professional, PBS Works, http://www.pbsworks.com/

- [47] Platform LSF, Platform Computing, http://www.platform.com/

- [48] PRACE Deliverable D6.6, Report on petascale software libraries and programming models, http://www.prace-project.eu/documents/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/public-deliverables-1/pu

- [49] PRACE Workshop on *New Languages & Future Technology Prototypes* (March 1-2, 2010), http://www.prace-project.eu/documents/prace\_workshop\_on\_new\_languages\_and\_future\_technology\_prototypes.pdf

- [50] PyOpenCL (access to the OpenCL API from Python, supports OpenCL 1.1), http://mathema.tician.de/software/pyopencl

- [51] I. Raicu, Z. Zhang, M. Wilde, I. Foster, P. Beckman, K. Iskra, B. Clifford, *Toward Loosely Coupled Programming on Petascale Systems*, IEEE/ACM Supercomputing 2008.

- [52] Redefining what it's possible. Scientific Computing. January 7, 2001. <a href="http://www.scientificcomputing.com/articles-HPC-GPGPU-Redefining-What-is-Possible-010711.aspx">http://www.scientificcomputing.com/articles-HPC-GPGPU-Redefining-What-is-Possible-010711.aspx</a>

- [53] Rice University CAF 2.0 <a href="http://caf.rice.edu/">http://caf.rice.edu/</a>

- [54] G.M. Shipman, S. Poole, P. Shamis, I. Rabinovitz, *X-SRQ Improving Scalability and Performance of Multi-Core Infiniband Clusters*, Euro PVM/MPI, 2008.

- [55] G.M. Shipman, T.S. Woodall, R.L. Graham, A.B. Maccabe, and P.G. Bridges, *InfiniBand Scalability in Open MPI*, IPDPS, 2006.

- [56] SAMSUNG OpenCL Framework, http://opencl.snu.ac.kr/

- [57] *SLURM*: A Highly Scalable Resource Manager, https://computing.llnl.gov/linux/slurm/slurm.html

- [58] D. Tsafrir, Y. Etsion, D. G. Feitelson, and S. Kirkpatrick, *System Noise, OS Clock Ticks, and Fine-grained Parallel Applications*, ICS, 2005.

- [59] Texas Instruments: TMS320C6678 MulticoreFixed and Floating-Point Digital Signal Processor. Literature Number SPRS691, November 2010.

- [60] Texas Instruments: TI's new C66x Fixed- and Floating-Point DSP Core Conquers the 'Need for Speed'. White paper by Arnon Friedman. Literature Number SPRY147, November 2010.

- [61] Texas Instruments: *TMS320C6672/74/78 High-performance multicore fixed- and floating-point DSPs* Product Bulletin. Literature Number SPRT577a, Februar 2011.

- [62] TORQUE, MOAB, MAUI, Adaptive Computing, http://www.adaptivecomputing.com/resources/docs/

- [63] Unified Parallel C (UPC) <a href="http://upc.gwu.edu/">http://upc.gwu.edu/</a>

- [64] ViennaCL (Linear Algebra and Iterative Solvers) with support for NVIDIA and AMD/ATI GPUs, <a href="http://viennacl.sourceforge.net/">http://viennacl.sourceforge.net/</a>

**BLAS**

# **List of Acronyms and Abbreviations**

AMD Advanced Micro Devices

API Application Programming Interface

APU Accelerated Processing Unit

ArBB Array Building Blocks (Intel)

ARM Advanced RISC Machines

ASIC Application-Specific Integrated Circuit

ATI Array Technologies Incorporated (AMD)

BSC Barcelona Supercomputing Center (Spain)

Basic Linear Algebra Subprograms

CaSToRC Computation-based Science and Technology Research Center (of the

Cyprus Institute)

CAF Co-Array Fortran

CCE Cray Compiler Environment

CCNUMA Cache Coherent NUMA

CEA Commissariat à l'Energie Atomique (represented in PRACE by GENCI,

France)

CILK Multithreaded Programming Language

CINECA Consorzio Interuniversitario, the largest Italian computing centre (Italy)

Chapel Cascade High-Productivity Language (Cray)

CLE Cray Linux Environment

CPU Central Processing Unit

CSC Finnish IT Centre for Science (Finland)

CSCS The Swiss National Supercomputing Centre (represented in PRACE by

ETHZ, Switzerland)

COTS Commercial Off-The-Shelf

CUDA Compute Unified Device Architecture (NVIDIA)

CUBLAS CUDA BLAS Library

DARPA Defense Advanced Research Projects Agency

DDN DataDirect Networks

DDR Double Data Rate

DGEMM Double precision General Matrix Multiply

DMA Direct Memory Access

DNA DeoxyriboNucleic Acid

DP Double Precision, usually 64-bit floating point numbers

DVFS Dynamic Voltage and Frequency Scaling

EC European Commission

ECC Error-Correcting Code

EESI European Exascale Software Initiative

EP Efficient Performance, e.g., Nehalem-EP (Intel)

EPCC Edinburg Parallel Computing Centre (represented in PRACE by

EPSRC, United Kingdom)

EX Expandable, e.g., Nehalem-EX (Intel)

Flop/s Floating point operations per second

FFT Fast Fourier Transform

FP Floating-Point

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FZJ Forschungszentrum Jülich (Germany)

GASNet Global Address Space Networking

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte

Gb/s Giga (= 10<sup>9</sup>) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GDDR Graphic Double Data Rate memory

GENCI Grand Equipment National de Calcul Intensif (France)

GFlop/s Giga (=  $10^9$ ) Floating point operations (usually in 64-bit) per second GHz Giga (=  $10^9$ ) Hertz, frequency =  $10^9$  periods or clock cycles per second

GNU GNU's not Unix, a free OS

GPGPU General Purpose GPU

GPU Graphic Processing Unit

GRNET Greek Research and Technology Network

HE High Efficiency

HLRS High Performance Computing Center (Stuttgart)

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hewlett-Packard

HPC High Performance Computing; Computing at a high performance level

at any given time; often used synonym with Supercomputing

HPL High Performance LINPACK

HT HyperTransport channel (AMD)

HTA Hierarchically Tiled Array programming environment

IB InfiniBand

IBM International Business Machines

ICE (SGI)

ICHEC Irish Center for High-End Computing

IDRIS Institut du Développement et des Ressources en Informatique

Scientifique (represented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IL Intermediate Language

IMB Intel MPI Benchmark

I/O Input/Output

IOR Interleaved Or Random

IPB Interprocessor Bus

IPMI Intelligent Platform Management Interface

ISA Instruction Set Architecture

ISC International Supercomputing Conference; European equivalent to the

US based SC0x conference. Held annually in Germany.

JKU Johannes Kepler University (Austria)

JSC Jülich Supercomputing Centre (FZJ, Germany)

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC,

Sweden)

LINPACK Software library for Linear Algebra

LLNL Laurence Livermore National Laboratory, Livermore, California (USA)

LRZ Leibniz Supercomputing Centre (Garching, Germany)

MFlop/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit) per second

MKL Math Kernel Library (Intel)

MPI Message Passing Interface

MTBF Mean Time Between Failures

MxM Double-Precision matrix-by-matrix multiplication mod2am of the

EuroBen kernels

NoC Network-on-a-Chip

NFS Network File System

NIC Network Interface Controller

NUMA Non-Uniform Memory Access or Architecture

OpenCL Open Computing Language

OpenGL Open Graphic Library

OpenMP Open Multi-Processing

OMPSs Programming model based on OpenMP and StarSs developed at BSC

OS Operating System

PCIe Peripheral Component Interconnect express, also PCI-Express

PGAS Partitioned Global Address Space

PGI Portland Group, Inc.

POSIX Portable OS Interface for Unix

PRACE Partnership for Advanced Computing in Europe; Project Acronym

PSNC Poznan Supercomputing and Networking Centre (Poland)

RDMA Remote Data Memory Access

RVDS RealView Development Suite (ARM)

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SDK Software Development Kit

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SIMD Single Instruction Multiple Data

SMP Symmetric Multi-Processor

SMT Simultaneous Multi-Threading

SNIC Swedish National Infrastructure for Computing (Sweden)

SoC System on a Chip

SP Single Precision, usually 32-bit floating point numbers

SSD Solid State Disk or Drive

StarSs Programming Model for Multicores developed at BSC

STFC Science and Technology Facilities Council (represented in PRACE by

EPSRC, United Kingdom)

TB Tera (= 240 ~ 1012) Bytes (= 8 bits), also TByte

TBB Thread Building Blocks (Intel)

TDP Thermal Design Power

TFlop/s Tera (= 10<sup>12</sup>) Floating-point operations (usually in 64-bit) per second

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the Tier-0 systems; national or topical HPC centres would constitute Tier-1

ULP Ultra Low Power

UPC Unified Parallel C

UV Ultra Violet (SGI)

UYBHM National Center for High Performance Computing of Turkey

VHDL VHSIC (Very-High Speed Integrated Circuit) Hardware Description

Language

# **Executive Summary**

This report investigates the transition of applications from multi-petascale to exascale performance. Since the recent end of frequency scaling, we observe a rapid evolution of power-efficient computer architectures. Thus, we believe that an investigation of future software systems requires an understanding of future hardware architectures. To that end we have surveyed and evaluated the state-of-the-art in high-performance computer systems, parallel programming languages, and system software and tools. Our goal is to identify trends and developments that have the potential to shape the era of exascale supercomputing.

We summarize our findings separately by topic: computer systems, parallel programming languages and system software and tools.

#### **Computer Systems**

We have surveyed state-of-the-art computer systems to assess the implications on future exascale software systems. Due to the accelerated evolution of power-efficient high-performance computers, industry presents us with a multi-faceted variety of designs. We considered mature systems as well as prototypes, ranging from hybrid architectures to IBM's BG/Q supercomputer.

High-performance computer architecture has bifurcated into (1) clusters of multicore chips, driven by the mainstream computer market, and (2) accelerated hybrid systems that combine different architectures such as CPUs and GPUs on the board or chip level. At this point in time, it is unclear whether these two directions will reconverge or coexist in future exascale systems. For the programmer, both directions impose a common serious challenge, the lack of programming language support. As a result, programmers have adopted pragmatic hybrid programming techniques, trying to understand and learn how to use these architectures efficiently. On clusters of multicores, the most prevalent programming paradigm is a combination of MPI and OpenMP, and for GPU-accelerated systems programmers combine MPI with Cuda. Consequently, programmer productivity remains a primary concern, in particular for exascale systems.

Our differentiated technology assessment yields the following conclusions. Microprocessor vendors rely on another decade of Moore's law to scale the number of cores per chip, which we expect to exacerbate the efficiency problems caused by the memory wall. Accelerator architectures have the potential to out-perform traditional CPU-based multicore architectures, but the current generation of accelerators fails to deliver a significant advantage in terms of floating-point performance. Furthermore, today's accelerators do not offer the productivity, portability, availability, and resilience of traditional multicore-based systems.

In summary, we are experiencing an era of rapid evolution towards power-efficient high-performance computer systems. Although the outcome is difficult to predict (we're relying on the 1IP-WP9 prototypes to gain deeper insights), current trends are likely to magnify the need for better parallel programming models.

## **Parallel Programming Languages**

We have evaluated a dozen parallel programming languages for (1) traditional parallel systems based on CPUs with shared-memory and distributed-memory architectures, (2) single and multiple GPUs, and (3) accelerated nodes consisting of both CPU and GPU.

Current de-facto standard for programming traditional clusters of multicores is a pragmatic combination of MPI and OpenMP, and, in addition, Cuda is the de-facto standard for programming NVIDIA GPUs. This mixed programming environment delivers the desired performance up to multi-petaflops.

Most of the evaluated parallel programming languages, including PGAS languages, CAF and UPC, ArBB, Cilk, StarSS, OpenCL, or HMPP, are considered potential candidates for programming exascale applications. At this point in time, we propose to focus on one or very small subset of languages to (1) prepare these languages for exascale computing and (2) offer a clear perspective to application programmers about the languages that are likely to be supported in the future. We have established a framework for the selection process based on benchmarks and a set of evaluation criteria, incl. Performance, productivity, correctness, and sustainability.

#### **System Software and Tools**

We have surveyed the system software and tools used to administrate and operate the supercomputers of the PRACE partners, and observe these trends:

- 1. Linux has become the dominant operating system used at 80% of all sites.

- 2. The majority of the tools for system management, data management, monitoring, and resource management are either open-source software of vendor-optimized variants, often based on open-source software.

- 3. Scalability issues are known for several mission-critical components, including system administration tools, MPI libraries, parallel file systems, and scheduling algorithms for heterogeneous resource management, that require R&D to prepare these components for exascale.

- 4. Energy management has yet to be introduced to the HPC community that still focuses on raw performance.

We note that much of the system software infrastructure is open-source software, which we suggest to embrace as a powerful means towards developing a common set of tools for exascale machines.

2

#### 1 Introduction

Supercomputing is an essential part of our daily life, ranging from large-scale computations such as weather forecasting to information retrieval via search engines. Today, the PRACE partners operate two petascale supercomputers with the goal to harness and develop the potential of computational science in Europe. Petascale machines offer a peak performance in excess of  $10^{15}$  operations per second. While such machines serve scientists today, the next frontier, exascale machines with  $10^{18}$  operations per second, shall be reached within the decade.

In this first of two reports on multi-peta to exascale software, we offer the perspective of the PRACE partners on the current state of the art in European petascale computing. Since the end of frequency scaling in 2005, the quest for exascale machines has hit the so-called power wall. Microprocessor speed has topped out at clock frequencies around 2-4 GHz, because dissipating heat beyond about 100 W per chip is not economically viable. Petascale supercomputers are assembled from hundreds of thousands of microprocessors, and consume up to 10 MW of electricity, enough to power thousands of homes. Simply increasing the number of microprocessors to hundreds of millions for an exascale machine would require on the order of 10 GW of electricity, requiring at least one dedicated a power plant. For comparison, such a machine would consume almost one per mille of the world's total energy consumption.

Since alternative low-power technologies to integrated circuits on silicon are not in sight, computer engineers experiment with architectural modifications to the general-purpose programmable von Neumann processor. It is widely known that special-purpose VLSI circuits, for example to compute Fourier transforms, deliver a performance-power ratio roughly three orders of magnitude higher than a software implementation executed on a general-purpose processor. The wide spectrum between special-purpose circuits and general-purpose processor hardware constitutes a broad playground for innovation, with a direct impact on design and use of exascale computers.

Over the past years, the PRACE community has evaluated and experimented with various programming languages, tools, operating environments, and computer architectures, including multicores, manycores, and accelerated hybrid architectures. Each architecture introduces different challenges to the programmer and operator. The trend towards specialized hardware also presents an opportunity to identify new computational fabrics that are particularly suited for computational science. Therefore, we have evaluated state-of-the-art systems from the perspectives of the scientist, computer engineer, and proficient parallel programmer. This report offers an account of these efforts, and an outlook of the opportunities and challenges ahead of us on the road towards exascale computing.

This report reflects the knowledge and experience of the PRACE partners. At the time of this writing, they operate a network of high-performance machines including those shown in Table 1 below. The European PRACE community faces its own challenges and opportunities, and shares many of the problems with other communities. Therefore, the discriminating reader may view the report at hand as complementing other reports on exascale efforts by the US supercomputing community [34] and the International supercomputing community [10].

| Site       | Vendor      | Туре       | Model                   | Process<br>or<br>archite<br>cture | # of nodes  | # of                 | Mem<br>per<br>core<br>(MB<br>yte) | Inter-<br>connect<br>network | Netwo<br>rk<br>topolo<br>gy | Intern<br>al IO<br>nodes | Exter<br>nal IO<br>nodes |

|------------|-------------|------------|-------------------------|-----------------------------------|-------------|----------------------|-----------------------------------|------------------------------|-----------------------------|--------------------------|--------------------------|

| BSC        | IBM         | SMP        | JS21                    | Powerp<br>c                       | 2560        | 10240                | 2048                              | Myrinet                      | Fat<br>Tree                 | N                        | Y                        |

| CEA        | BULL        | ccNUMA     | \$6010<br>\$6030        | x86_64                            | 4000        | 128000               | 2048                              | IB QDR                       | Pruned<br>Tree              | Y                        | Y                        |

| CINE<br>CA | IBM         | ccNUMA     | P575                    | Power                             | 168         | 5376                 | 4096                              | IB                           | Mesh                        | Y                        | N                        |

| CSCS       | CRAY        | ccNUMA     | XT5                     | x86                               | 1844        | 22128                | 1300                              | CRAY<br>SeaStar<br>2+        | 3D<br>Torus                 | Y                        | N                        |

| EPCC       | CRAY        | ccNUMA     | XE6                     | x86_64                            | 1856        | 44544                | 1300                              | CRAY<br>Gemini               | 3D<br>Torus                 | Y                        | Y                        |

| FZJ        | IBM         | SMP        | Blue<br>Gene/P          | Power                             | 73728       | 294912               | 512                               | proprieta<br>ry              | 3D<br>Torus                 | Y                        | N                        |

| HLRS       | NEC         | ccNUMA     |                         | x86_64                            | 711         | 5688 + accelera tors | 1500                              | IB                           | Tree                        | Y                        | Y                        |

| ICHE<br>C  | SGI         | ccNUMA     | Altix<br>ICE<br>8200 EX | x86_64                            | 320         | 3840                 | 2048                              | IB DDR                       | Hyper-<br>cube              | Y                        | N                        |

| IPB        | PARAD<br>OX | ccNUMA     |                         | x86_64                            | 84          | 672                  | 1024                              | GbE                          | Star                        | N                        | N                        |

| JKU        | SGI         | ccNUMA     | Altix<br>4700           | IA64                              | 1<br>(SSI)  | 256                  | 4096                              | NUMAL<br>ink 4               | Fat<br>Tree                 | Y                        | N                        |

| KTH        | CRAY        | CCNUM<br>A | XE6                     | x86_64                            | 1516        | 36384                | 1333                              | CRAY<br>Gemini               | 3D<br>Torus                 | Y                        | N                        |

| LRZ        | SGI         | ccNUMA     | Altix<br>4700           | IA64                              | 19<br>(SSI) | 9728                 | 4096                              | NUMAL<br>ink 4               | Fat<br>Tree +<br>2D<br>mesh | N<br>(SAN)               | N<br>(SAN)               |

| STFC       | IBM         | SMP        | BlueGen<br>e/P          | x86_64                            | 1024        | 4096                 | 512                               | Proprieta<br>ry              | 3D<br>Torus                 | Y                        | N                        |

| UYBH<br>M  | НР          | ccNUMA     |                         | x86_64                            | 192         | 1004                 | 2048                              | IB                           | Fat<br>Tree                 | Y                        | Y                        |

**Table 1 Contributing PRACE sites**

The remainder of this report consists of three sections. Section 2 assesses the state-of-the-art computer architectures for high-performance computing. Section 3 covers developments in programming languages and environments. Section 4 discusses trends in system management software and tools for high-performance computing.

## **2 Computer Architectures**

#### 2.1 Hardware Implications on Software for Exascale

In this chapter, we survey the state-of-the-art of high-performance computer hardware from the software perspective, and attempt to deduce trends that affect the transition from petascale to exascale supercomputing. Our survey focuses on hardware features with a dominant impact on the feasibility and viability of scalable software systems for exascale machines.

Our analysis is based on the assessment of advantages and disadvantages of the various hardware platforms with respect to the following criteria:

- 1. **Scalability**: Multicore and manycore chips raise the issue of scalability within a chip to the same level of concern as scalability across chips. The central issue from the programmer's perspective is the scalability of hybrid programming models for systems of multicores and accelerated architectures, as are details such as architectural support for high-level parallel programming languages and efficient communication.

- 2. **Performance:** Besides the traditional peak Flop/s or Linpack sustained Flop/s measure, today's supercomputers may be characterized by means of various complementary performance measures, including Flop/\$s, Flop/Ws, efficiency relative to peak, etc.

- 3. **Productivity:** We are concerned about programmability in terms of availability of programming languages, operating systems, tools, as well as comparing the effort required to obtain correct and efficient programs.

- 4. **Sustainability:** Since supercomputing is a tiny market segment, the affinity of hardware products to the mass market is important to assemble affordable machines from COTS parts, and to ensure competitive upgrades depending on the refresh rate of vendors' offers.

- 5. **Portability:** Scalable software must be portable across the parts of a large machine, even if different parts are operated at different levels of upgrades. Ideally, runtime systems automate aspects like process placement and load balancing, so that portable programs can be oblivious to the number processors, the network topology, and memory hierarchy.

- 6. **Availability:** Large-scale machines require adequate manufacturing volumes; supply should match the demand during the construction period with associated cost constraints.

- 7. **Resilience:** Large-scale machines require fault-tolerance provisions to increase the uptime (MTBF). For example, at the hardware level, ECC protected memories, including caches and hard disks are effective. At the software level, increasing attention is paid to tolerating correctness and efficiency bugs.

Based on the expertise of the PRACE partners, we compile a survey of state-of-the-art hardware in Section 2.2. In Section 2.3, we summarize the trends from the perspective of scalable software systems. Furthermore, we shed some light on complementary research topics pursued with the WP9 prototype projects. In Section 2.4, we provide a watch list of topics that we recommend to be monitored throughout the upcoming year in preparation of PRACE deliverable D9.2.2 "Second Report on Multi-Peta- to Exascale Software" at project month 22.

Disclaimer: Our survey of compute hardware is by no means complete. We have included those systems in Section 2.2 that are available to the PRACE partners, and the partners have gathered sufficient experience as of March 2011 to suggest that this hardware offers a promising contribution towards an exascale system.

# 2.2 Promising Hardware Technologies for Exascale HPC

#### 2.2.1 Intel SandyBridge

Intel's SandyBridge architecture exemplifies of the evolution of mainstream multicore microprocessor architecture. Integrated on-chip is a special-purpose video processing engine that will be programmable with OpenCL (windows only today).

| Intel Sandy Pros   |                                                                                                                                                                                                                                                                                                                  | Cons                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bridge             |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Scalability        | Intel Sandy Bridge is re-designed version of the Nehalem architecture, so we expect similar on-chip scalability. A 16 core version of the chip is expected. Better power management should allow for denser packaging.                                                                                           | No plans for 8+ socket configuration in the next 2 years. Server chip will not have GPU cores.                                                                                                                                                                                                                                                    |  |  |  |

| Performance        | Additional set of instructions (AVX) and changes in the architecture (physical register file, Out-of-order cluster, execution cluster and memory cluster) should result in reducing the gap between real life and theoretical performance. Tests and benchmarking will be performed after the hardware shipment. | The integrated GPU cores are programmable yet no experiments are known as of now; therefore it may be difficult to use them for calculations (especially with the server version which lacks of the GPU part). No plans for releasing math libraries using the GPU cores. The theoretical peak performance stays at the same level as in Nehalem. |  |  |  |

| Productivity       | No special languages required, all binaries should work more efficient without any changes.                                                                                                                                                                                                                      | Using AVX requires either new libraries or rewriting part of the codes. Currently there is no simple way to use the GPU cores for calculations.                                                                                                                                                                                                   |  |  |  |

| Sustainabilit<br>y | Sandy Bridge and its shrunken version<br>Ivy Bridge will form the backbone of the<br>Intel offer in the next 2 years                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Portability        | All standard compilers with support for x86 will work.                                                                                                                                                                                                                                                           | AVX instruction set must be supported by the compiler. AVX is not backwards compatible                                                                                                                                                                                                                                                            |  |  |  |

| Availability       | Desktop and mobile versions will are already available. Server 2P configurations will be available 4Q 2011.                                                                                                                                                                                                      | 4P servers will not be available during PRACE-1IP.                                                                                                                                                                                                                                                                                                |  |  |  |

| Resilience         | Server version will support ECC memory                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

Table 2 INTEL Sandy Bridge pros and cons

The Sandy Bridge architecture is an evolutionary step towards better performance and lower power consumption compared to its predecessor Nehalem. Some interesting changes in the architecture resulted in reduced power consumption and increased performance. Intel promotes x86 as a general platform that should cover all possible markets. GPU cores introduced in some of the models have decent performance but since the cores have fixed functionality it may be difficult if not impossible to use them for HPC. In contrast to AMD, who strongly supports accelerated processing units, Intel is more conservative improving the performance with a traditional multicore architecture, new engineering solutions, and adding new instructions.

#### 2.2.2 *IBM Power 7*

Released in 2010, it is a RISC processor in 45nm technology. The chip contains 4, 6, or 8 cores, each 4-way SMT-capable, operating at a frequency of 3.0 GHz to 4.25 GHz. As established in the tradition of Power, the SIMD unit (AltiVec) plays a limited role (with respect to the Intel CPUs), but to exploit the power is necessary to use all four FPUs and the Fused Multiply-Add instruction. The chip contains three levels of cache, the first two, 64 kB L1 and 256 kB L2, are private to the core and the 32 MB L3 is shared (but it may be set with core-private partitions).

| IBM Power7     | Pros                                                                                                                                                                | Cons                                                                                                                                                                                                                                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scalability    | Up to 256 cores, and 1024 threads.                                                                                                                                  | SMT not very efficient, at least under Linux OS. Comparisons made in similar conditions (applications and number of physical cores) show that using SMT either with MPI or OpenMP do not bring better results (compared to SMT turned off). This is in contrast with Power6 processors. |

| Performance    | Peak performance of 8-core<br>Power7 is 265 GFlop/s at 4GHz,<br>or 1.25 GFlop/Ws.                                                                                   | Programming for high-performance requires keeping the 4 FPUs busy, and carefully using the cache.                                                                                                                                                                                       |

| Productivity   | Linux based system: established tools are available.                                                                                                                | GNU compilers and tools suite do not support Power7 extensions yet.                                                                                                                                                                                                                     |

| Sustainability | IBM Power processors are on the HPC market since the early 1990s.                                                                                                   | -                                                                                                                                                                                                                                                                                       |

| Portability    | Good for Linux based system. In fact no main problems are expected in porting application from other Linux based HPC systems like BG/P, BG/Q, Cray, Linux clusters. | Problem may arise for the IBM XL compiler suite, due to the limited support for C++ recently introduced standard feature (e.g. Boost library does not compile)                                                                                                                          |

| Availability   | Good. Product line includes workstations, blade systems and supercomputers.                                                                                         | -                                                                                                                                                                                                                                                                                       |

| Resilience     | High. Power7 is designed to support PERCS (Productive, Easy-to-use, Reliable Computer System) project in US, so                                                     | -                                                                                                                                                                                                                                                                                       |

| IBM Power7 | Pros                           | Cons |

|------------|--------------------------------|------|

|            | resilience has been taken into |      |

|            | account by design.             |      |

Table 3 IBM Power 7 pros and cons

The architectural characteristic of Power7 promotes the use of hybrid MPI and OpenMP programming model and cache blocked algorithms.

#### 2.2.3 IBM BG/Q

The Blue Gene Q (BG/Q) architecture represents a supercomputer architecture that focuses on maximizing the Flop/Ws ratio. Although Blue Gene belongs to the class of general-purpose computers, it is a niche product for supercomputing that has not penetrated the mass market.

| IBM BG/Q       | Pros                                                                                                                                                                                                                                                       | Cons                                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scalability    | System is designed to be extremely scalable up to more than 2M cores. Improved communication network (5-D topology), compared to BG/P                                                                                                                      | No full (non blocking) fat tree network topology                                                                                                                                                                    |

| Performance    | Very high MF/W ratio target (>2500) (leading Green500 list). System with 20 PFlop/s will be installed at LLNL                                                                                                                                              | Only a first, less efficient prototype system is listed in the Green500                                                                                                                                             |

| Productivity   | Standard MPI, OpenMP programming environment with optimized compilers for standard C/C++ and Fortran available. No hardware specific adaption necessary, compatible to BG/P                                                                                | System is only really suitable for high scaling applications with more than 16k tasks/threads, nevertheless minimal job size can be 256 tasks/threads without wasting resources. Limited amount of memory per core. |

| Sustainability | 3 <sup>rd</sup> version in Blue Gene series (not COTS but still sustained)                                                                                                                                                                                 | -                                                                                                                                                                                                                   |

| Portability    | Very high, no special, hardware specific programming model/language required                                                                                                                                                                               | Pure MPI applications might no longer suitable to utilize full performance capability of (this/all) many core architectures. Hybrid programming models might be necessary                                           |

| Availability   | Planned to be generally available in 4Q/2011                                                                                                                                                                                                               | Hardware more expensive than x86 solution, but much more power efficient => TCO might be comparable.                                                                                                                |

| Resilience     | Proven high resilience features from BG/P improved like full system hardware counter collection and real time analyses for pre-emptive hardware replacement strategy (HW will be replaced when recoverable error counters go up before hard errors occure) | -                                                                                                                                                                                                                   |

| T-1-1 4 IDM D  | C/O pros and cons                                                                                                                                                                                                                                          |                                                                                                                                                                                                                     |

Table 4 IBM BG/Q pros and cons

Upgraded features of BG/Q compared to predecessor BG/P:

- 4x increased number of cores per node: 16 (+1)

- 2x clock speed: 1.6 Ghz

- 64-bit architecture

- 2x SIMD width: 4-wide double-precision SIMD unit

- 4-way SMT allows up to 64 (MPI) threads per node